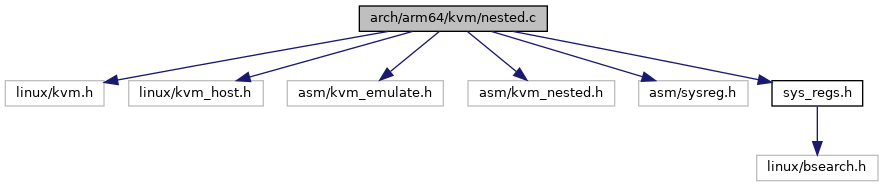

#include <linux/kvm.h>

#include <linux/kvm_host.h>

#include <asm/kvm_emulate.h>

#include <asm/kvm_nested.h>

#include <asm/sysreg.h>

#include "sys_regs.h"

Go to the source code of this file.

|

| #define | NV_FTR(r, f) ID_AA64##r##_EL1_##f |

| |

◆ NV_FTR

| #define NV_FTR |

( |

|

r, |

|

|

|

f |

|

) |

| ID_AA64##r##_EL1_##f |

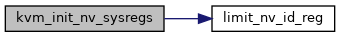

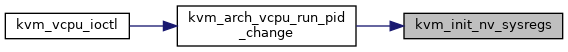

◆ kvm_init_nv_sysregs()

| int kvm_init_nv_sysregs |

( |

struct kvm * |

kvm | ) |

|

Definition at line 159 of file nested.c.

161 mutex_lock(&kvm->arch.config_lock);

163 for (

int i = 0; i < KVM_ARM_ID_REG_NUM; i++)

165 kvm->arch.id_regs[i]);

167 mutex_unlock(&kvm->arch.config_lock);

static u64 limit_nv_id_reg(u32 id, u64 val)

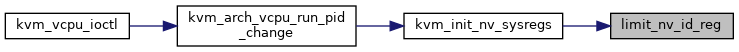

◆ limit_nv_id_reg()

| static u64 limit_nv_id_reg |

( |

u32 |

id, |

|

|

u64 |

val |

|

) |

| |

|

static |

Definition at line 26 of file nested.c.

31 case SYS_ID_AA64ISAR0_EL1:

33 val &= ~(

NV_FTR(ISAR0, TLB) |

37 case SYS_ID_AA64ISAR1_EL1:

39 val &= ~(GENMASK_ULL(63, 56) |

47 case SYS_ID_AA64PFR0_EL1:

49 val &= ~(GENMASK_ULL(55, 52) |

59 val |= FIELD_PREP(

NV_FTR(PFR0, EL1), 0b0001);

60 val |= FIELD_PREP(

NV_FTR(PFR0, EL2), 0b0001);

61 val |= FIELD_PREP(

NV_FTR(PFR0, EL3), 0b0001);

64 case SYS_ID_AA64PFR1_EL1:

69 case SYS_ID_AA64MMFR0_EL1:

71 val &= ~(

NV_FTR(MMFR0, ECV) |

81 val |= FIELD_PREP(

NV_FTR(MMFR0, TGRAN16_2), 0b0001);

84 val |= FIELD_PREP(

NV_FTR(MMFR0, TGRAN4_2), 0b0001);

98 val |= FIELD_PREP(

NV_FTR(MMFR0, TGRAN4_2), 0b0010);

101 val |= FIELD_PREP(

NV_FTR(MMFR0, TGRAN16_2), 0b0010);

104 val |= FIELD_PREP(

NV_FTR(MMFR0, TGRAN64_2), 0b0010);

108 tmp = FIELD_GET(

NV_FTR(MMFR0, PARANGE), val);

110 val &= ~

NV_FTR(MMFR0, PARANGE);

111 val |= FIELD_PREP(

NV_FTR(MMFR0, PARANGE), 0b0101);

115 case SYS_ID_AA64MMFR1_EL1:

116 val &= (

NV_FTR(MMFR1, HCX) |

124 case SYS_ID_AA64MMFR2_EL1:

125 val &= ~(

NV_FTR(MMFR2, BBM) |

127 GENMASK_ULL(47, 44) |

133 val |= FIELD_PREP(

NV_FTR(MMFR2, TTL), 0b0001);

136 case SYS_ID_AA64DFR0_EL1:

138 val &= (

NV_FTR(DFR0, PMUVer) |

144 tmp = FIELD_GET(

NV_FTR(DFR0, DebugVer), val);

146 val &= ~

NV_FTR(DFR0, DebugVer);

147 val |= FIELD_PREP(

NV_FTR(DFR0, DebugVer), 0b0111);