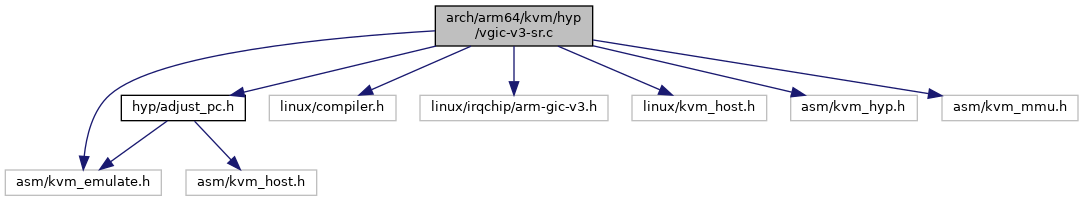

#include <hyp/adjust_pc.h>#include <linux/compiler.h>#include <linux/irqchip/arm-gic-v3.h>#include <linux/kvm_host.h>#include <asm/kvm_emulate.h>#include <asm/kvm_hyp.h>#include <asm/kvm_mmu.h>

Go to the source code of this file.

Macros | |

| #define | vtr_to_max_lr_idx(v) ((v) & 0xf) |

| #define | vtr_to_nr_pre_bits(v) ((((u32)(v) >> 26) & 7) + 1) |

| #define | vtr_to_nr_apr_regs(v) (1 << (vtr_to_nr_pre_bits(v) - 5)) |

| #define | GICv3_IDLE_PRIORITY 0xff |

Functions | |

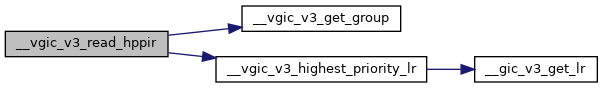

| static u64 | __gic_v3_get_lr (unsigned int lr) |

| static void | __gic_v3_set_lr (u64 val, int lr) |

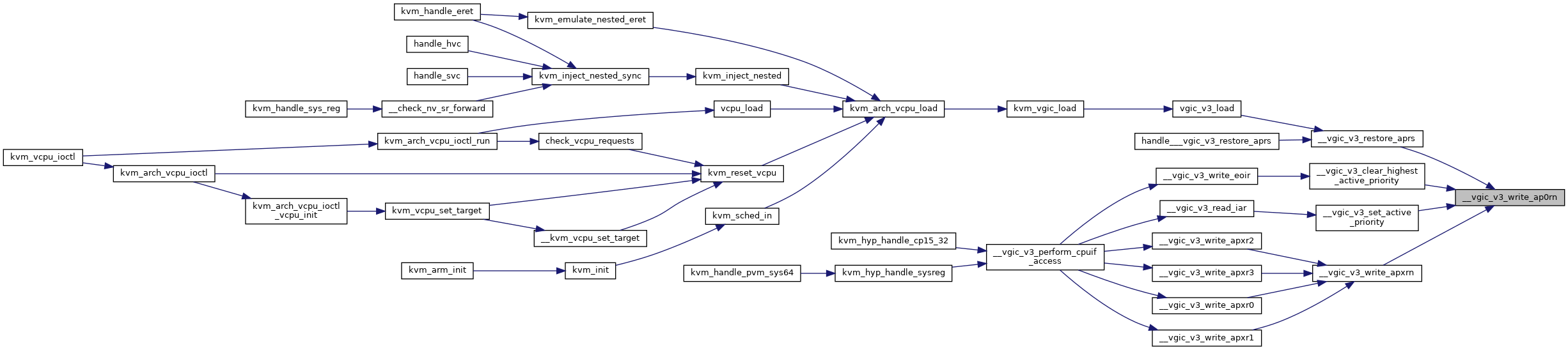

| static void | __vgic_v3_write_ap0rn (u32 val, int n) |

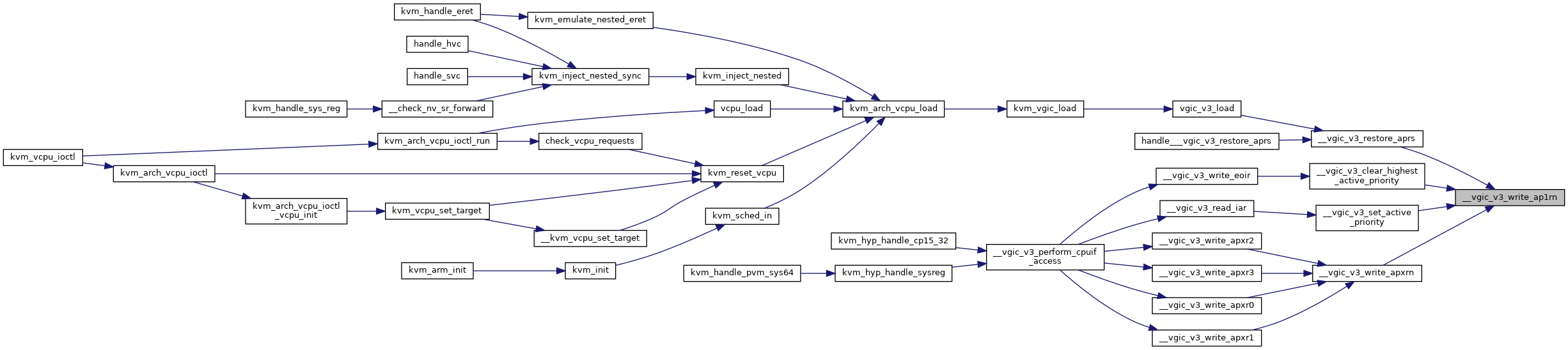

| static void | __vgic_v3_write_ap1rn (u32 val, int n) |

| static u32 | __vgic_v3_read_ap0rn (int n) |

| static u32 | __vgic_v3_read_ap1rn (int n) |

| void | __vgic_v3_save_state (struct vgic_v3_cpu_if *cpu_if) |

| void | __vgic_v3_restore_state (struct vgic_v3_cpu_if *cpu_if) |

| void | __vgic_v3_activate_traps (struct vgic_v3_cpu_if *cpu_if) |

| void | __vgic_v3_deactivate_traps (struct vgic_v3_cpu_if *cpu_if) |

| void | __vgic_v3_save_aprs (struct vgic_v3_cpu_if *cpu_if) |

| void | __vgic_v3_restore_aprs (struct vgic_v3_cpu_if *cpu_if) |

| void | __vgic_v3_init_lrs (void) |

| u64 | __vgic_v3_get_gic_config (void) |

| u64 | __vgic_v3_read_vmcr (void) |

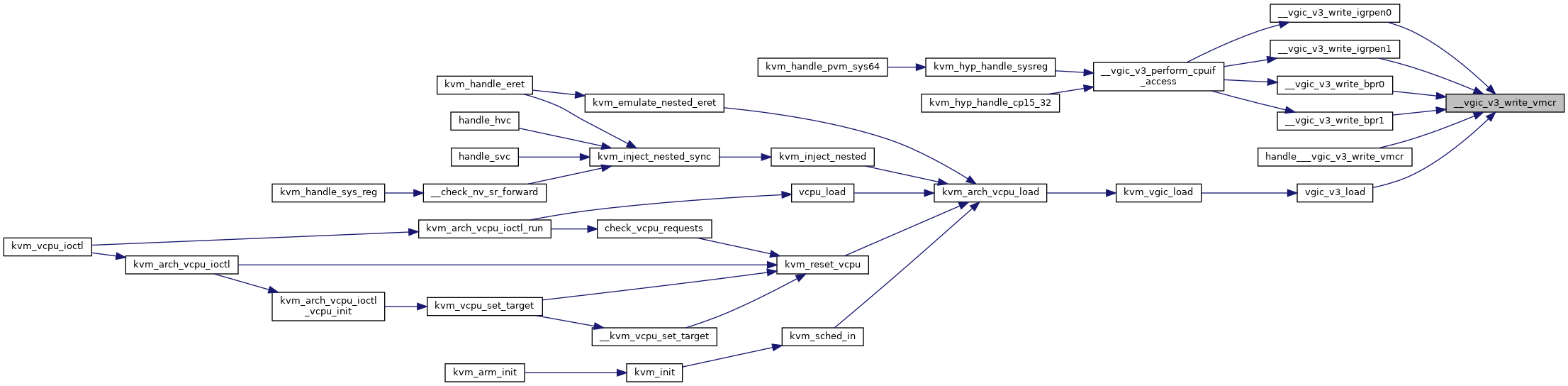

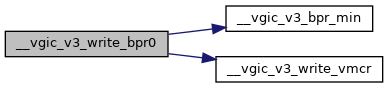

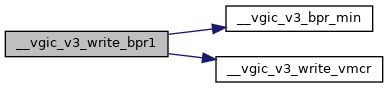

| void | __vgic_v3_write_vmcr (u32 vmcr) |

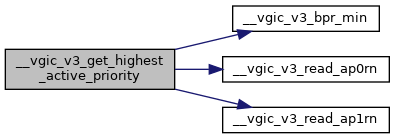

| static int | __vgic_v3_bpr_min (void) |

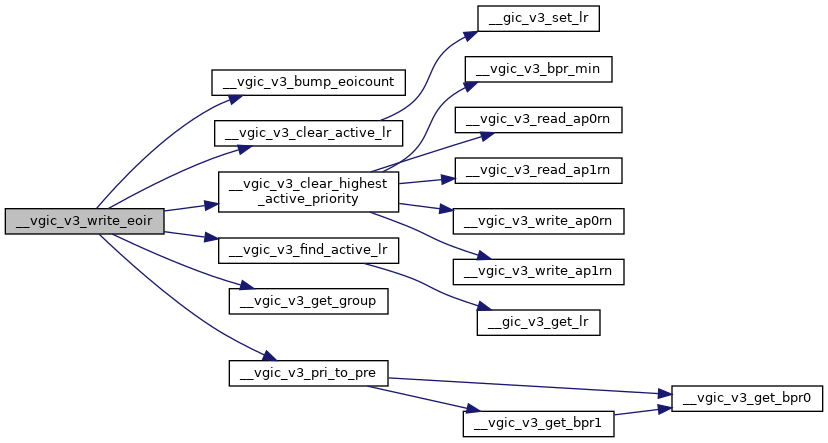

| static int | __vgic_v3_get_group (struct kvm_vcpu *vcpu) |

| static int | __vgic_v3_highest_priority_lr (struct kvm_vcpu *vcpu, u32 vmcr, u64 *lr_val) |

| static int | __vgic_v3_find_active_lr (struct kvm_vcpu *vcpu, int intid, u64 *lr_val) |

| static int | __vgic_v3_get_highest_active_priority (void) |

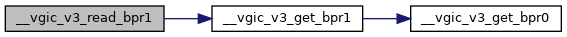

| static unsigned int | __vgic_v3_get_bpr0 (u32 vmcr) |

| static unsigned int | __vgic_v3_get_bpr1 (u32 vmcr) |

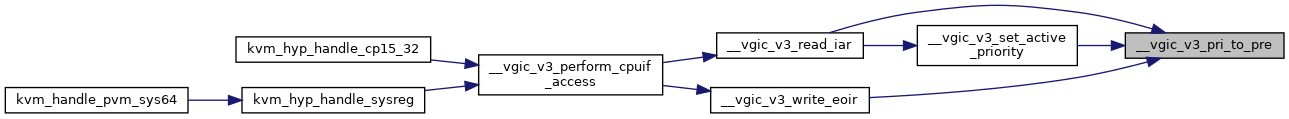

| static u8 | __vgic_v3_pri_to_pre (u8 pri, u32 vmcr, int grp) |

| static void | __vgic_v3_set_active_priority (u8 pri, u32 vmcr, int grp) |

| static int | __vgic_v3_clear_highest_active_priority (void) |

| static void | __vgic_v3_read_iar (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_clear_active_lr (int lr, u64 lr_val) |

| static void | __vgic_v3_bump_eoicount (void) |

| static void | __vgic_v3_write_dir (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_write_eoir (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_igrpen0 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_igrpen1 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_write_igrpen0 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_write_igrpen1 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_bpr0 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

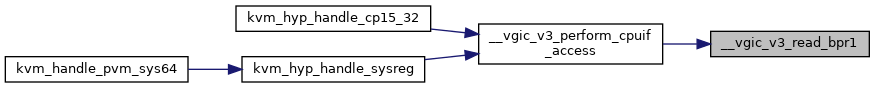

| static void | __vgic_v3_read_bpr1 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

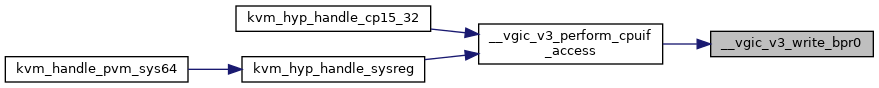

| static void | __vgic_v3_write_bpr0 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

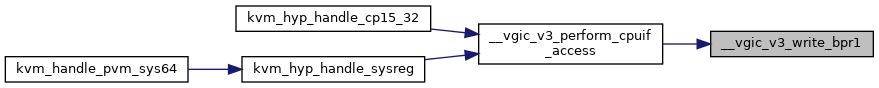

| static void | __vgic_v3_write_bpr1 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

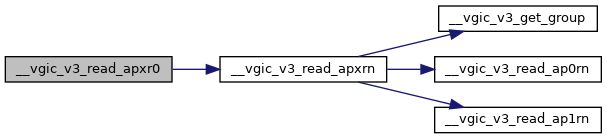

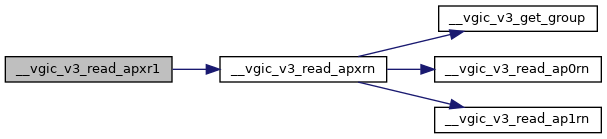

| static void | __vgic_v3_read_apxrn (struct kvm_vcpu *vcpu, int rt, int n) |

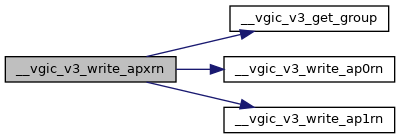

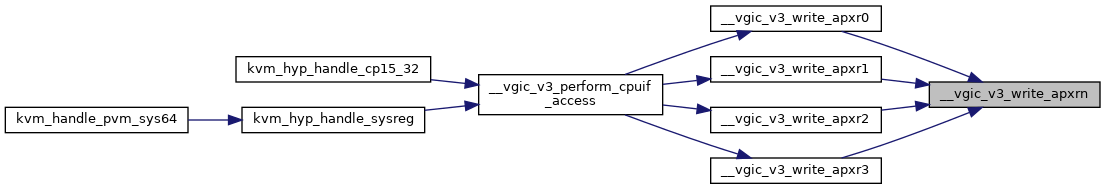

| static void | __vgic_v3_write_apxrn (struct kvm_vcpu *vcpu, int rt, int n) |

| static void | __vgic_v3_read_apxr0 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_apxr1 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_apxr2 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_apxr3 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_write_apxr0 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_write_apxr1 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

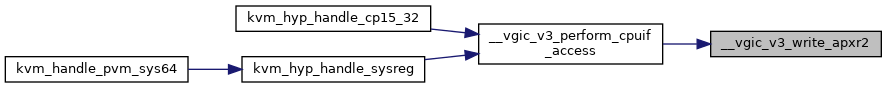

| static void | __vgic_v3_write_apxr2 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

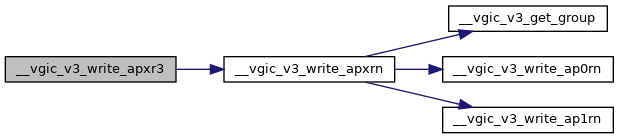

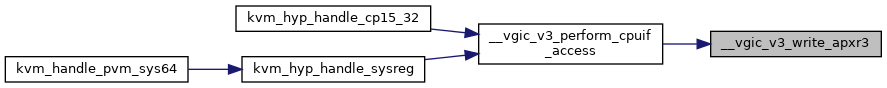

| static void | __vgic_v3_write_apxr3 (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_hppir (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_pmr (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

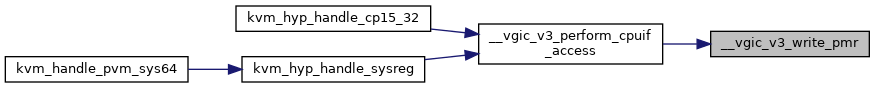

| static void | __vgic_v3_write_pmr (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| static void | __vgic_v3_read_rpr (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

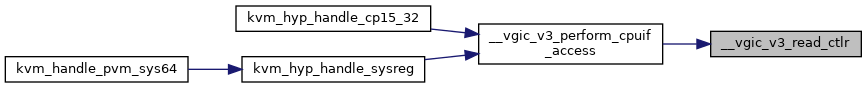

| static void | __vgic_v3_read_ctlr (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

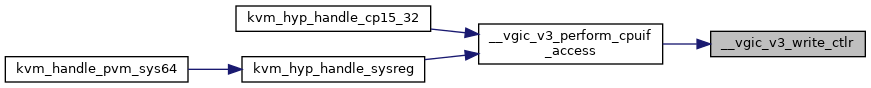

| static void | __vgic_v3_write_ctlr (struct kvm_vcpu *vcpu, u32 vmcr, int rt) |

| int | __vgic_v3_perform_cpuif_access (struct kvm_vcpu *vcpu) |

Macro Definition Documentation

◆ GICv3_IDLE_PRIORITY

| #define GICv3_IDLE_PRIORITY 0xff |

Definition at line 482 of file vgic-v3-sr.c.

◆ vtr_to_max_lr_idx

| #define vtr_to_max_lr_idx | ( | v | ) | ((v) & 0xf) |

Definition at line 17 of file vgic-v3-sr.c.

◆ vtr_to_nr_apr_regs

| #define vtr_to_nr_apr_regs | ( | v | ) | (1 << (vtr_to_nr_pre_bits(v) - 5)) |

Definition at line 19 of file vgic-v3-sr.c.

◆ vtr_to_nr_pre_bits

| #define vtr_to_nr_pre_bits | ( | v | ) | ((((u32)(v) >> 26) & 7) + 1) |

Definition at line 18 of file vgic-v3-sr.c.

Function Documentation

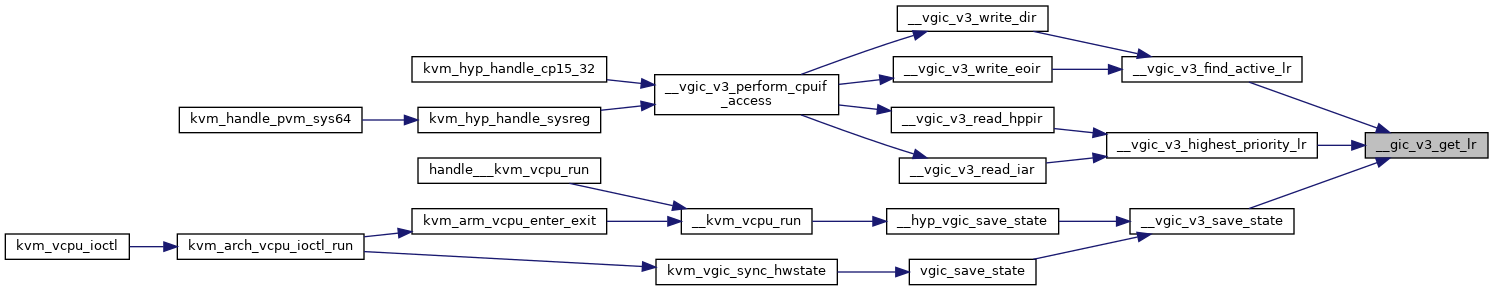

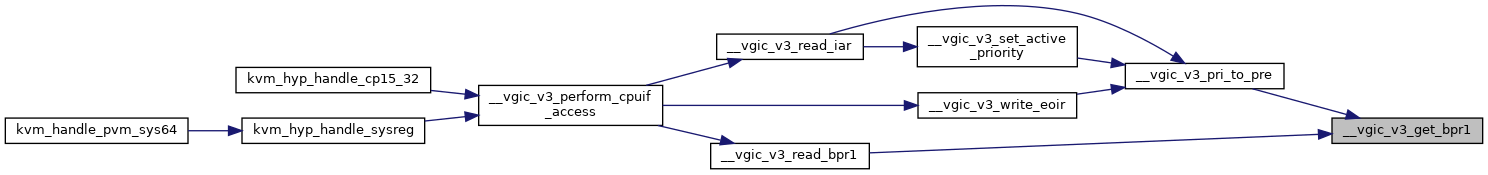

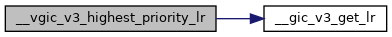

◆ __gic_v3_get_lr()

|

static |

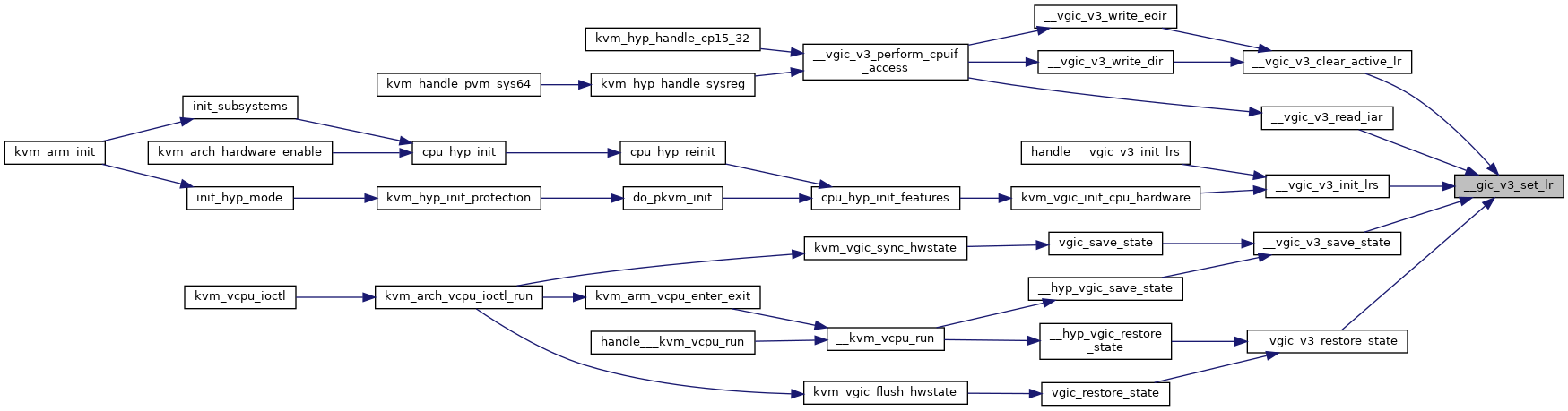

◆ __gic_v3_set_lr()

|

static |

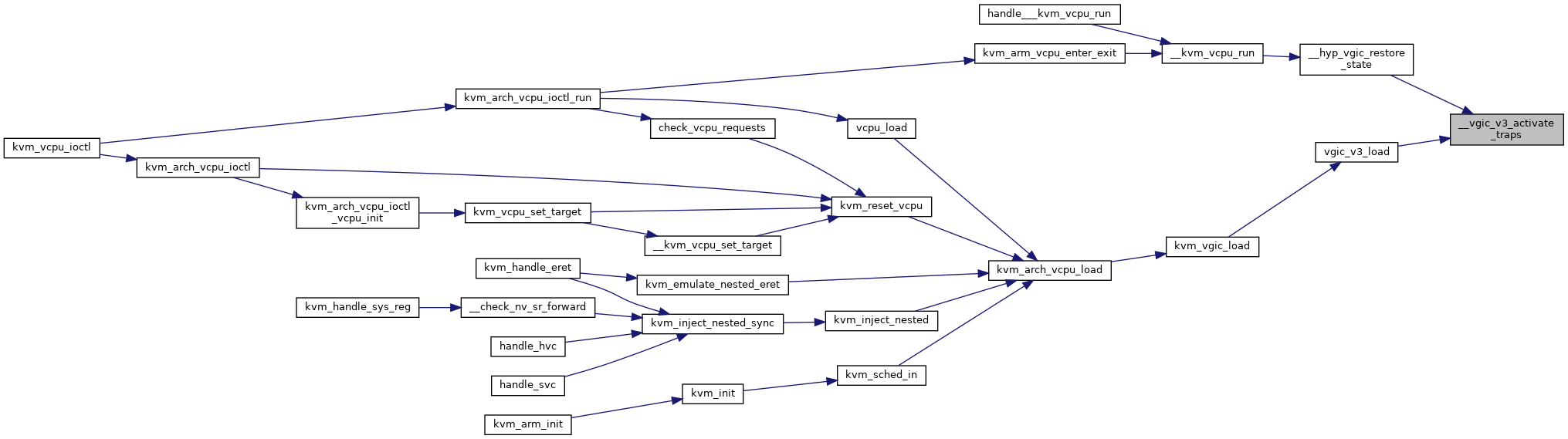

◆ __vgic_v3_activate_traps()

| void __vgic_v3_activate_traps | ( | struct vgic_v3_cpu_if * | cpu_if | ) |

Definition at line 260 of file vgic-v3-sr.c.

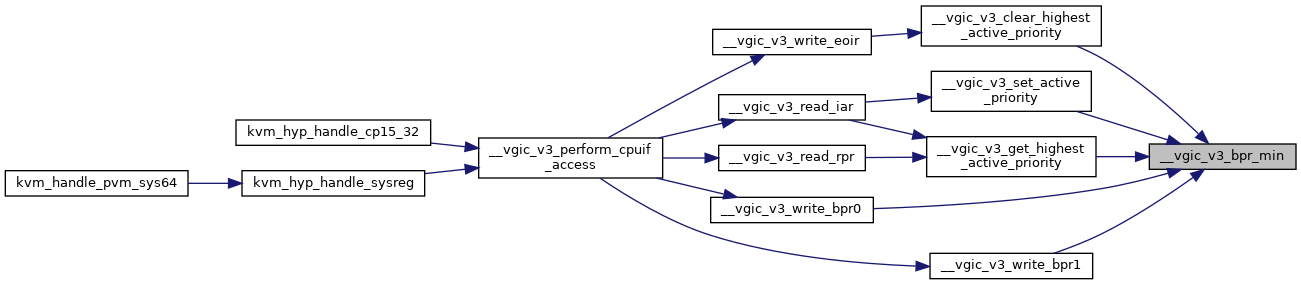

◆ __vgic_v3_bpr_min()

|

static |

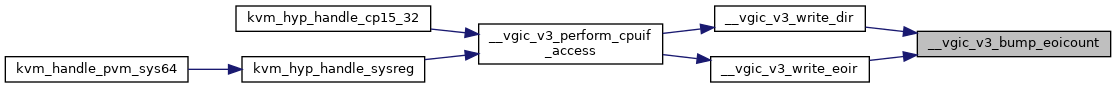

◆ __vgic_v3_bump_eoicount()

|

static |

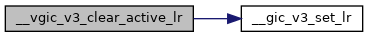

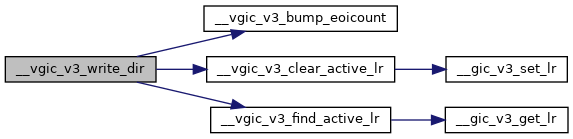

◆ __vgic_v3_clear_active_lr()

|

static |

Definition at line 708 of file vgic-v3-sr.c.

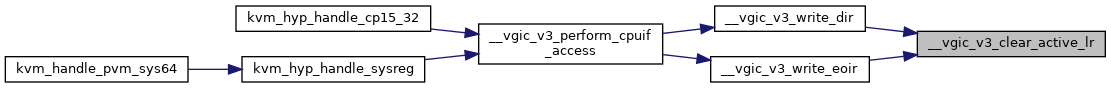

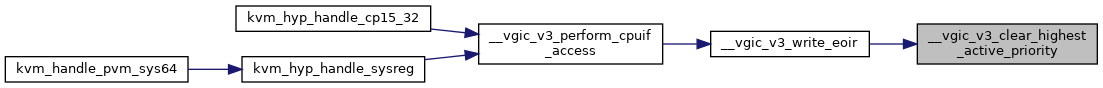

◆ __vgic_v3_clear_highest_active_priority()

|

static |

Definition at line 636 of file vgic-v3-sr.c.

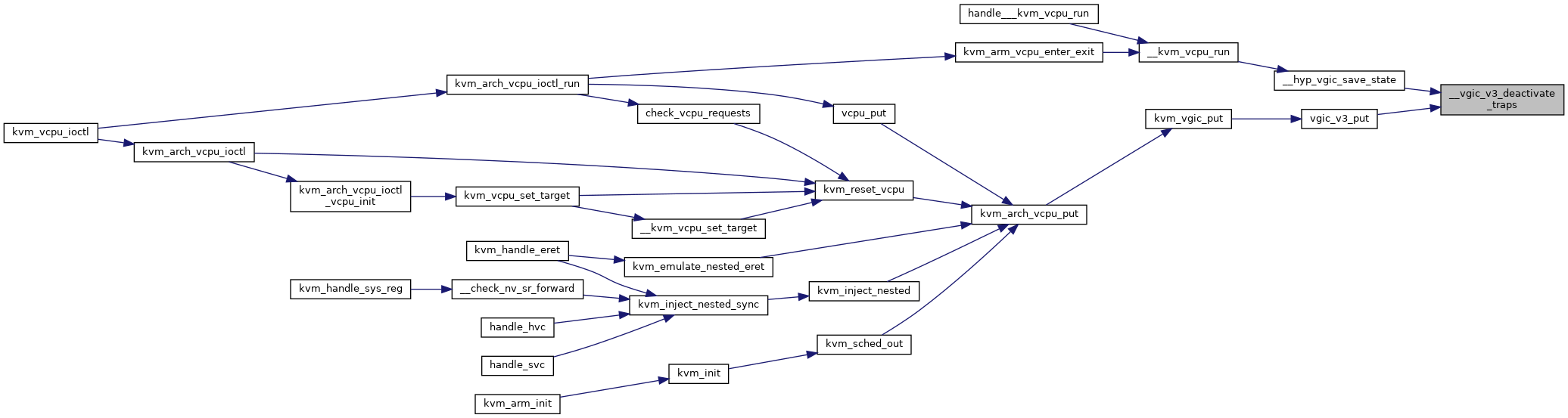

◆ __vgic_v3_deactivate_traps()

| void __vgic_v3_deactivate_traps | ( | struct vgic_v3_cpu_if * | cpu_if | ) |

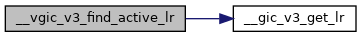

◆ __vgic_v3_find_active_lr()

|

static |

Definition at line 523 of file vgic-v3-sr.c.

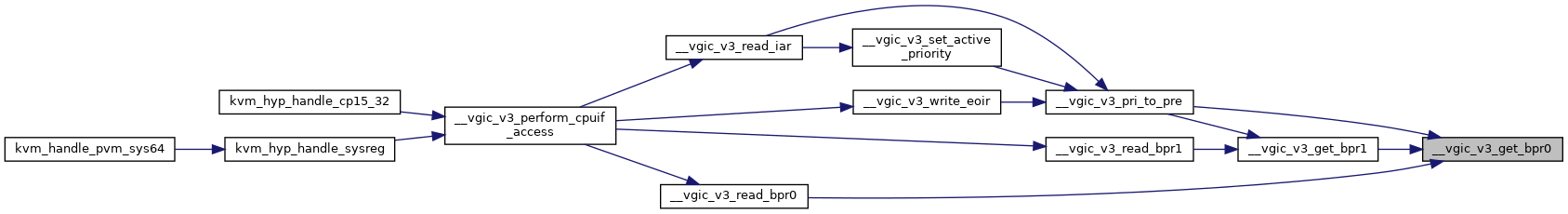

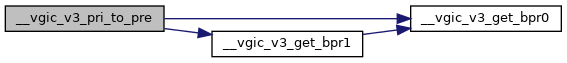

◆ __vgic_v3_get_bpr0()

|

static |

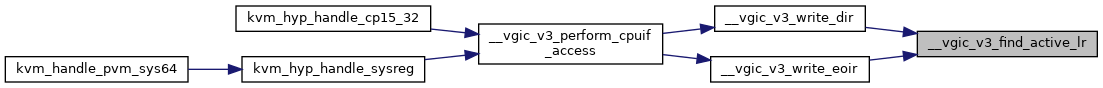

◆ __vgic_v3_get_bpr1()

|

static |

Definition at line 580 of file vgic-v3-sr.c.

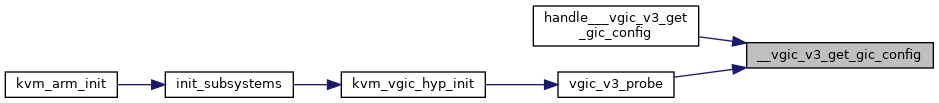

◆ __vgic_v3_get_gic_config()

| u64 __vgic_v3_get_gic_config | ( | void | ) |

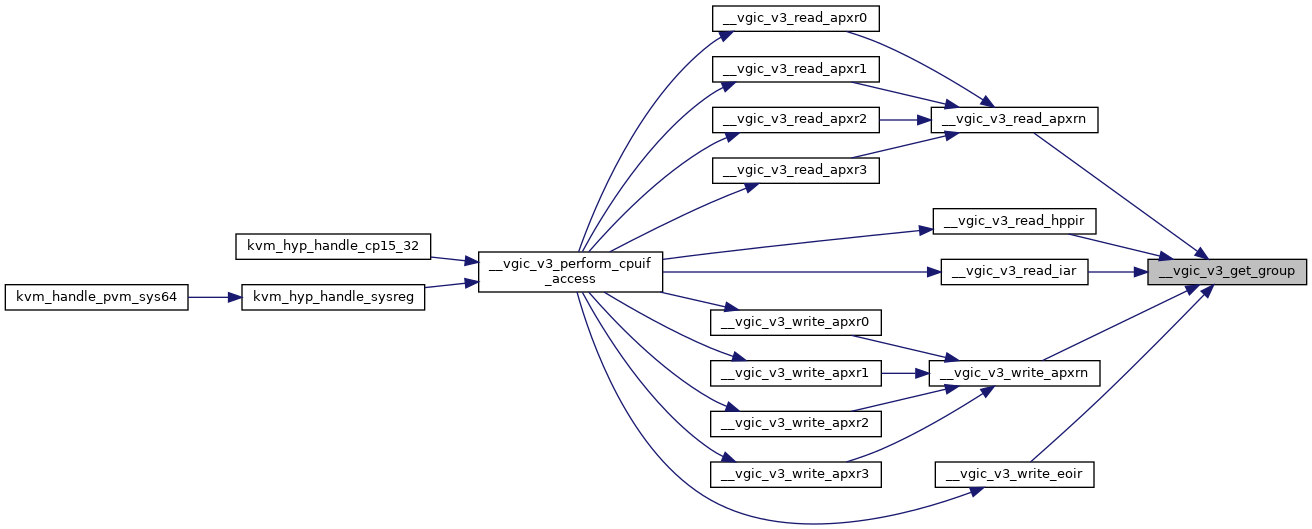

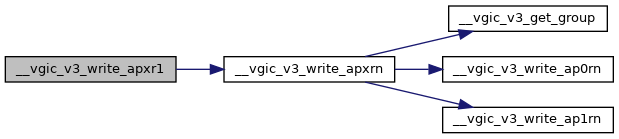

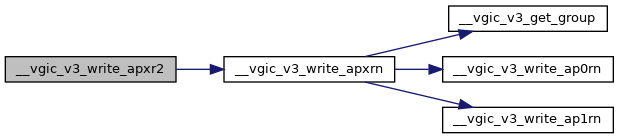

◆ __vgic_v3_get_group()

|

static |

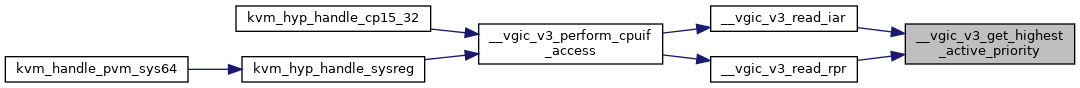

◆ __vgic_v3_get_highest_active_priority()

|

static |

Definition at line 543 of file vgic-v3-sr.c.

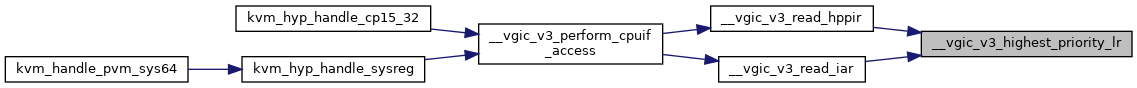

◆ __vgic_v3_highest_priority_lr()

|

static |

Definition at line 484 of file vgic-v3-sr.c.

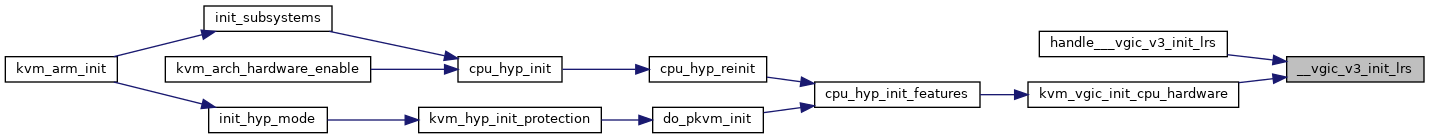

◆ __vgic_v3_init_lrs()

| void __vgic_v3_init_lrs | ( | void | ) |

Definition at line 399 of file vgic-v3-sr.c.

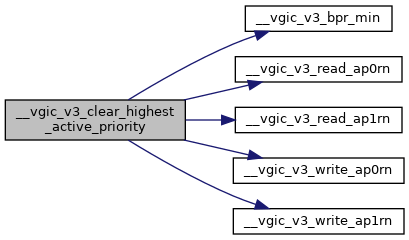

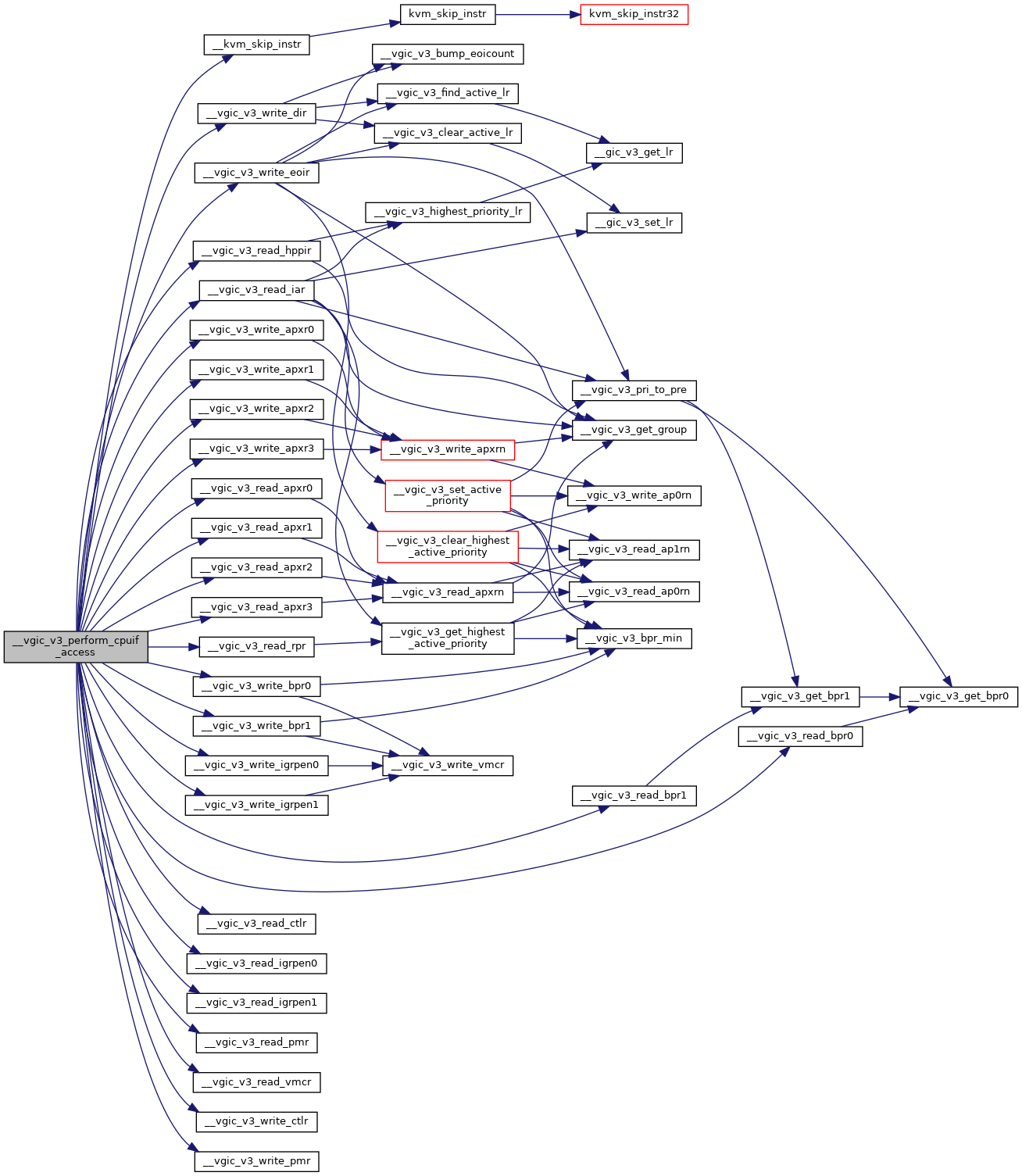

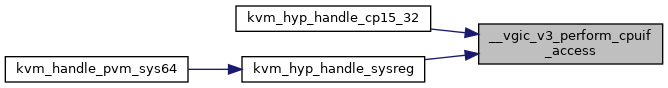

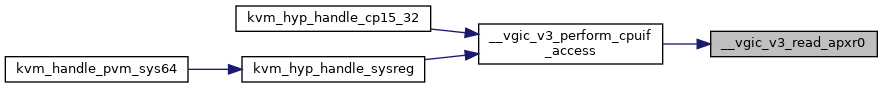

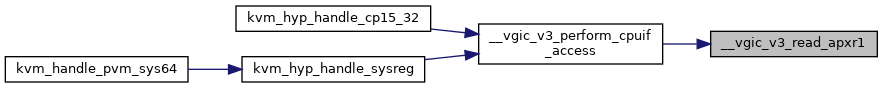

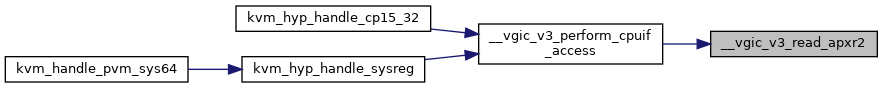

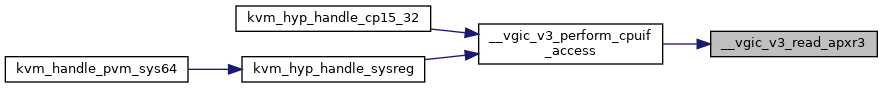

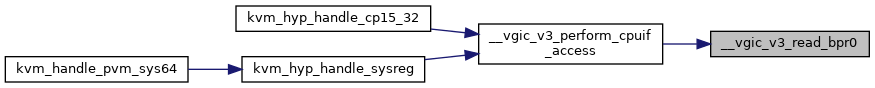

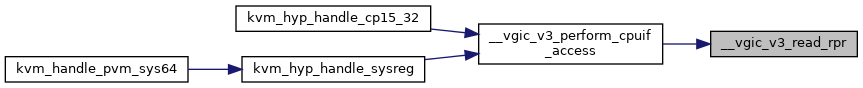

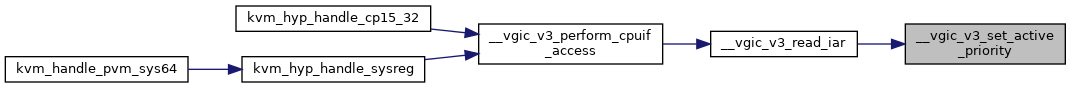

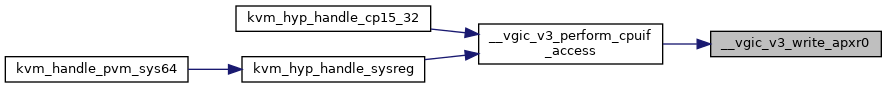

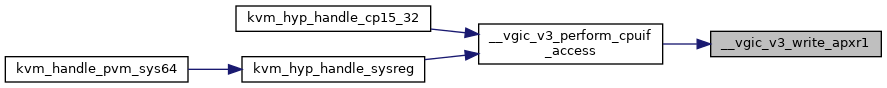

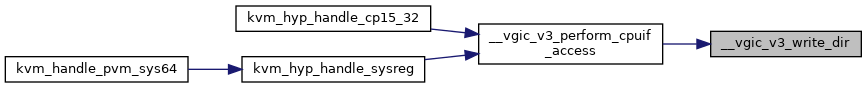

◆ __vgic_v3_perform_cpuif_access()

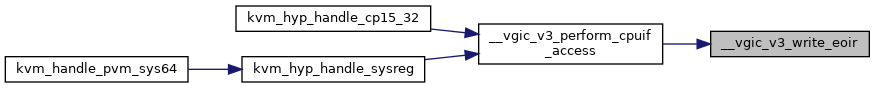

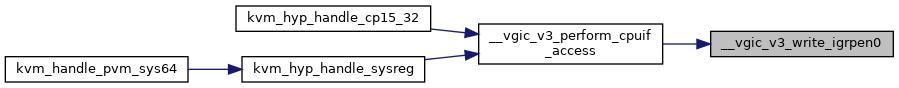

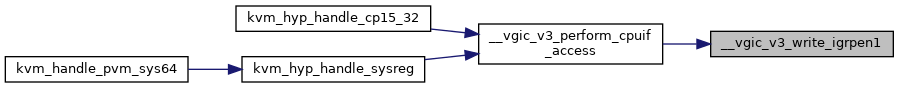

| int __vgic_v3_perform_cpuif_access | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 1016 of file vgic-v3-sr.c.

◆ __vgic_v3_pri_to_pre()

|

static |

Definition at line 599 of file vgic-v3-sr.c.

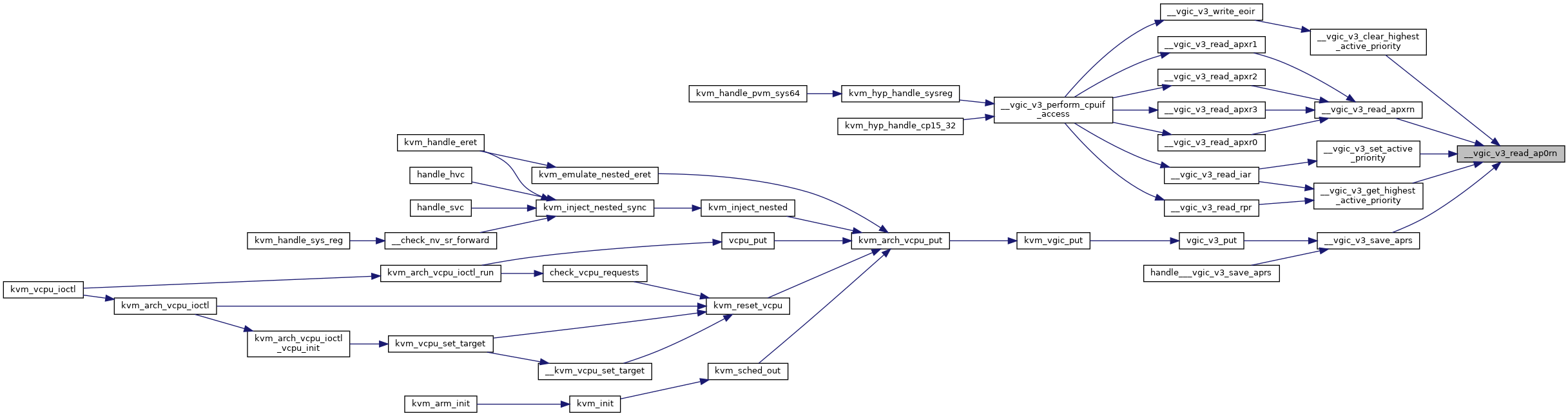

◆ __vgic_v3_read_ap0rn()

|

static |

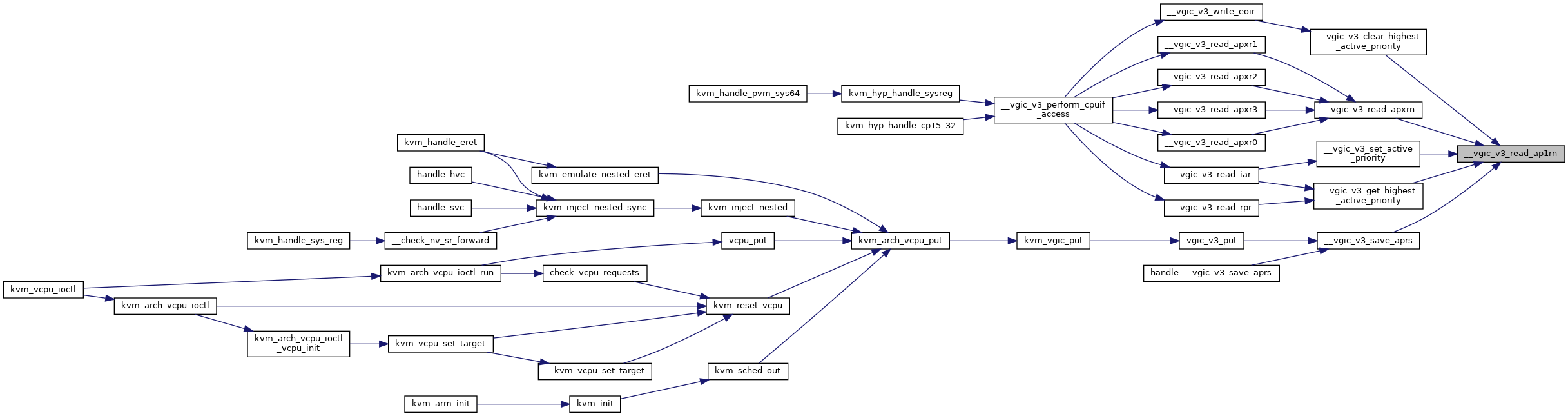

◆ __vgic_v3_read_ap1rn()

|

static |

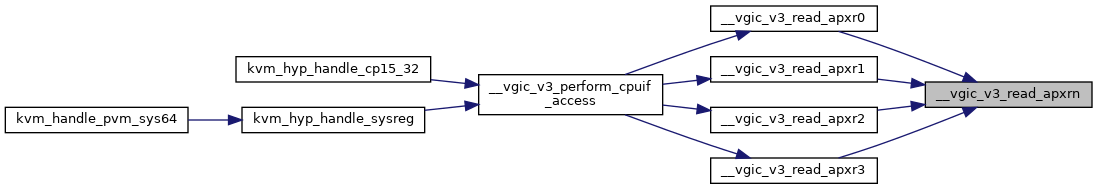

◆ __vgic_v3_read_apxr0()

|

static |

Definition at line 891 of file vgic-v3-sr.c.

◆ __vgic_v3_read_apxr1()

|

static |

Definition at line 897 of file vgic-v3-sr.c.

◆ __vgic_v3_read_apxr2()

|

static |

Definition at line 903 of file vgic-v3-sr.c.

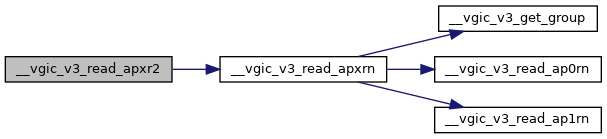

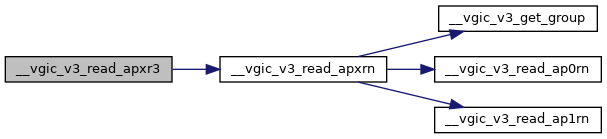

◆ __vgic_v3_read_apxr3()

|

static |

Definition at line 908 of file vgic-v3-sr.c.

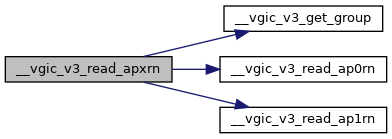

◆ __vgic_v3_read_apxrn()

|

static |

Definition at line 869 of file vgic-v3-sr.c.

◆ __vgic_v3_read_bpr0()

|

static |

Definition at line 822 of file vgic-v3-sr.c.

◆ __vgic_v3_read_bpr1()

|

static |

Definition at line 827 of file vgic-v3-sr.c.

◆ __vgic_v3_read_ctlr()

|

static |

Definition at line 977 of file vgic-v3-sr.c.

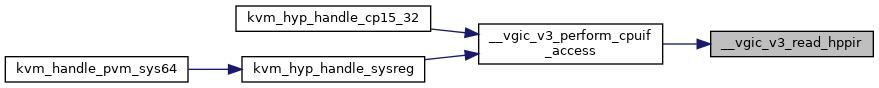

◆ __vgic_v3_read_hppir()

|

static |

Definition at line 933 of file vgic-v3-sr.c.

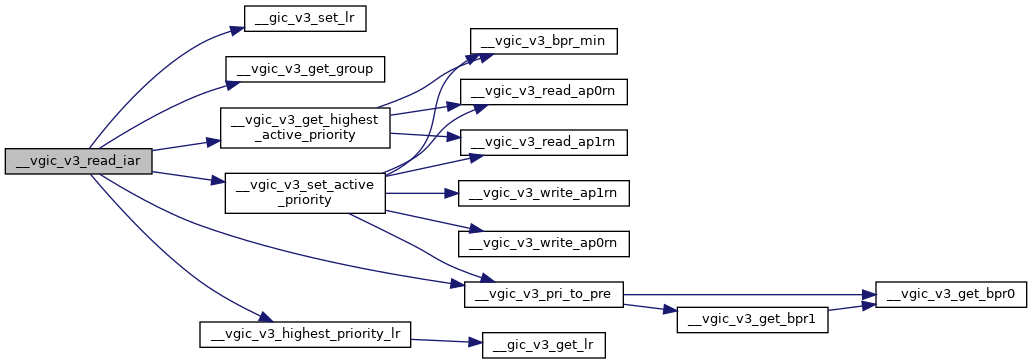

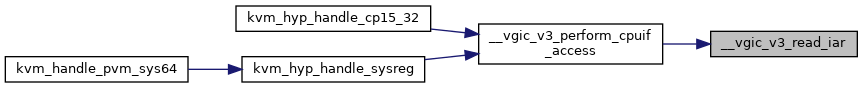

◆ __vgic_v3_read_iar()

|

static |

Definition at line 674 of file vgic-v3-sr.c.

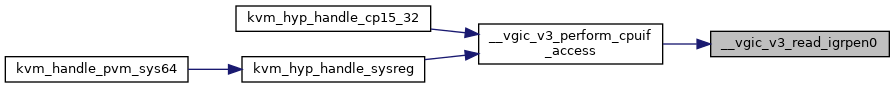

◆ __vgic_v3_read_igrpen0()

|

static |

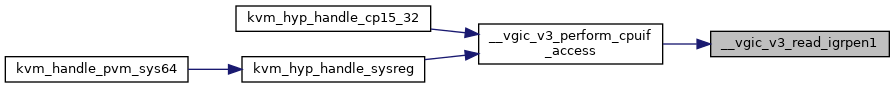

◆ __vgic_v3_read_igrpen1()

|

static |

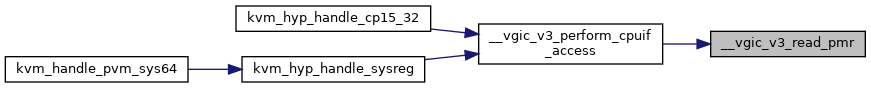

◆ __vgic_v3_read_pmr()

|

static |

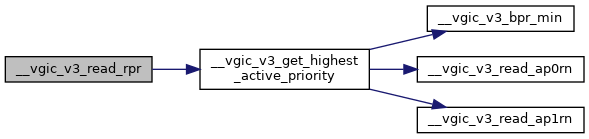

◆ __vgic_v3_read_rpr()

|

static |

Definition at line 971 of file vgic-v3-sr.c.

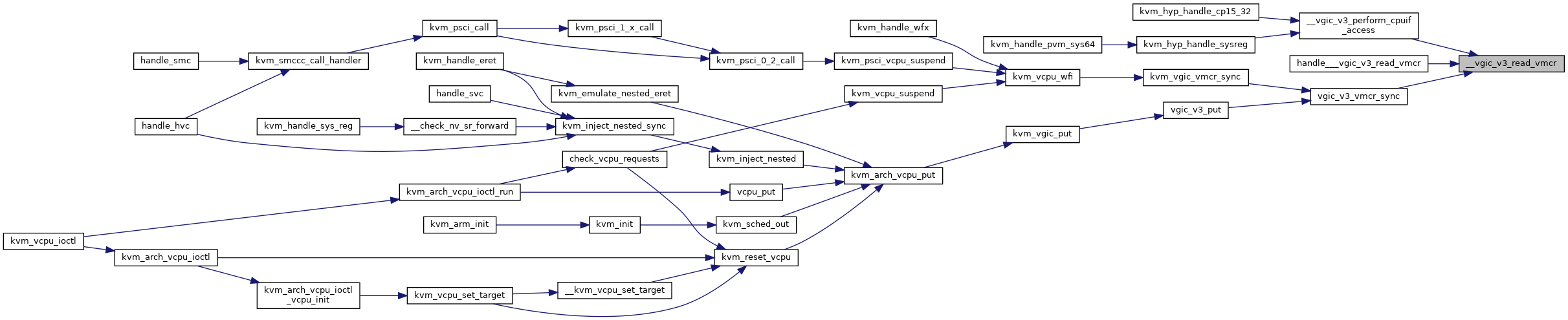

◆ __vgic_v3_read_vmcr()

| u64 __vgic_v3_read_vmcr | ( | void | ) |

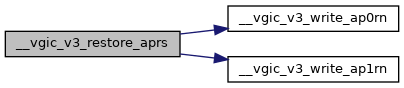

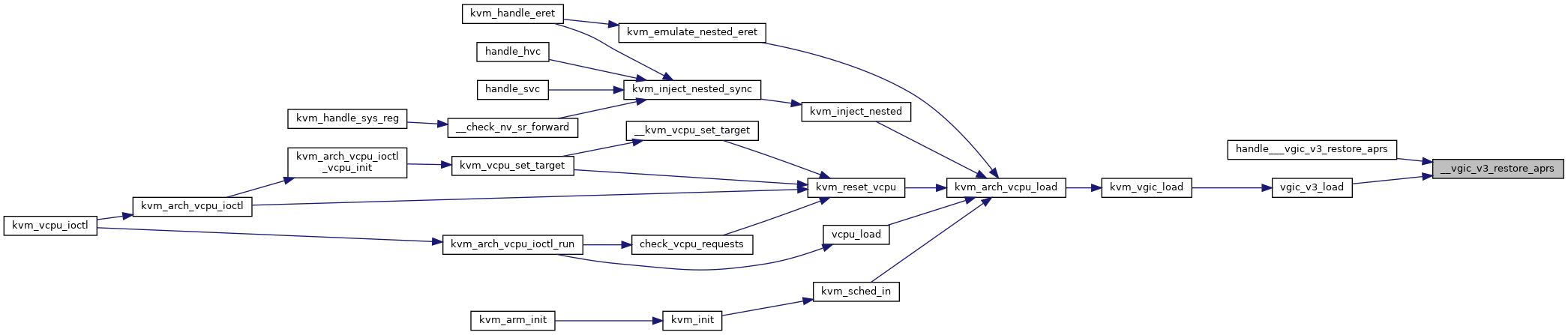

◆ __vgic_v3_restore_aprs()

| void __vgic_v3_restore_aprs | ( | struct vgic_v3_cpu_if * | cpu_if | ) |

Definition at line 366 of file vgic-v3-sr.c.

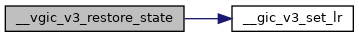

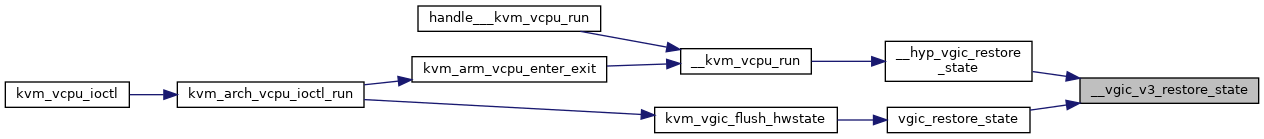

◆ __vgic_v3_restore_state()

| void __vgic_v3_restore_state | ( | struct vgic_v3_cpu_if * | cpu_if | ) |

Definition at line 234 of file vgic-v3-sr.c.

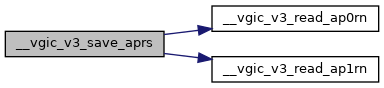

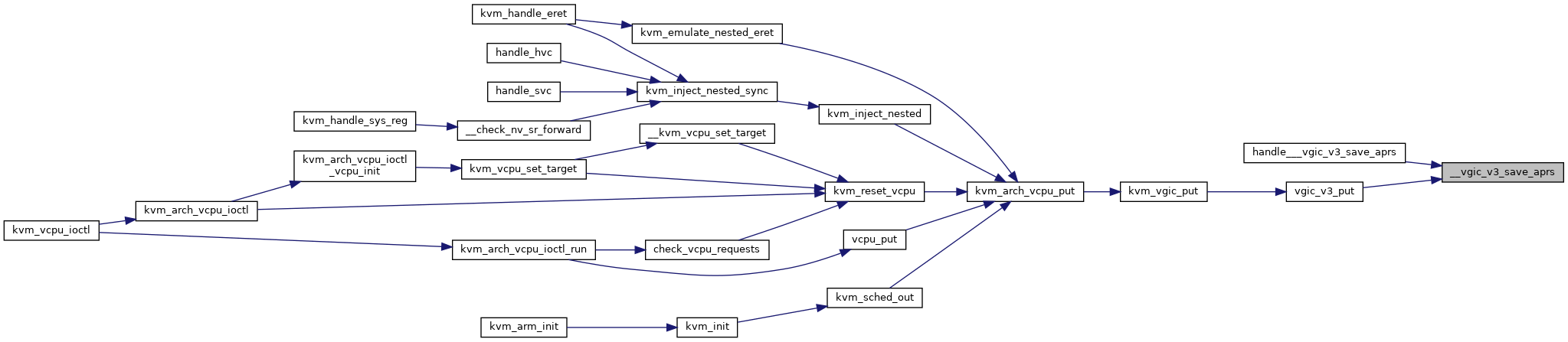

◆ __vgic_v3_save_aprs()

| void __vgic_v3_save_aprs | ( | struct vgic_v3_cpu_if * | cpu_if | ) |

Definition at line 333 of file vgic-v3-sr.c.

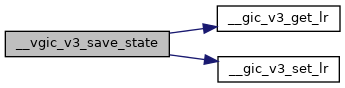

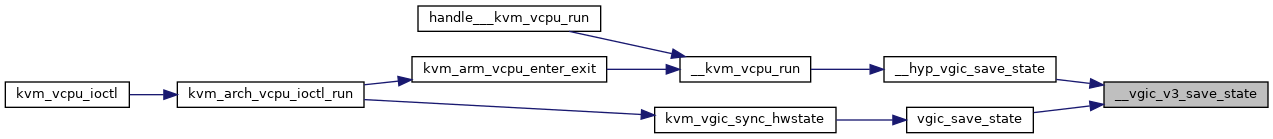

◆ __vgic_v3_save_state()

| void __vgic_v3_save_state | ( | struct vgic_v3_cpu_if * | cpu_if | ) |

Definition at line 199 of file vgic-v3-sr.c.

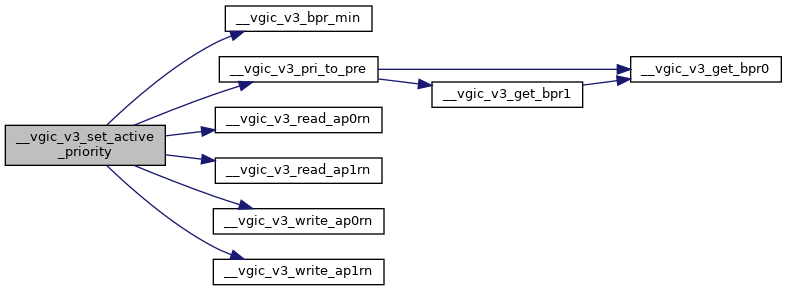

◆ __vgic_v3_set_active_priority()

|

static |

Definition at line 617 of file vgic-v3-sr.c.

◆ __vgic_v3_write_ap0rn()

|

static |

◆ __vgic_v3_write_ap1rn()

|

static |

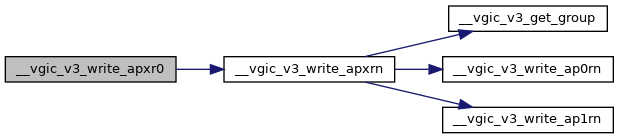

◆ __vgic_v3_write_apxr0()

|

static |

Definition at line 913 of file vgic-v3-sr.c.

◆ __vgic_v3_write_apxr1()

|

static |

Definition at line 918 of file vgic-v3-sr.c.

◆ __vgic_v3_write_apxr2()

|

static |

Definition at line 923 of file vgic-v3-sr.c.

◆ __vgic_v3_write_apxr3()

|

static |

Definition at line 928 of file vgic-v3-sr.c.

◆ __vgic_v3_write_apxrn()

|

static |

Definition at line 881 of file vgic-v3-sr.c.

◆ __vgic_v3_write_bpr0()

|

static |

Definition at line 832 of file vgic-v3-sr.c.

◆ __vgic_v3_write_bpr1()

|

static |

Definition at line 849 of file vgic-v3-sr.c.

◆ __vgic_v3_write_ctlr()

|

static |

◆ __vgic_v3_write_dir()

|

static |

Definition at line 730 of file vgic-v3-sr.c.

◆ __vgic_v3_write_eoir()

|

static |

Definition at line 753 of file vgic-v3-sr.c.

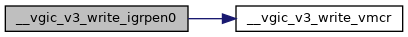

◆ __vgic_v3_write_igrpen0()

|

static |

Definition at line 798 of file vgic-v3-sr.c.

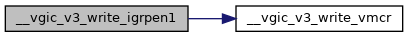

◆ __vgic_v3_write_igrpen1()

|

static |

Definition at line 810 of file vgic-v3-sr.c.

◆ __vgic_v3_write_pmr()

|

static |

◆ __vgic_v3_write_vmcr()

| void __vgic_v3_write_vmcr | ( | u32 | vmcr | ) |