#include <hyp/adjust_pc.h>#include <linux/kvm_host.h>#include <asm/kvm_emulate.h>#include <asm/kvm_mmu.h>#include <asm/kvm_nested.h>

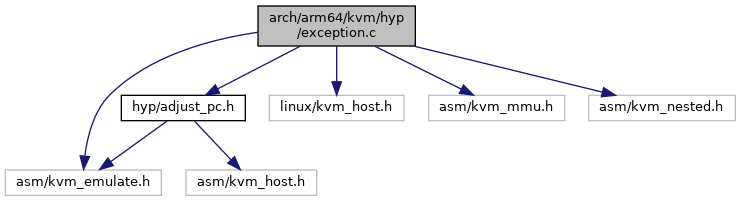

Include dependency graph for exception.c:

Go to the source code of this file.

Functions | |

| static u64 | __vcpu_read_sys_reg (const struct kvm_vcpu *vcpu, int reg) |

| static void | __vcpu_write_sys_reg (struct kvm_vcpu *vcpu, u64 val, int reg) |

| static void | __vcpu_write_spsr (struct kvm_vcpu *vcpu, unsigned long target_mode, u64 val) |

| static void | __vcpu_write_spsr_abt (struct kvm_vcpu *vcpu, u64 val) |

| static void | __vcpu_write_spsr_und (struct kvm_vcpu *vcpu, u64 val) |

| static void | enter_exception64 (struct kvm_vcpu *vcpu, unsigned long target_mode, enum exception_type type) |

| static unsigned long | get_except32_cpsr (struct kvm_vcpu *vcpu, u32 mode) |

| static void | enter_exception32 (struct kvm_vcpu *vcpu, u32 mode, u32 vect_offset) |

| static void | kvm_inject_exception (struct kvm_vcpu *vcpu) |

| void | __kvm_adjust_pc (struct kvm_vcpu *vcpu) |

Variables | |

| static const u8 | return_offsets [8][2] |

Function Documentation

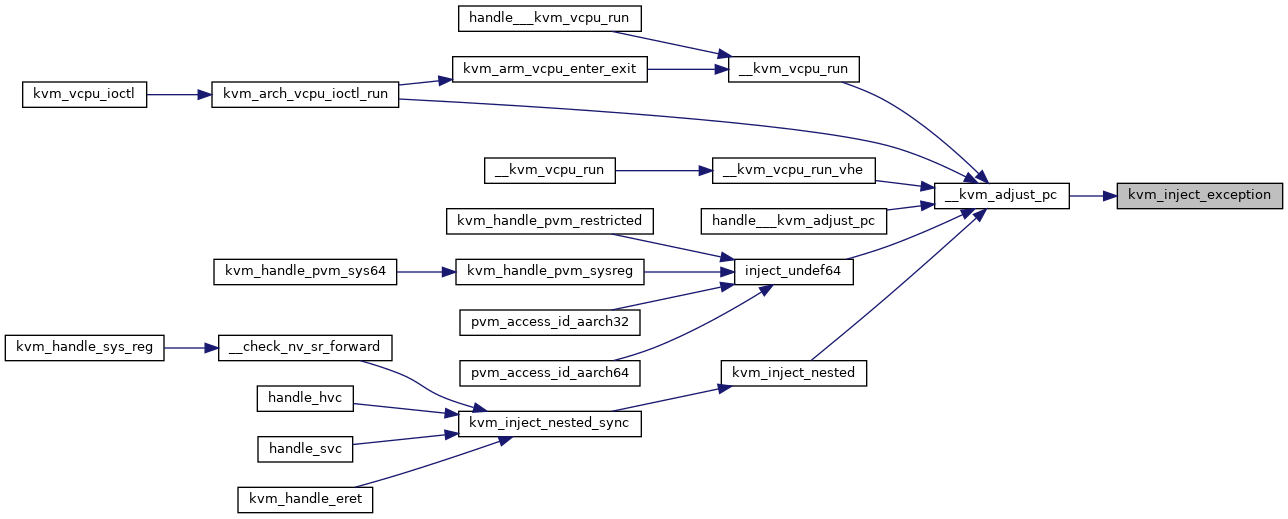

◆ __kvm_adjust_pc()

| void __kvm_adjust_pc | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 365 of file exception.c.

static void kvm_inject_exception(struct kvm_vcpu *vcpu)

Definition: exception.c:319

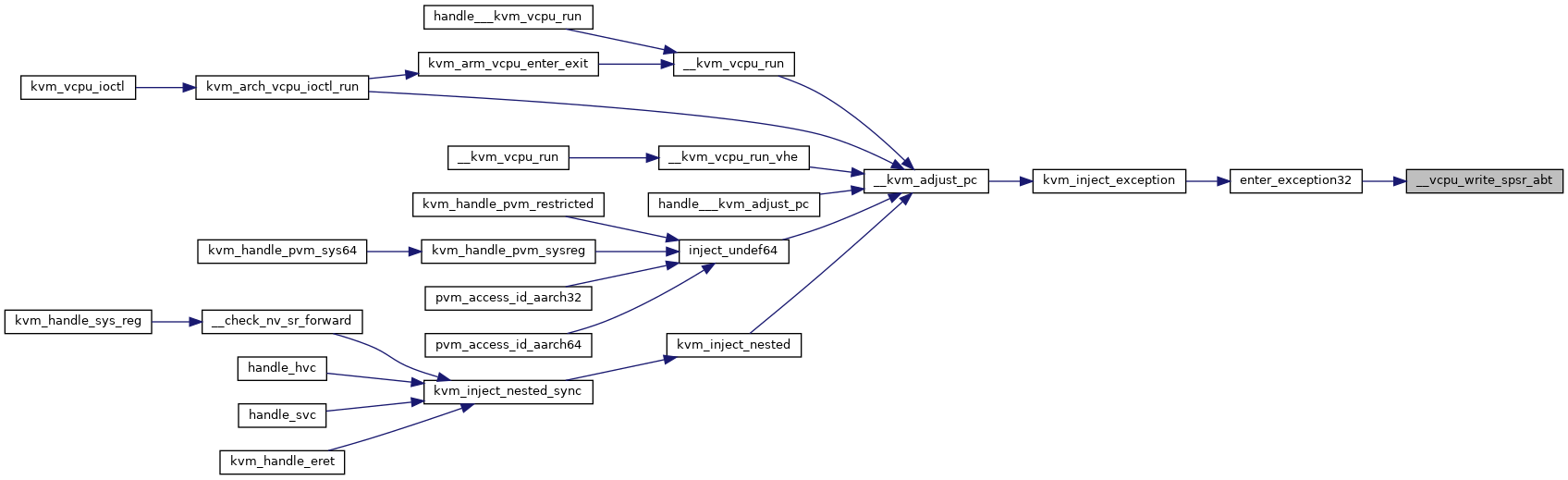

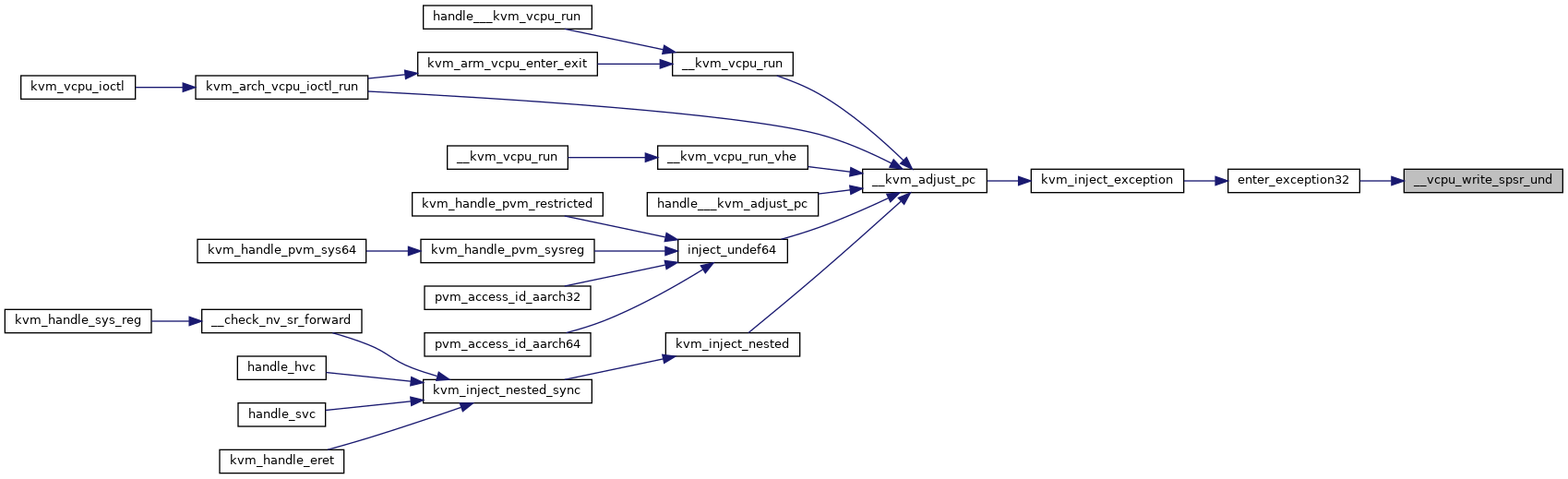

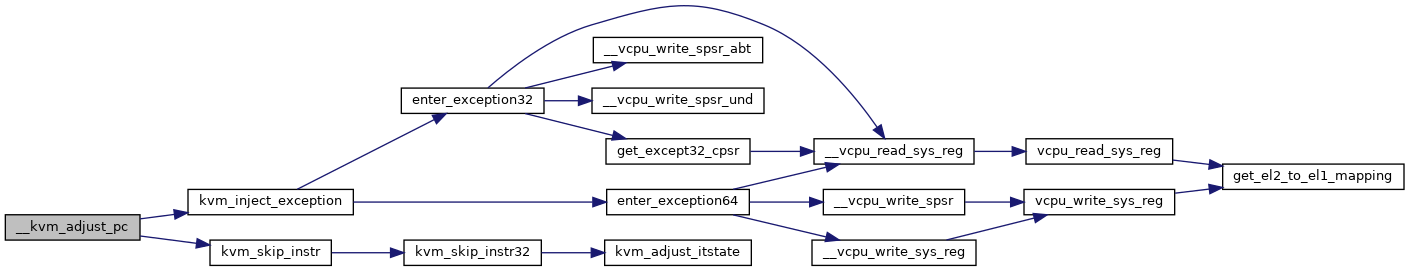

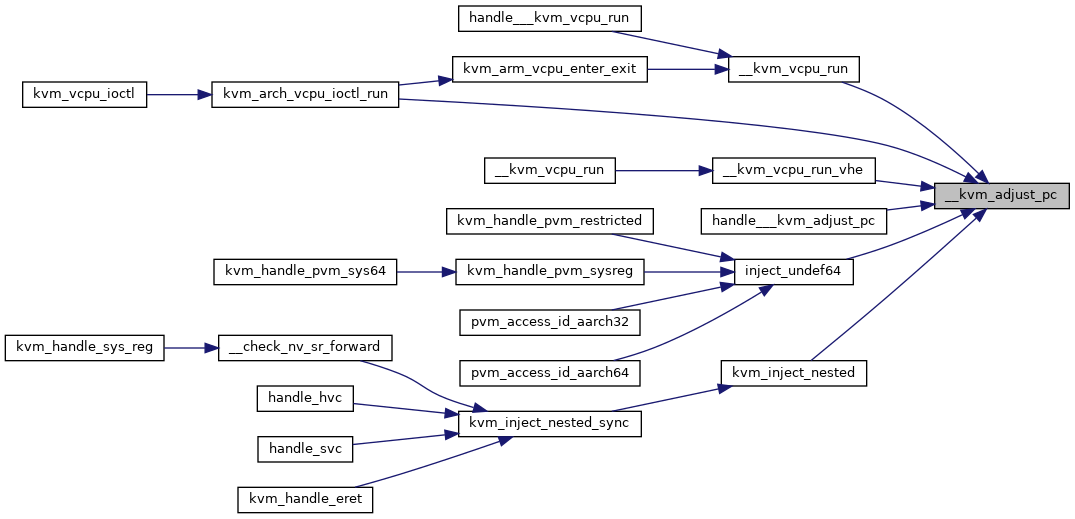

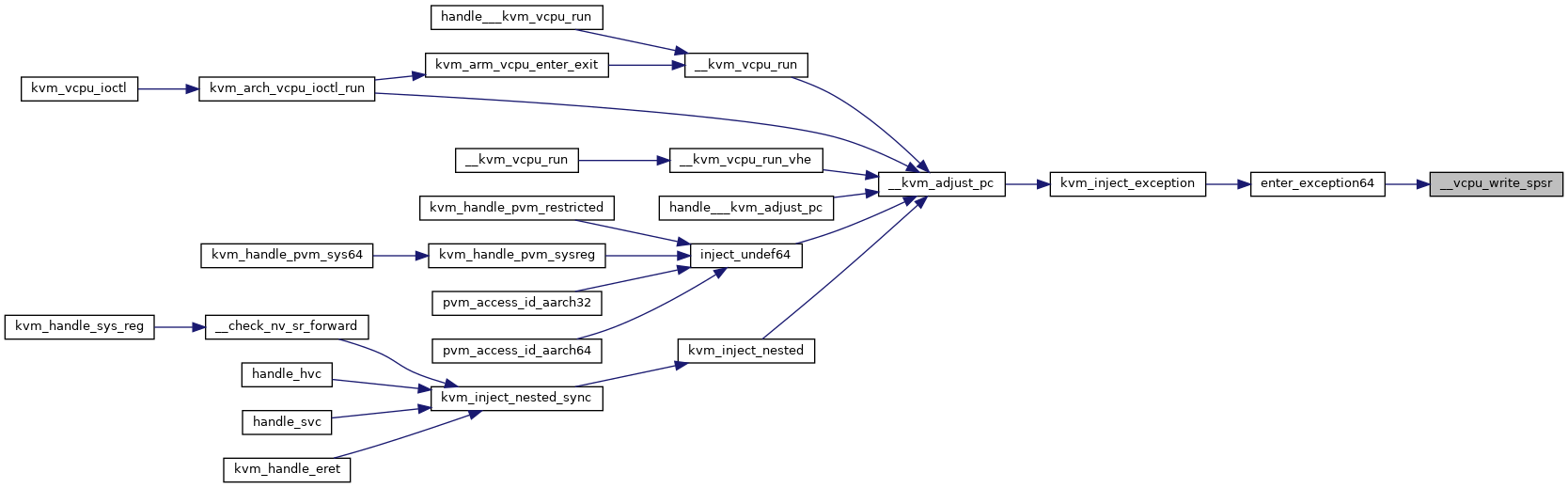

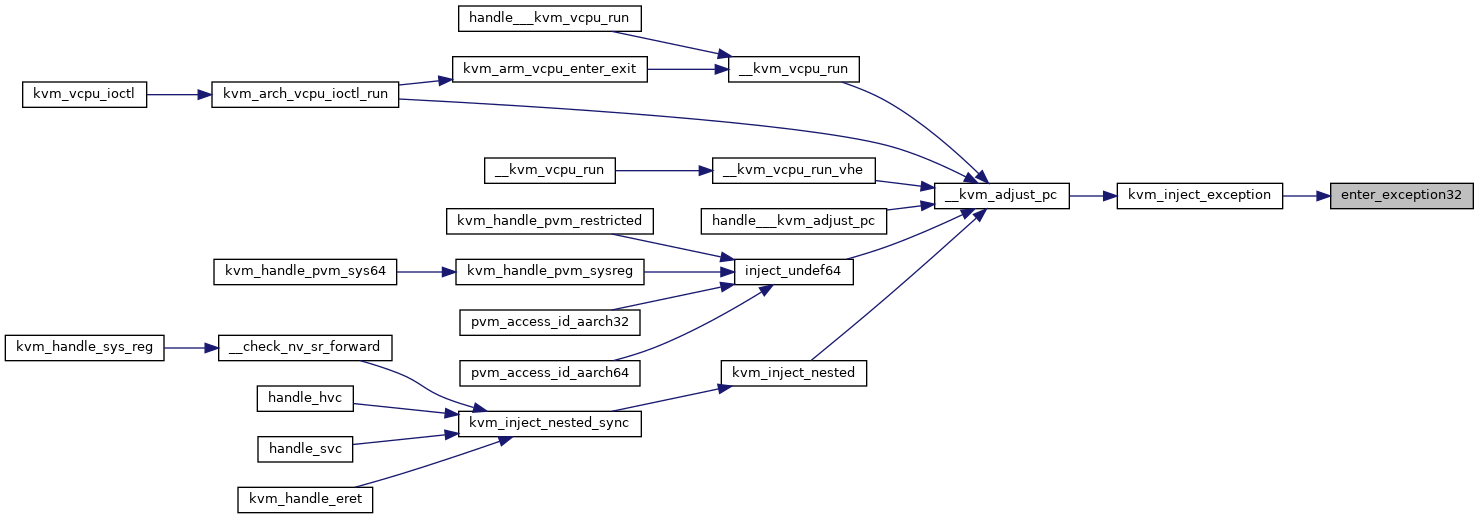

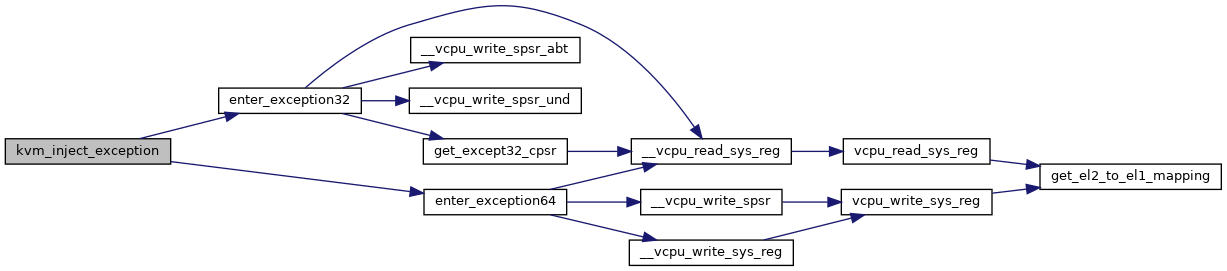

Here is the call graph for this function:

Here is the caller graph for this function:

◆ __vcpu_read_sys_reg()

|

inlinestatic |

Definition at line 23 of file exception.c.

u64 vcpu_read_sys_reg(const struct kvm_vcpu *vcpu, int reg)

Definition: sys_regs.c:128

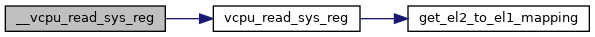

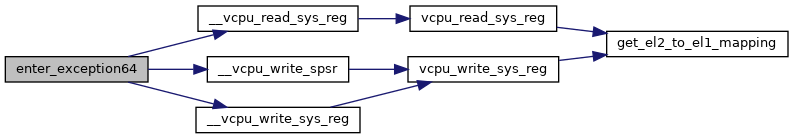

Here is the call graph for this function:

Here is the caller graph for this function:

◆ __vcpu_write_spsr()

|

static |

Definition at line 43 of file exception.c.

void vcpu_write_sys_reg(struct kvm_vcpu *vcpu, u64 val, int reg)

Definition: sys_regs.c:172

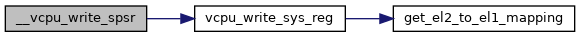

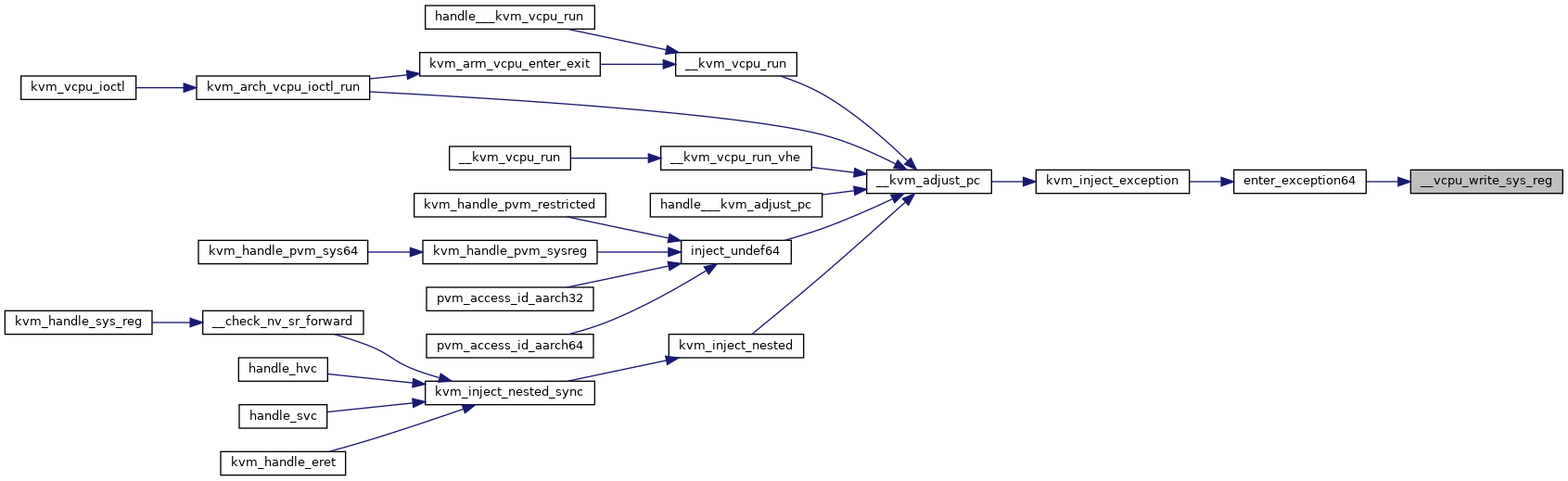

Here is the call graph for this function:

Here is the caller graph for this function:

◆ __vcpu_write_spsr_abt()

|

static |

◆ __vcpu_write_spsr_und()

|

static |

◆ __vcpu_write_sys_reg()

|

inlinestatic |

Definition at line 35 of file exception.c.

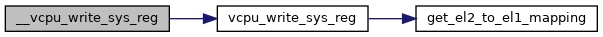

Here is the call graph for this function:

Here is the caller graph for this function:

◆ enter_exception32()

|

static |

Definition at line 286 of file exception.c.

static void __vcpu_write_spsr_abt(struct kvm_vcpu *vcpu, u64 val)

Definition: exception.c:58

static void __vcpu_write_spsr_und(struct kvm_vcpu *vcpu, u64 val)

Definition: exception.c:66

static u64 __vcpu_read_sys_reg(const struct kvm_vcpu *vcpu, int reg)

Definition: exception.c:23

static unsigned long get_except32_cpsr(struct kvm_vcpu *vcpu, u32 mode)

Definition: exception.c:192

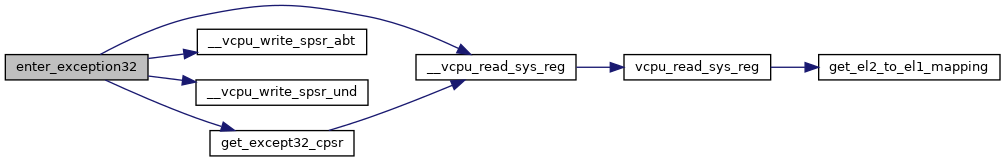

Here is the call graph for this function:

Here is the caller graph for this function:

◆ enter_exception64()

|

static |

Definition at line 91 of file exception.c.

static void __vcpu_write_spsr(struct kvm_vcpu *vcpu, unsigned long target_mode, u64 val)

Definition: exception.c:43

static void __vcpu_write_sys_reg(struct kvm_vcpu *vcpu, u64 val, int reg)

Definition: exception.c:35

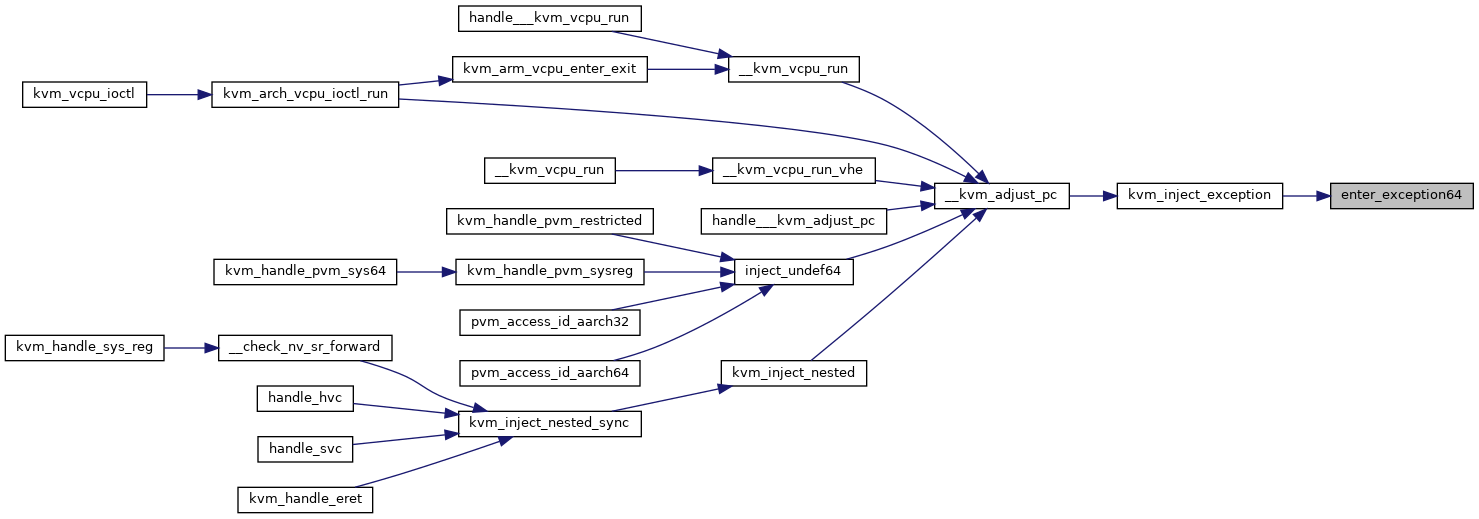

Here is the call graph for this function:

Here is the caller graph for this function:

◆ get_except32_cpsr()

|

static |

Definition at line 192 of file exception.c.

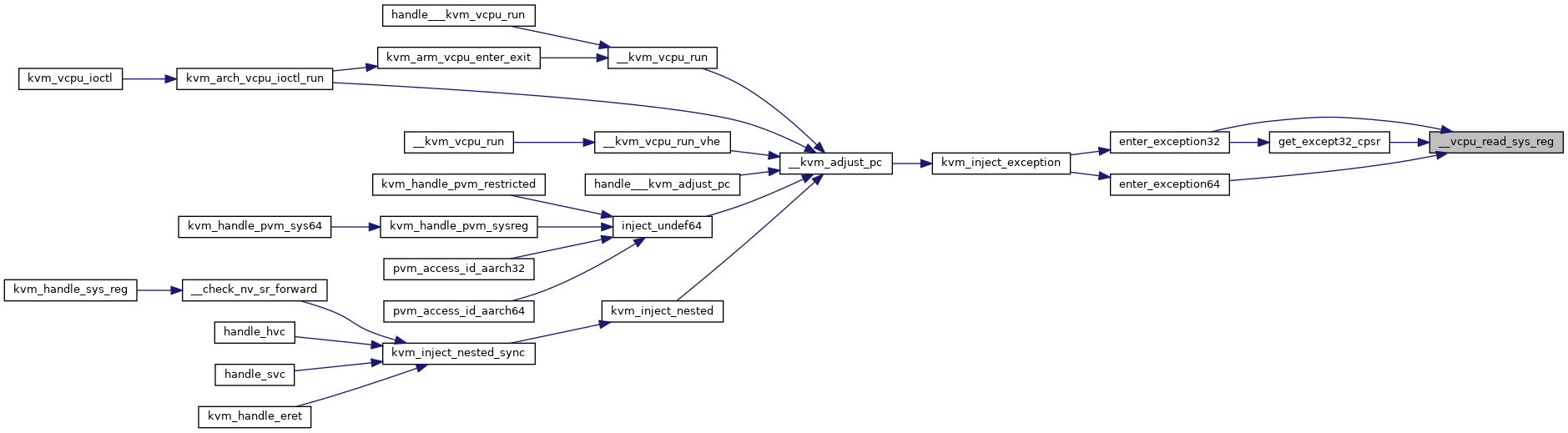

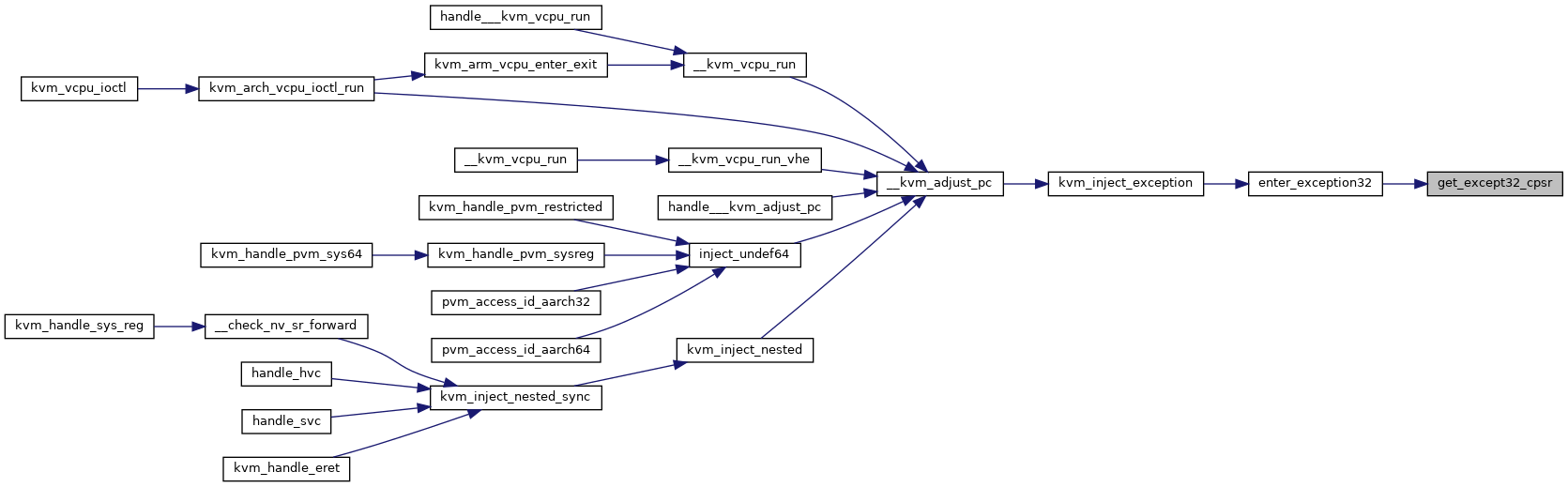

Here is the call graph for this function:

Here is the caller graph for this function:

◆ kvm_inject_exception()

|

static |

Definition at line 319 of file exception.c.

static void enter_exception64(struct kvm_vcpu *vcpu, unsigned long target_mode, enum exception_type type)

Definition: exception.c:91

static void enter_exception32(struct kvm_vcpu *vcpu, u32 mode, u32 vect_offset)

Definition: exception.c:286

Here is the call graph for this function:

Here is the caller graph for this function:

Variable Documentation

◆ return_offsets

|

static |

Initial value:

= {

[0] = { 0, 0 },

[1] = { 4, 2 },

[2] = { 0, 0 },

[3] = { 4, 4 },

[4] = { 8, 8 },

[5] = { 0, 0 },

[6] = { 4, 4 },

[7] = { 4, 4 },

}

Definition at line 275 of file exception.c.