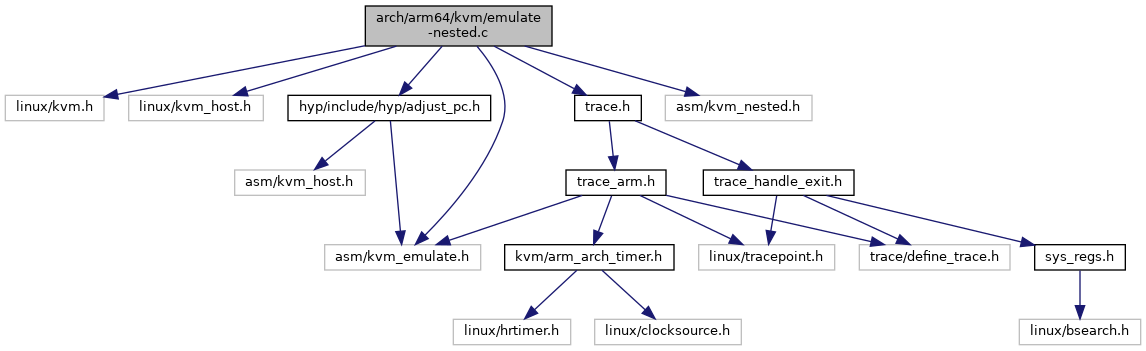

#include <linux/kvm.h>#include <linux/kvm_host.h>#include <asm/kvm_emulate.h>#include <asm/kvm_nested.h>#include "hyp/include/hyp/adjust_pc.h"#include "trace.h"

Go to the source code of this file.

Classes | |

| struct | trap_bits |

| union | trap_config |

| struct | encoding_to_trap_config |

Macros | |

| #define | MCB(id, ...) |

| #define | CCC(id, fn) [id - __COMPLEX_CONDITIONS__] = fn |

| #define | TC_CGT_BITS 10 |

| #define | TC_FGT_BITS 4 |

| #define | TC_FGF_BITS 5 |

| #define | SR_RANGE_TRAP(sr_start, sr_end, trap_id) |

| #define | SR_TRAP(sr, trap_id) SR_RANGE_TRAP(sr, sr, trap_id) |

| #define | SR_FGF(sr, g, b, p, f) |

| #define | SR_FGT(sr, g, b, p) SR_FGF(sr, g, b, p, __NO_FGF__) |

| #define | sanitised_sys_reg(vcpu, reg) |

Typedefs | |

| typedef enum trap_behaviour(* | complex_condition_check) (struct kvm_vcpu *) |

Functions | |

| static u64 | get_sanitized_cnthctl (struct kvm_vcpu *vcpu) |

| static enum trap_behaviour | check_cnthctl_el1pcten (struct kvm_vcpu *vcpu) |

| static enum trap_behaviour | check_cnthctl_el1pten (struct kvm_vcpu *vcpu) |

| static | DEFINE_XARRAY (sr_forward_xa) |

| static union trap_config | get_trap_config (u32 sysreg) |

| static __init void | print_nv_trap_error (const struct encoding_to_trap_config *tc, const char *type, int err) |

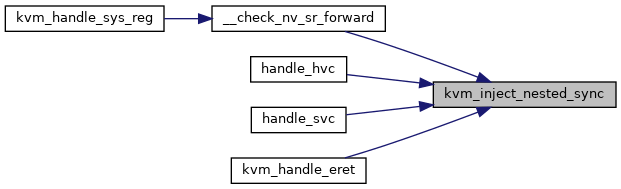

| int __init | populate_nv_trap_config (void) |

| static enum trap_behaviour | get_behaviour (struct kvm_vcpu *vcpu, const struct trap_bits *tb) |

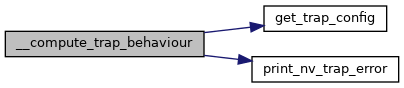

| static enum trap_behaviour | __compute_trap_behaviour (struct kvm_vcpu *vcpu, const enum cgt_group_id id, enum trap_behaviour b) |

| static enum trap_behaviour | compute_trap_behaviour (struct kvm_vcpu *vcpu, const union trap_config tc) |

| static bool | check_fgt_bit (u64 val, const union trap_config tc) |

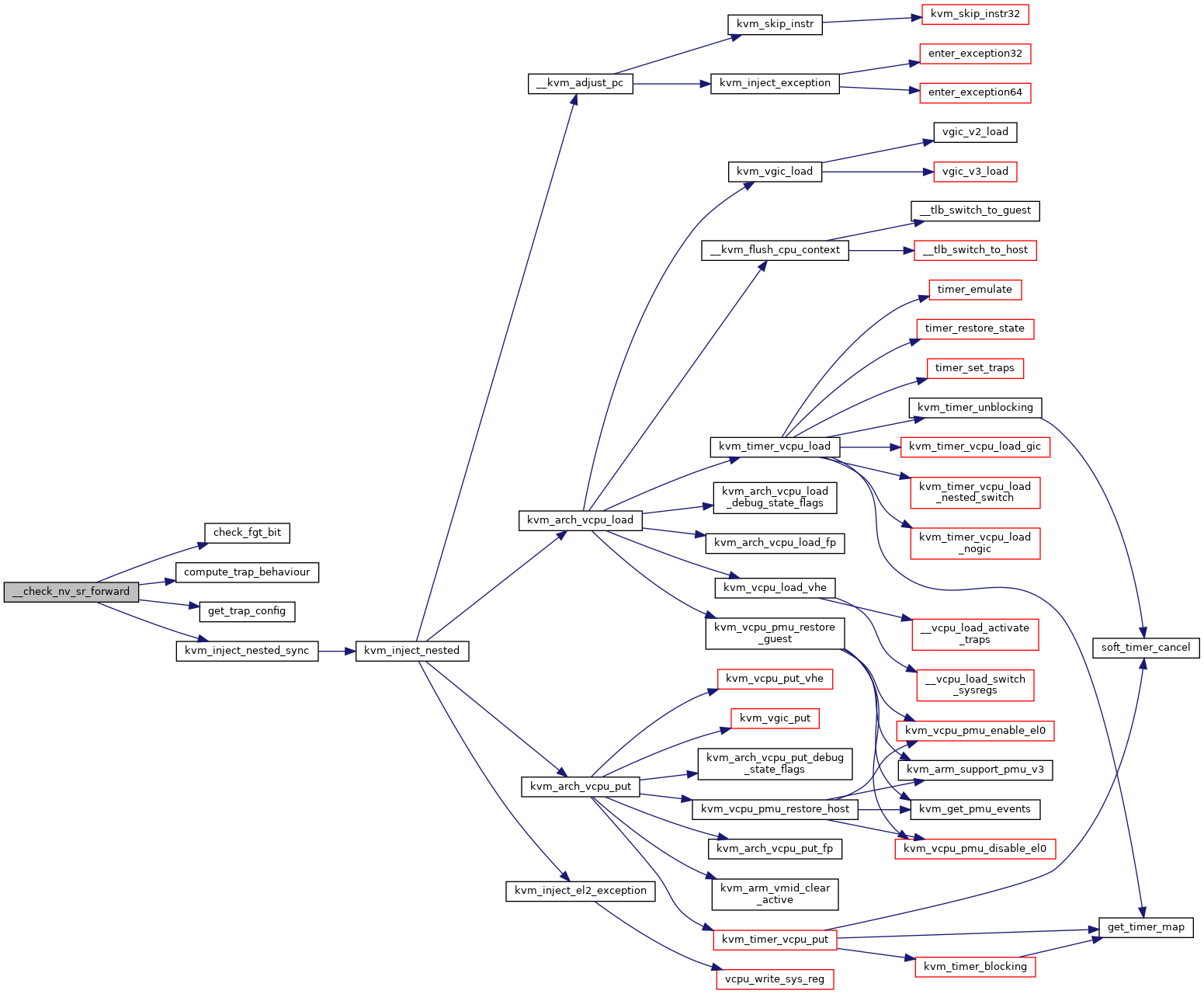

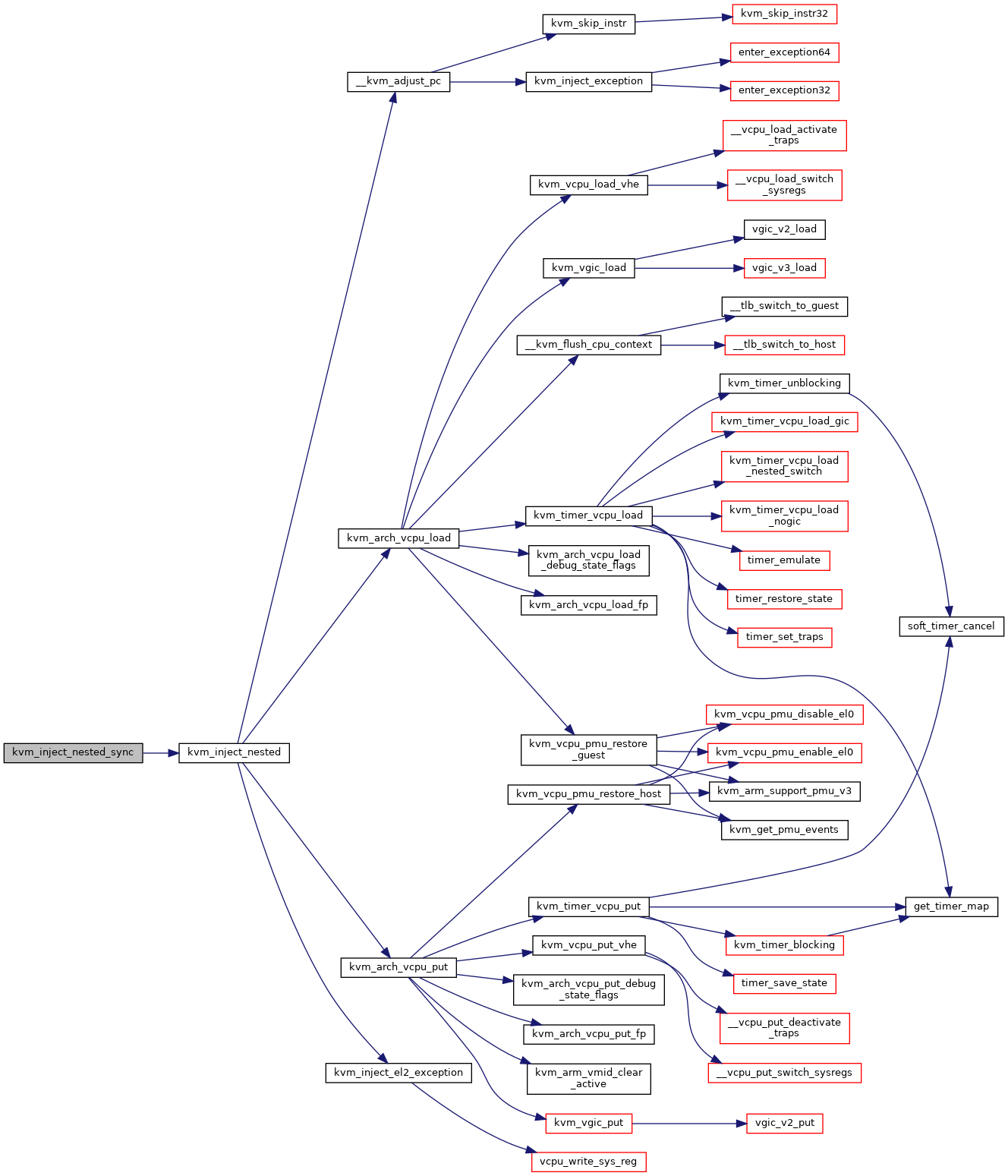

| bool | __check_nv_sr_forward (struct kvm_vcpu *vcpu) |

| static u64 | kvm_check_illegal_exception_return (struct kvm_vcpu *vcpu, u64 spsr) |

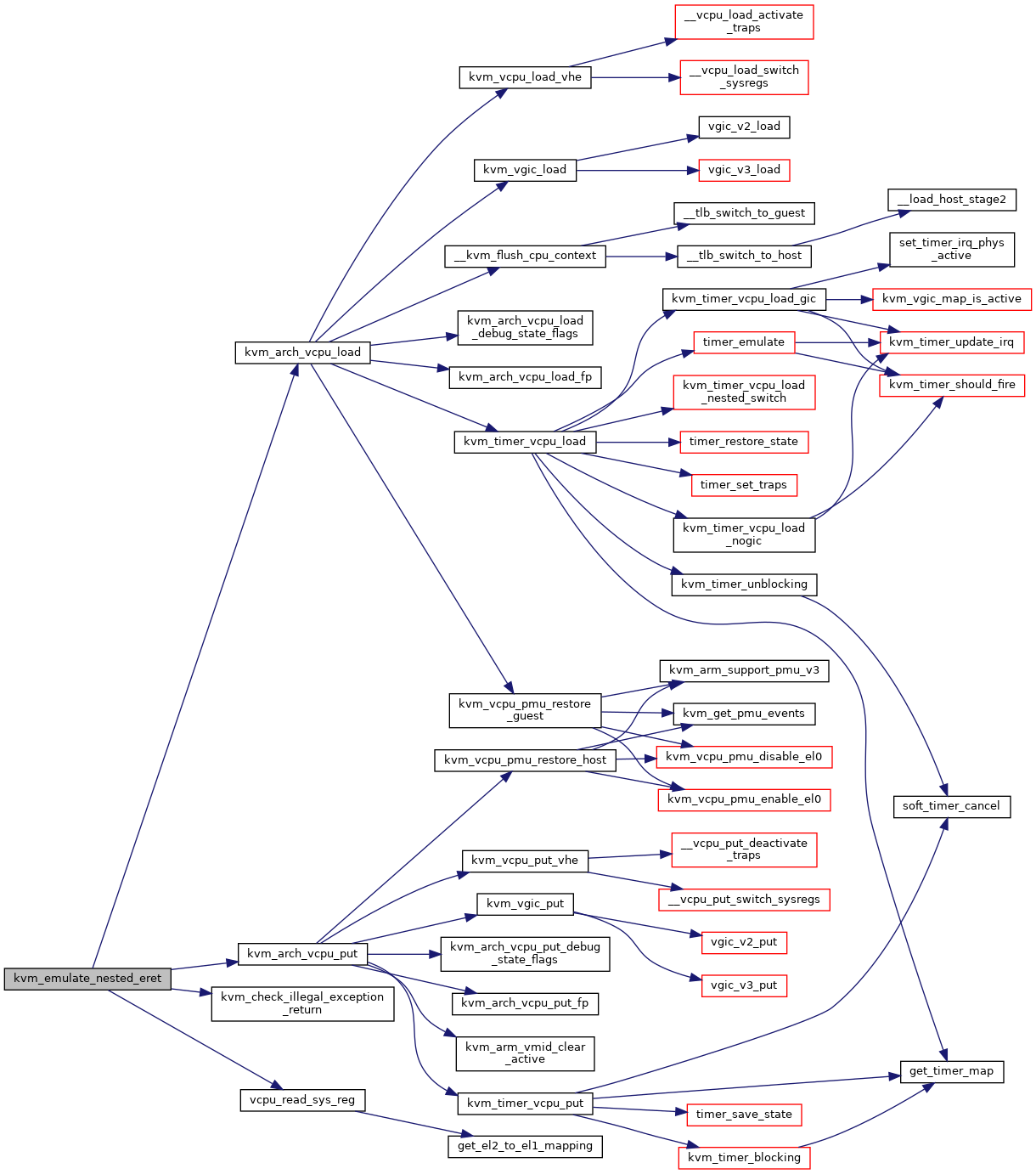

| void | kvm_emulate_nested_eret (struct kvm_vcpu *vcpu) |

| static void | kvm_inject_el2_exception (struct kvm_vcpu *vcpu, u64 esr_el2, enum exception_type type) |

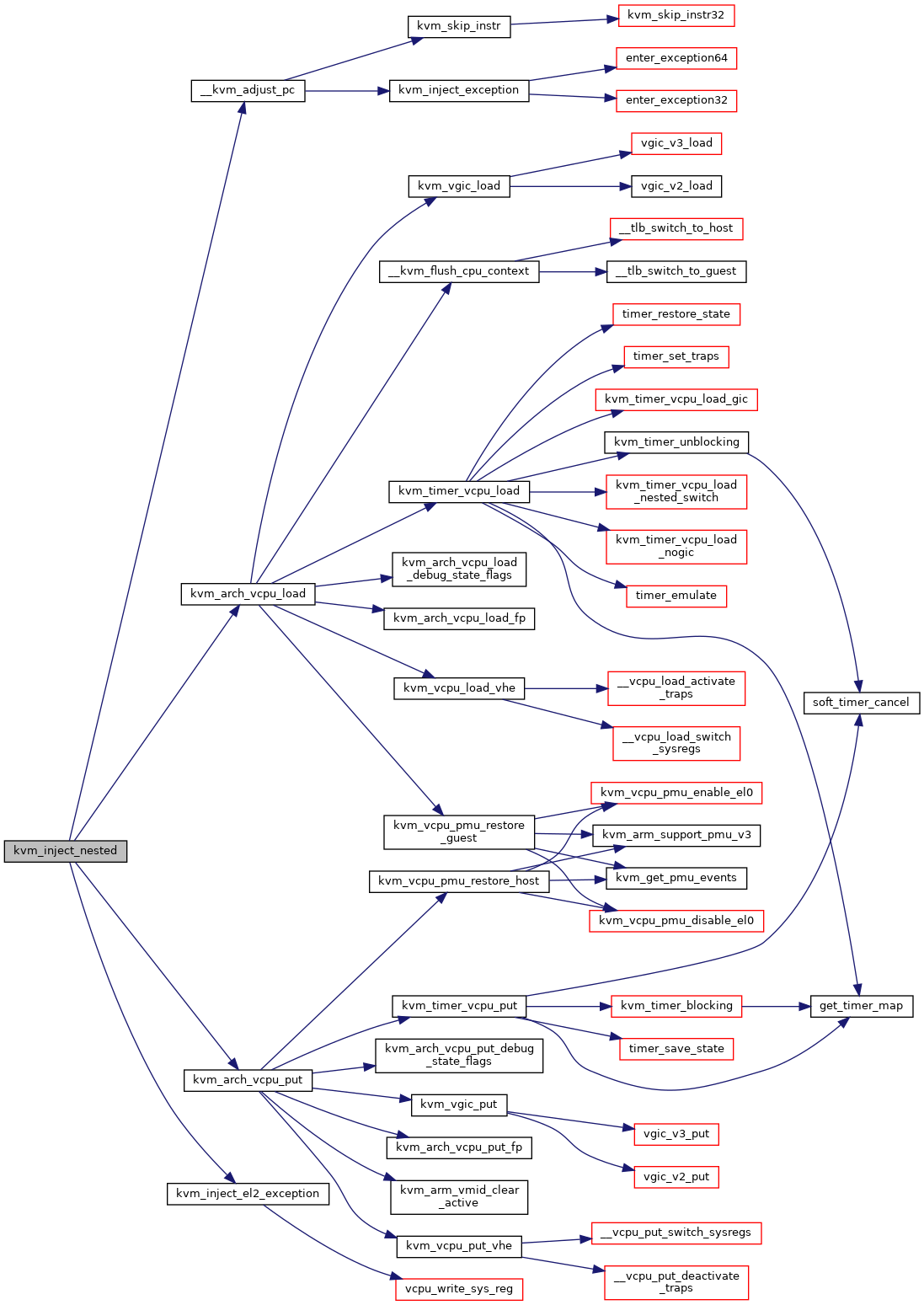

| static int | kvm_inject_nested (struct kvm_vcpu *vcpu, u64 esr_el2, enum exception_type type) |

| int | kvm_inject_nested_sync (struct kvm_vcpu *vcpu, u64 esr_el2) |

| int | kvm_inject_nested_irq (struct kvm_vcpu *vcpu) |

Variables | |

| static const struct trap_bits | coarse_trap_bits [] |

| static enum cgt_group_id * | coarse_control_combo [] |

| static const complex_condition_check | ccc [] |

| static const struct encoding_to_trap_config encoding_to_cgt[] | __initconst |

Macro Definition Documentation

◆ CCC

| #define CCC | ( | id, | |

| fn | |||

| ) | [id - __COMPLEX_CONDITIONS__] = fn |

Definition at line 413 of file emulate-nested.c.

◆ MCB

| #define MCB | ( | id, | |

| ... | |||

| ) |

Definition at line 350 of file emulate-nested.c.

◆ sanitised_sys_reg

| #define sanitised_sys_reg | ( | vcpu, | |

| reg | |||

| ) |

Definition at line 1900 of file emulate-nested.c.

◆ SR_FGF

| #define SR_FGF | ( | sr, | |

| g, | |||

| b, | |||

| p, | |||

| f | |||

| ) |

Definition at line 1029 of file emulate-nested.c.

◆ SR_FGT

| #define SR_FGT | ( | sr, | |

| g, | |||

| b, | |||

| p | |||

| ) | SR_FGF(sr, g, b, p, __NO_FGF__) |

Definition at line 1042 of file emulate-nested.c.

◆ SR_RANGE_TRAP

| #define SR_RANGE_TRAP | ( | sr_start, | |

| sr_end, | |||

| trap_id | |||

| ) |

Definition at line 457 of file emulate-nested.c.

◆ SR_TRAP

| #define SR_TRAP | ( | sr, | |

| trap_id | |||

| ) | SR_RANGE_TRAP(sr, sr, trap_id) |

Definition at line 467 of file emulate-nested.c.

◆ TC_CGT_BITS

| #define TC_CGT_BITS 10 |

Definition at line 433 of file emulate-nested.c.

◆ TC_FGF_BITS

| #define TC_FGF_BITS 5 |

Definition at line 435 of file emulate-nested.c.

◆ TC_FGT_BITS

| #define TC_FGT_BITS 4 |

Definition at line 434 of file emulate-nested.c.

Typedef Documentation

◆ complex_condition_check

| typedef enum trap_behaviour(* complex_condition_check) (struct kvm_vcpu *) |

Definition at line 356 of file emulate-nested.c.

Enumeration Type Documentation

◆ cgt_group_id

| enum cgt_group_id |

Definition at line 32 of file emulate-nested.c.

◆ fg_filter_id

| enum fg_filter_id |

| Enumerator | |

|---|---|

| __NO_FGF__ | |

| HCRX_FGTnXS | |

| __NR_FG_FILTER_IDS__ | |

Definition at line 1021 of file emulate-nested.c.

◆ fgt_group_id

| enum fgt_group_id |

| Enumerator | |

|---|---|

| __NO_FGT_GROUP__ | |

| HFGxTR_GROUP | |

| HDFGRTR_GROUP | |

| HDFGWTR_GROUP | |

| HFGITR_GROUP | |

| HAFGRTR_GROUP | |

| __NR_FGT_GROUP_IDS__ | |

Definition at line 1009 of file emulate-nested.c.

◆ trap_behaviour

| enum trap_behaviour |

| Enumerator | |

|---|---|

| BEHAVE_HANDLE_LOCALLY | |

| BEHAVE_FORWARD_READ | |

| BEHAVE_FORWARD_WRITE | |

| BEHAVE_FORWARD_ANY | |

Definition at line 17 of file emulate-nested.c.

Function Documentation

◆ __check_nv_sr_forward()

| bool __check_nv_sr_forward | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 1908 of file emulate-nested.c.

◆ __compute_trap_behaviour()

|

static |

Definition at line 1760 of file emulate-nested.c.

◆ check_cnthctl_el1pcten()

|

static |

Definition at line 387 of file emulate-nested.c.

◆ check_cnthctl_el1pten()

|

static |

Definition at line 387 of file emulate-nested.c.

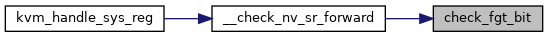

◆ check_fgt_bit()

|

static |

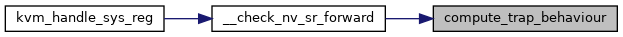

◆ compute_trap_behaviour()

|

static |

◆ DEFINE_XARRAY()

|

static |

◆ get_behaviour()

|

static |

Definition at line 1760 of file emulate-nested.c.

◆ get_sanitized_cnthctl()

|

static |

Definition at line 387 of file emulate-nested.c.

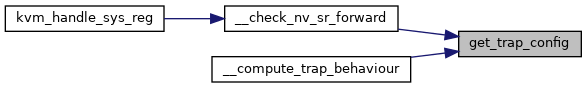

◆ get_trap_config()

|

static |

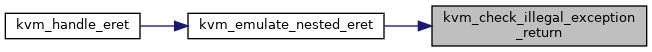

◆ kvm_check_illegal_exception_return()

|

static |

◆ kvm_emulate_nested_eret()

| void kvm_emulate_nested_eret | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 2032 of file emulate-nested.c.

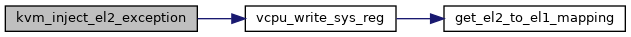

◆ kvm_inject_el2_exception()

|

static |

Definition at line 2079 of file emulate-nested.c.

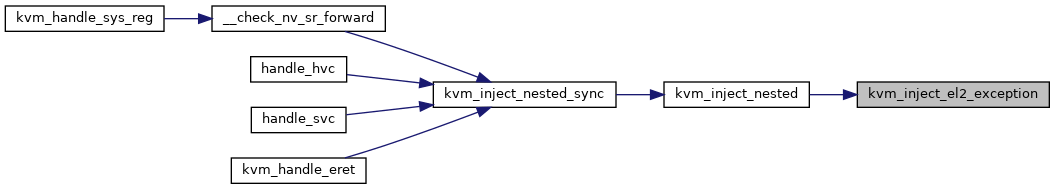

◆ kvm_inject_nested()

|

static |

Definition at line 2101 of file emulate-nested.c.

◆ kvm_inject_nested_irq()

| int kvm_inject_nested_irq | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 2167 of file emulate-nested.c.

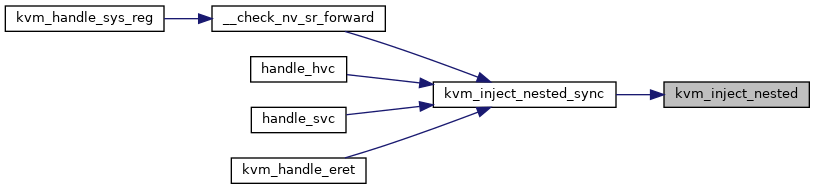

◆ kvm_inject_nested_sync()

| int kvm_inject_nested_sync | ( | struct kvm_vcpu * | vcpu, |

| u64 | esr_el2 | ||

| ) |

Definition at line 2162 of file emulate-nested.c.

◆ populate_nv_trap_config()

| int __init populate_nv_trap_config | ( | void | ) |

Definition at line 1760 of file emulate-nested.c.

◆ print_nv_trap_error()

|

static |

Variable Documentation

◆ __initconst

|

static |

Definition at line 476 of file emulate-nested.c.

◆ ccc

|

static |

Definition at line 416 of file emulate-nested.c.

◆ coarse_control_combo

|

static |

Definition at line 356 of file emulate-nested.c.

◆ coarse_trap_bits

|

static |

Definition at line 1 of file emulate-nested.c.