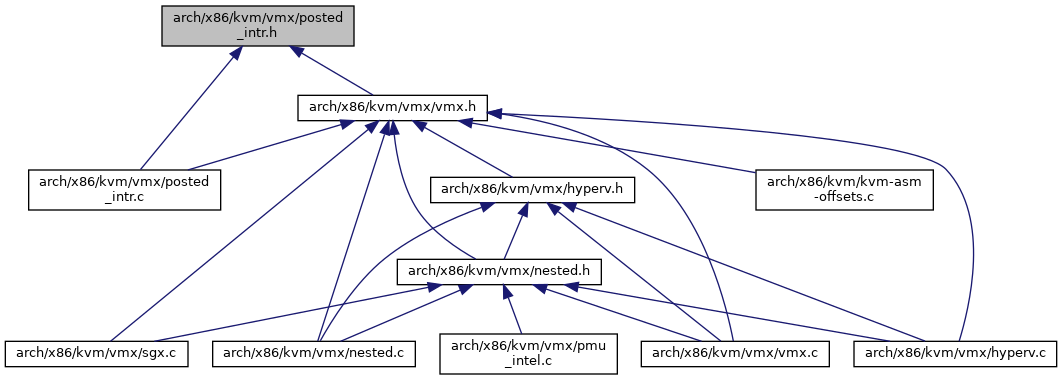

Go to the source code of this file.

Classes | |

| struct | pi_desc |

Macros | |

| #define | POSTED_INTR_ON 0 |

| #define | POSTED_INTR_SN 1 |

| #define | PID_TABLE_ENTRY_VALID 1 |

Functions | |

| struct pi_desc | __aligned (64) |

| static bool | pi_test_and_set_on (struct pi_desc *pi_desc) |

| static bool | pi_test_and_clear_on (struct pi_desc *pi_desc) |

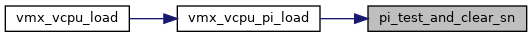

| static bool | pi_test_and_clear_sn (struct pi_desc *pi_desc) |

| static bool | pi_test_and_set_pir (int vector, struct pi_desc *pi_desc) |

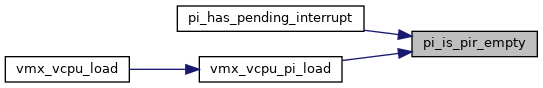

| static bool | pi_is_pir_empty (struct pi_desc *pi_desc) |

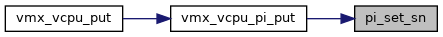

| static void | pi_set_sn (struct pi_desc *pi_desc) |

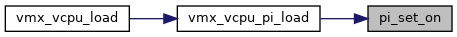

| static void | pi_set_on (struct pi_desc *pi_desc) |

| static void | pi_clear_on (struct pi_desc *pi_desc) |

| static void | pi_clear_sn (struct pi_desc *pi_desc) |

| static bool | pi_test_on (struct pi_desc *pi_desc) |

| static bool | pi_test_sn (struct pi_desc *pi_desc) |

| void | vmx_vcpu_pi_load (struct kvm_vcpu *vcpu, int cpu) |

| void | vmx_vcpu_pi_put (struct kvm_vcpu *vcpu) |

| void | pi_wakeup_handler (void) |

| void __init | pi_init_cpu (int cpu) |

| bool | pi_has_pending_interrupt (struct kvm_vcpu *vcpu) |

| int | vmx_pi_update_irte (struct kvm *kvm, unsigned int host_irq, uint32_t guest_irq, bool set) |

| void | vmx_pi_start_assignment (struct kvm *kvm) |

Variables | |

| u32 | pir [8] |

| union { | |

| struct { | |

| u16 on: 1 | |

| u16 sn: 1 | |

| u16 rsvd_1: 14 | |

| u8 nv | |

| u8 rsvd_2 | |

| u32 ndst | |

| } | |

| u64 control | |

| }; | |

| u32 | rsvd [6] |

Macro Definition Documentation

◆ PID_TABLE_ENTRY_VALID

| #define PID_TABLE_ENTRY_VALID 1 |

Definition at line 8 of file posted_intr.h.

◆ POSTED_INTR_ON

| #define POSTED_INTR_ON 0 |

Definition at line 5 of file posted_intr.h.

◆ POSTED_INTR_SN

| #define POSTED_INTR_SN 1 |

Definition at line 6 of file posted_intr.h.

Function Documentation

◆ __aligned()

| struct pi_desc __aligned | ( | 64 | ) |

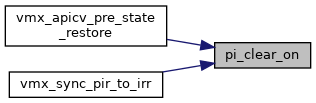

◆ pi_clear_on()

|

inlinestatic |

Definition at line 73 of file posted_intr.h.

◆ pi_clear_sn()

|

inlinestatic |

Definition at line 79 of file posted_intr.h.

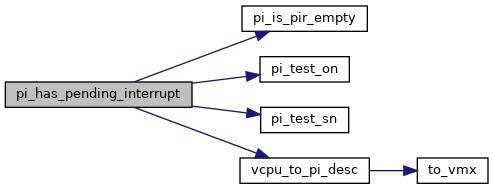

◆ pi_has_pending_interrupt()

| bool pi_has_pending_interrupt | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 240 of file posted_intr.c.

◆ pi_init_cpu()

| void __init pi_init_cpu | ( | int | cpu | ) |

◆ pi_is_pir_empty()

|

inlinestatic |

◆ pi_set_on()

|

inlinestatic |

◆ pi_set_sn()

|

inlinestatic |

◆ pi_test_and_clear_on()

|

inlinestatic |

◆ pi_test_and_clear_sn()

|

inlinestatic |

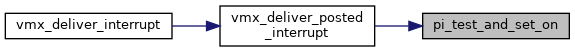

◆ pi_test_and_set_on()

|

inlinestatic |

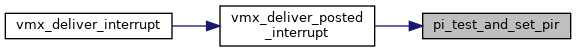

◆ pi_test_and_set_pir()

|

inlinestatic |

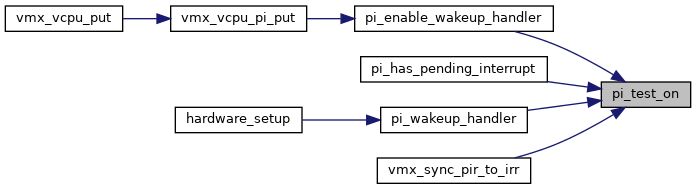

◆ pi_test_on()

|

inlinestatic |

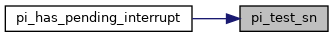

◆ pi_test_sn()

|

inlinestatic |

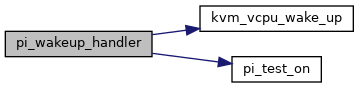

◆ pi_wakeup_handler()

| void pi_wakeup_handler | ( | void | ) |

Definition at line 218 of file posted_intr.c.

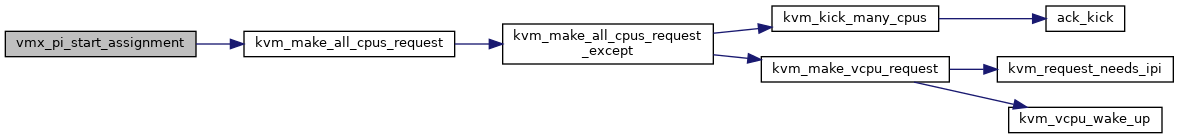

◆ vmx_pi_start_assignment()

| void vmx_pi_start_assignment | ( | struct kvm * | kvm | ) |

Definition at line 255 of file posted_intr.c.

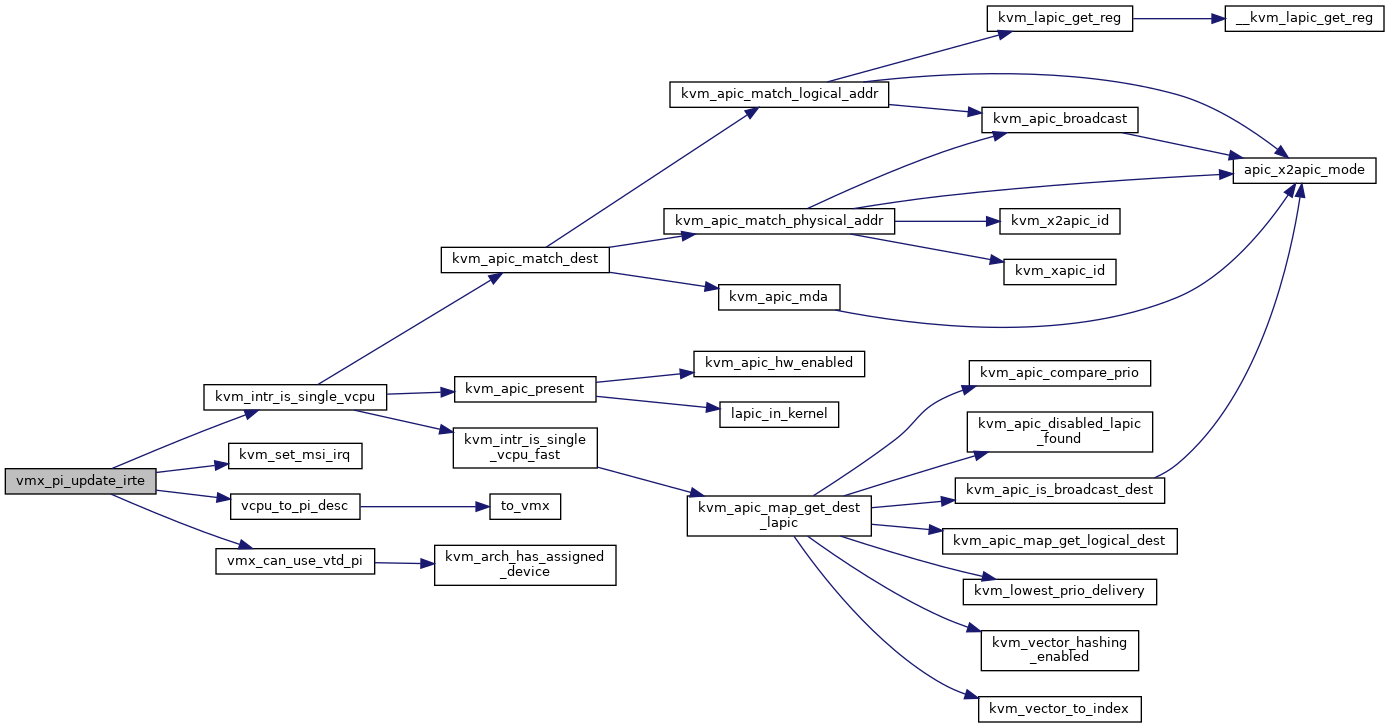

◆ vmx_pi_update_irte()

| int vmx_pi_update_irte | ( | struct kvm * | kvm, |

| unsigned int | host_irq, | ||

| uint32_t | guest_irq, | ||

| bool | set | ||

| ) |

Definition at line 272 of file posted_intr.c.

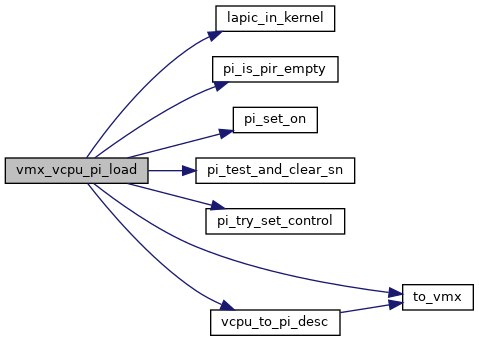

◆ vmx_vcpu_pi_load()

| void vmx_vcpu_pi_load | ( | struct kvm_vcpu * | vcpu, |

| int | cpu | ||

| ) |

Definition at line 53 of file posted_intr.c.

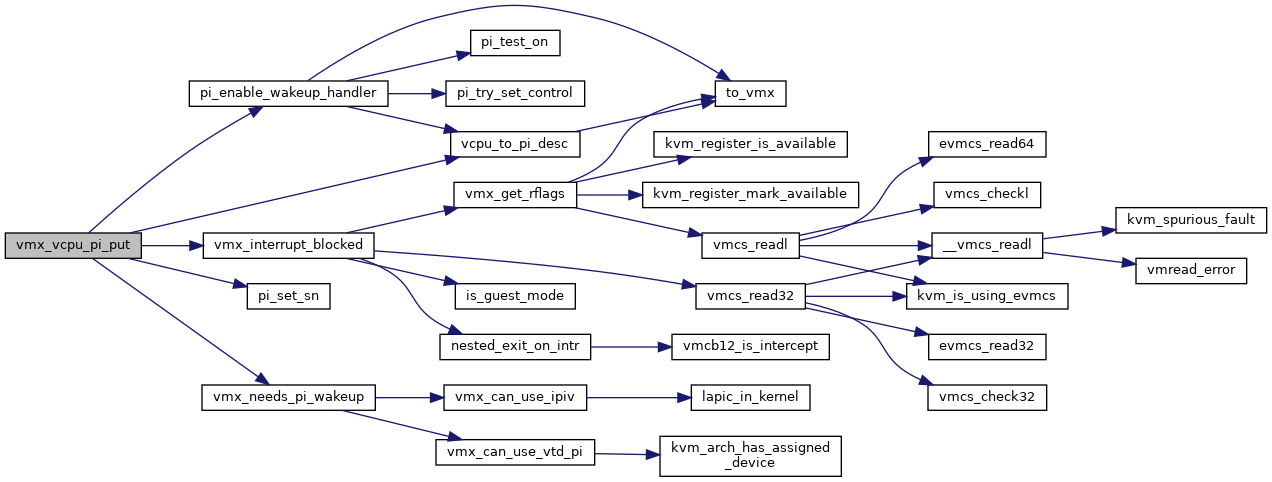

◆ vmx_vcpu_pi_put()

| void vmx_vcpu_pi_put | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 196 of file posted_intr.c.

Variable Documentation

◆

| union { ... } |

◆ control

| u64 control |

Definition at line 16 of file posted_intr.h.

◆ ndst

| u32 ndst |

Definition at line 14 of file posted_intr.h.

◆ nv

| u8 nv |

Definition at line 10 of file posted_intr.h.

◆ on

| u16 on |

Definition at line 4 of file posted_intr.h.

◆ pir

| u32 pir[8] |

Definition at line 0 of file posted_intr.h.

◆ rsvd

| u32 rsvd[6] |

Definition at line 18 of file posted_intr.h.

◆ rsvd_1

| u16 rsvd_1 |

Definition at line 8 of file posted_intr.h.

◆ rsvd_2

| u8 rsvd_2 |

Definition at line 12 of file posted_intr.h.

◆ sn

| u16 sn |

Definition at line 6 of file posted_intr.h.