#include <linux/irqchip/arm-gic.h>#include <linux/kvm.h>#include <linux/kvm_host.h>#include <kvm/arm_vgic.h>#include <asm/kvm_mmu.h>#include "vgic.h"

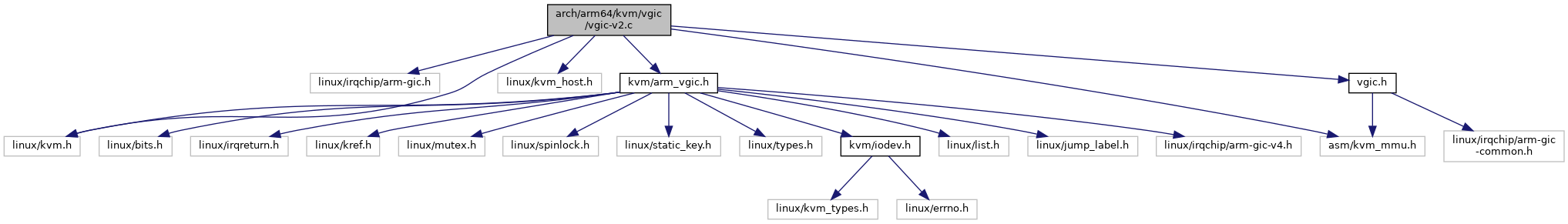

Include dependency graph for vgic-v2.c:

Go to the source code of this file.

Functions | |

| static void | vgic_v2_write_lr (int lr, u32 val) |

| void | vgic_v2_init_lrs (void) |

| void | vgic_v2_set_underflow (struct kvm_vcpu *vcpu) |

| static bool | lr_signals_eoi_mi (u32 lr_val) |

| void | vgic_v2_fold_lr_state (struct kvm_vcpu *vcpu) |

| void | vgic_v2_populate_lr (struct kvm_vcpu *vcpu, struct vgic_irq *irq, int lr) |

| void | vgic_v2_clear_lr (struct kvm_vcpu *vcpu, int lr) |

| void | vgic_v2_set_vmcr (struct kvm_vcpu *vcpu, struct vgic_vmcr *vmcrp) |

| void | vgic_v2_get_vmcr (struct kvm_vcpu *vcpu, struct vgic_vmcr *vmcrp) |

| void | vgic_v2_enable (struct kvm_vcpu *vcpu) |

| static bool | vgic_v2_check_base (gpa_t dist_base, gpa_t cpu_base) |

| int | vgic_v2_map_resources (struct kvm *kvm) |

| DEFINE_STATIC_KEY_FALSE (vgic_v2_cpuif_trap) | |

| int | vgic_v2_probe (const struct gic_kvm_info *info) |

| static void | save_lrs (struct kvm_vcpu *vcpu, void __iomem *base) |

| void | vgic_v2_save_state (struct kvm_vcpu *vcpu) |

| void | vgic_v2_restore_state (struct kvm_vcpu *vcpu) |

| void | vgic_v2_load (struct kvm_vcpu *vcpu) |

| void | vgic_v2_vmcr_sync (struct kvm_vcpu *vcpu) |

| void | vgic_v2_put (struct kvm_vcpu *vcpu) |

Function Documentation

◆ DEFINE_STATIC_KEY_FALSE()

| DEFINE_STATIC_KEY_FALSE | ( | vgic_v2_cpuif_trap | ) |

◆ lr_signals_eoi_mi()

|

static |

◆ save_lrs()

|

static |

Definition at line 403 of file vgic-v2.c.

Definition: arm_vgic.h:297

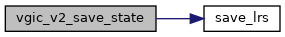

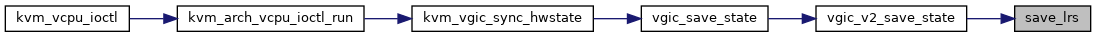

Here is the caller graph for this function:

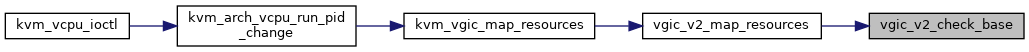

◆ vgic_v2_check_base()

|

static |

◆ vgic_v2_clear_lr()

| void vgic_v2_clear_lr | ( | struct kvm_vcpu * | vcpu, |

| int | lr | ||

| ) |

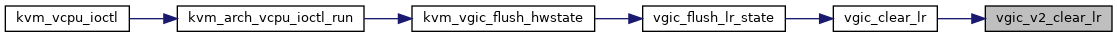

◆ vgic_v2_enable()

| void vgic_v2_enable | ( | struct kvm_vcpu * | vcpu | ) |

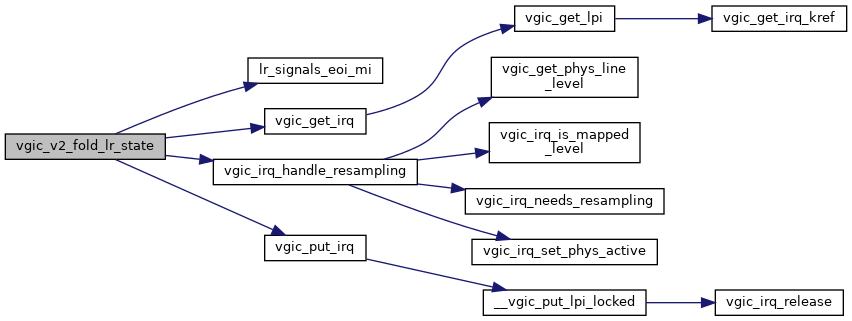

◆ vgic_v2_fold_lr_state()

| void vgic_v2_fold_lr_state | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 49 of file vgic-v2.c.

Definition: arm_vgic.h:325

Definition: arm_vgic.h:117

void vgic_irq_handle_resampling(struct vgic_irq *irq, bool lr_deactivated, bool lr_pending)

Definition: vgic.c:1060

struct vgic_irq * vgic_get_irq(struct kvm *kvm, struct kvm_vcpu *vcpu, u32 intid)

Definition: vgic.c:92

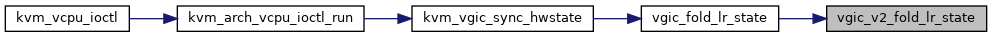

Here is the call graph for this function:

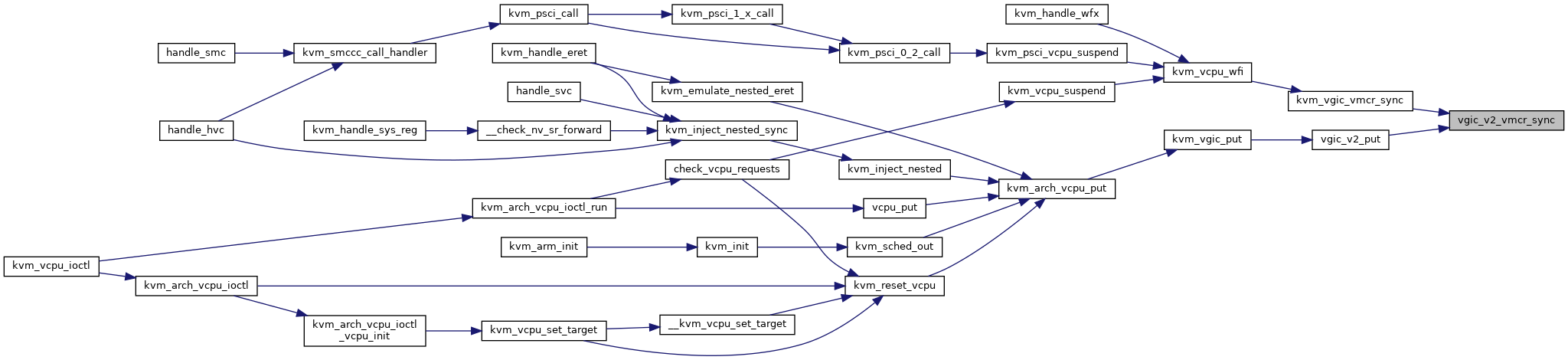

Here is the caller graph for this function:

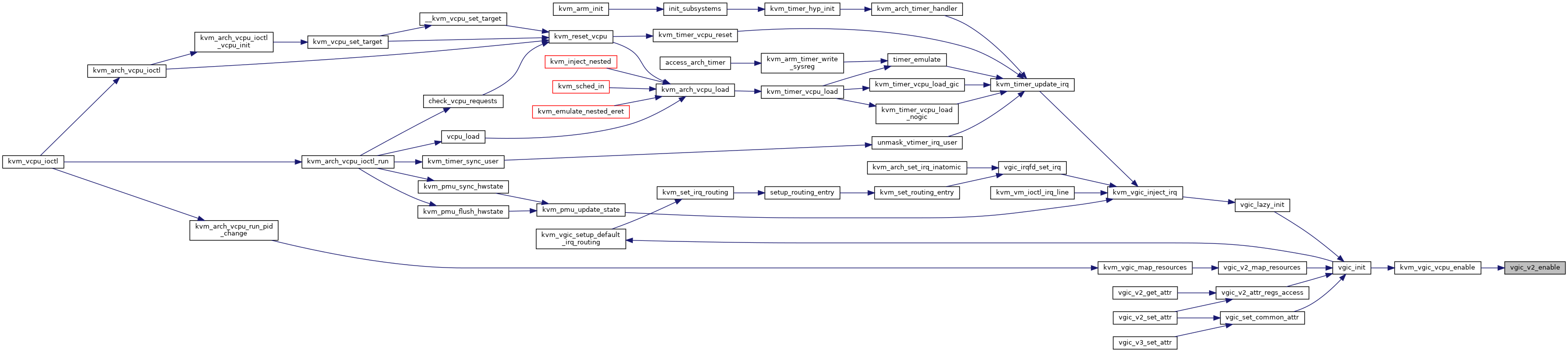

◆ vgic_v2_get_vmcr()

| void vgic_v2_get_vmcr | ( | struct kvm_vcpu * | vcpu, |

| struct vgic_vmcr * | vmcrp | ||

| ) |

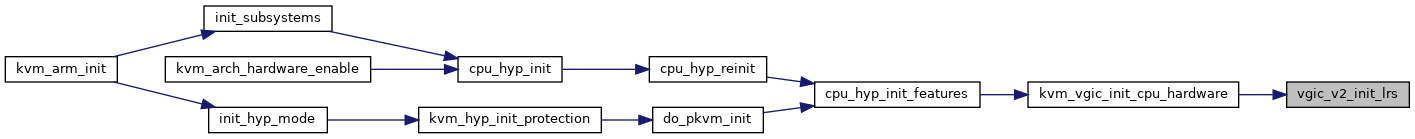

◆ vgic_v2_init_lrs()

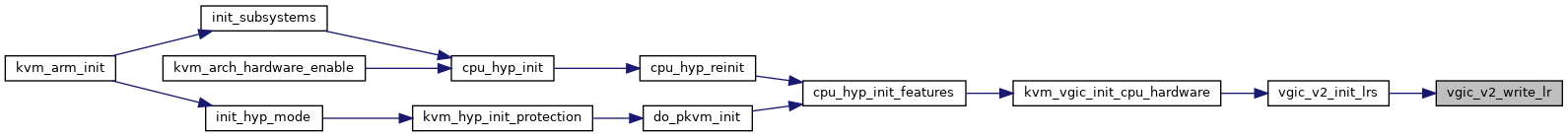

| void vgic_v2_init_lrs | ( | void | ) |

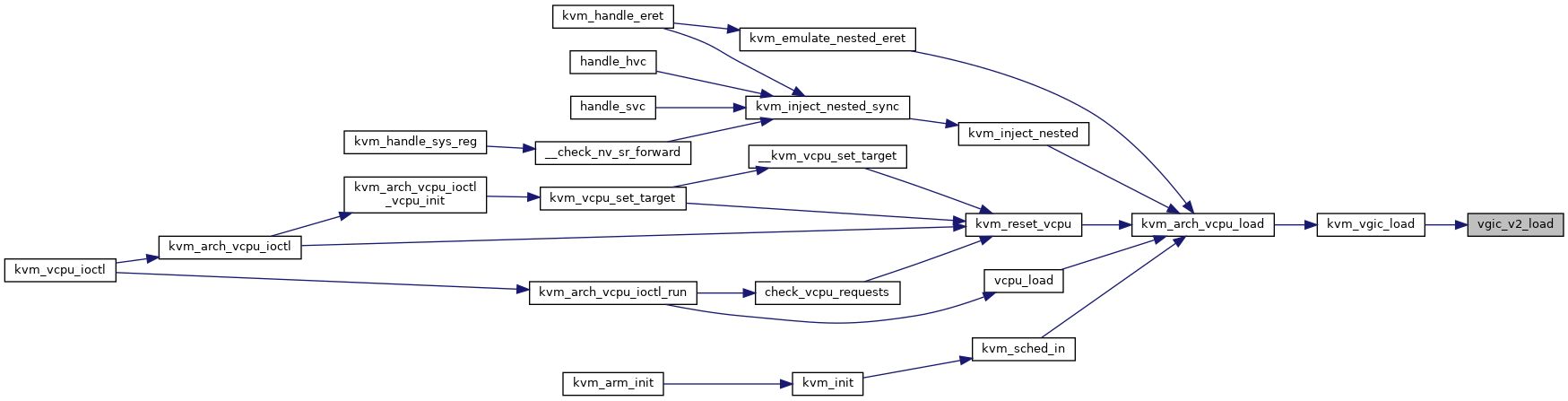

◆ vgic_v2_load()

| void vgic_v2_load | ( | struct kvm_vcpu * | vcpu | ) |

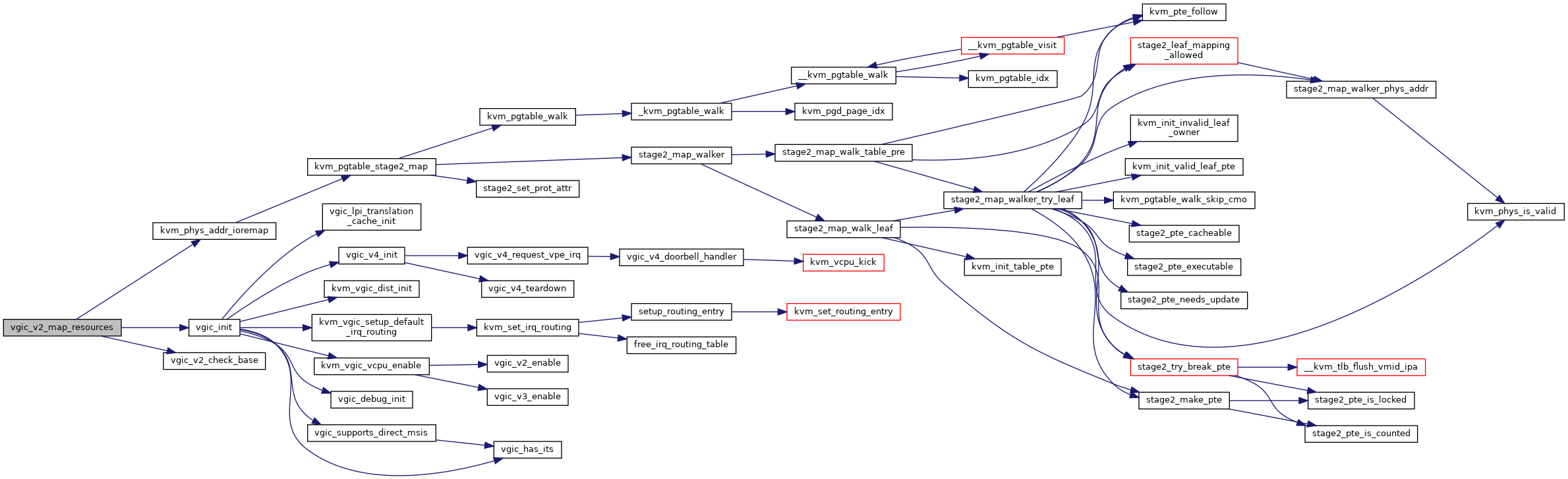

◆ vgic_v2_map_resources()

| int vgic_v2_map_resources | ( | struct kvm * | kvm | ) |

Definition at line 289 of file vgic-v2.c.

struct static_key_false vgic_v2_cpuif_trap

int kvm_phys_addr_ioremap(struct kvm *kvm, phys_addr_t guest_ipa, phys_addr_t pa, unsigned long size, bool writable)

Definition: mmu.c:1066

Definition: arm_vgic.h:224

static bool vgic_v2_check_base(gpa_t dist_base, gpa_t cpu_base)

Definition: vgic-v2.c:274

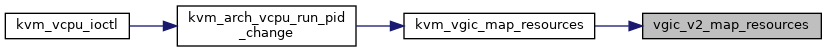

Here is the call graph for this function:

Here is the caller graph for this function:

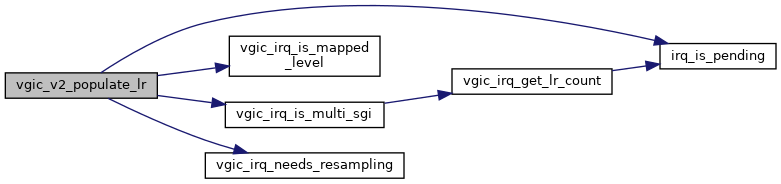

◆ vgic_v2_populate_lr()

| void vgic_v2_populate_lr | ( | struct kvm_vcpu * | vcpu, |

| struct vgic_irq * | irq, | ||

| int | lr | ||

| ) |

Definition at line 122 of file vgic-v2.c.

static bool vgic_irq_needs_resampling(struct vgic_irq *irq)

Definition: arm_vgic.h:160

static bool vgic_irq_is_mapped_level(struct vgic_irq *irq)

Definition: vgic.h:116

Here is the call graph for this function:

Here is the caller graph for this function:

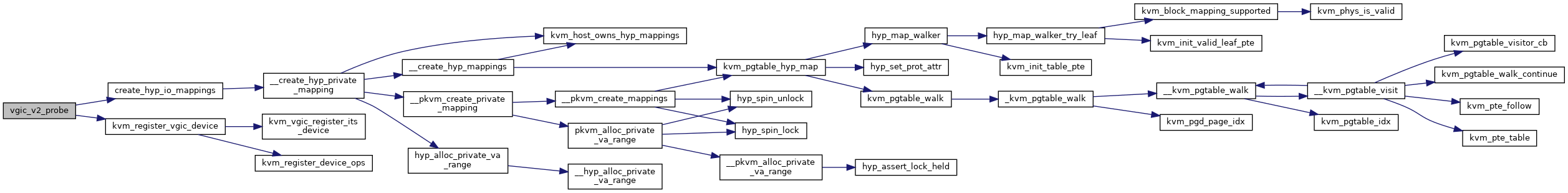

◆ vgic_v2_probe()

| int vgic_v2_probe | ( | const struct gic_kvm_info * | info | ) |

vgic_v2_probe - probe for a VGICv2 compatible interrupt controller @info: pointer to the GIC description

Returns 0 if the VGICv2 has been probed successfully, returns an error code otherwise

Definition at line 337 of file vgic-v2.c.

int create_hyp_io_mappings(phys_addr_t phys_addr, size_t size, void __iomem **kaddr, void __iomem **haddr)

Definition: mmu.c:740

int kvm_register_vgic_device(unsigned long type)

Definition: vgic-kvm-device.c:316

Here is the call graph for this function:

Here is the caller graph for this function:

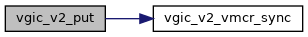

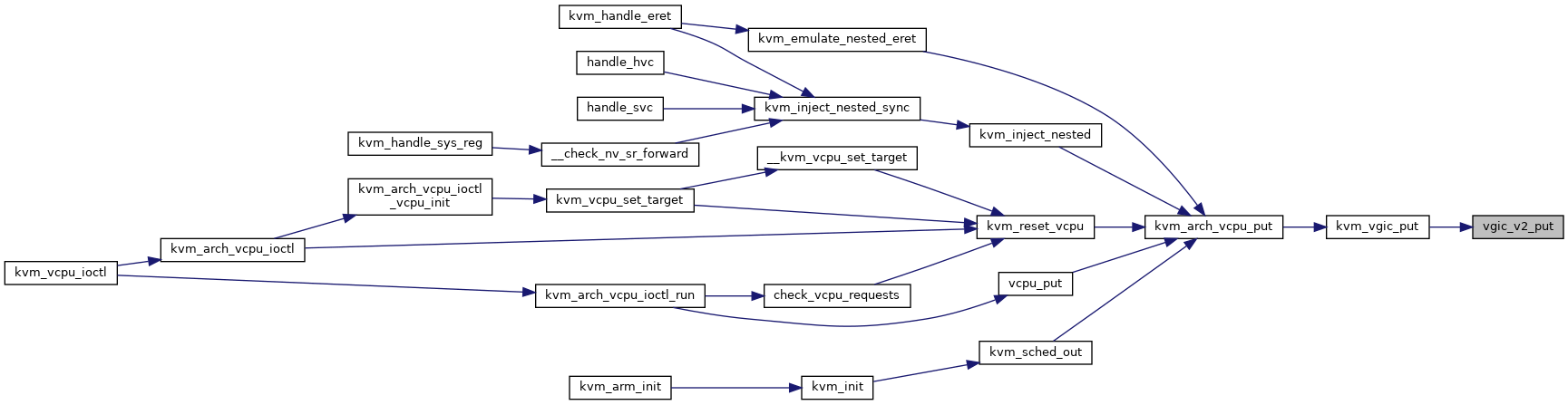

◆ vgic_v2_put()

| void vgic_v2_put | ( | struct kvm_vcpu * | vcpu | ) |

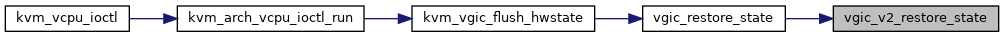

◆ vgic_v2_restore_state()

| void vgic_v2_restore_state | ( | struct kvm_vcpu * | vcpu | ) |

◆ vgic_v2_save_state()

| void vgic_v2_save_state | ( | struct kvm_vcpu * | vcpu | ) |

◆ vgic_v2_set_underflow()

| void vgic_v2_set_underflow | ( | struct kvm_vcpu * | vcpu | ) |

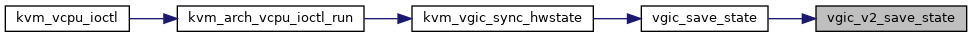

◆ vgic_v2_set_vmcr()

| void vgic_v2_set_vmcr | ( | struct kvm_vcpu * | vcpu, |

| struct vgic_vmcr * | vmcrp | ||

| ) |

◆ vgic_v2_vmcr_sync()

| void vgic_v2_vmcr_sync | ( | struct kvm_vcpu * | vcpu | ) |