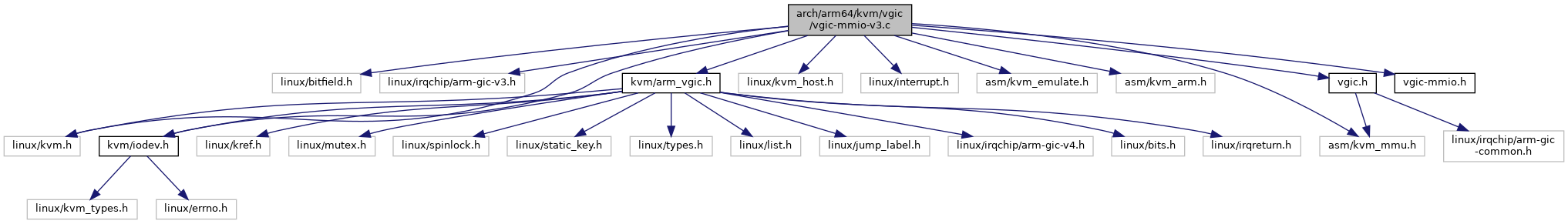

#include <linux/bitfield.h>#include <linux/irqchip/arm-gic-v3.h>#include <linux/kvm.h>#include <linux/kvm_host.h>#include <linux/interrupt.h>#include <kvm/iodev.h>#include <kvm/arm_vgic.h>#include <asm/kvm_emulate.h>#include <asm/kvm_arm.h>#include <asm/kvm_mmu.h>#include "vgic.h"#include "vgic-mmio.h"

Go to the source code of this file.

Macros | |

| #define | PROPBASER_RES0_MASK (GENMASK_ULL(63, 59) | GENMASK_ULL(55, 52) | GENMASK_ULL(6, 5)) |

| #define | PENDBASER_RES0_MASK |

| #define | REGISTER_DESC_WITH_BITS_PER_IRQ_SHARED(off, rd, wr, ur, uw, bpi, acc) |

| #define | SGI_AFFINITY_LEVEL(reg, level) |

Functions | |

| unsigned long | extract_bytes (u64 data, unsigned int offset, unsigned int num) |

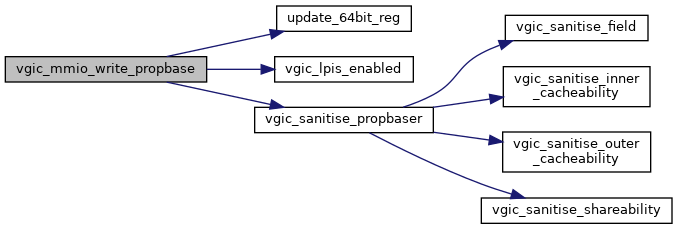

| u64 | update_64bit_reg (u64 reg, unsigned int offset, unsigned int len, unsigned long val) |

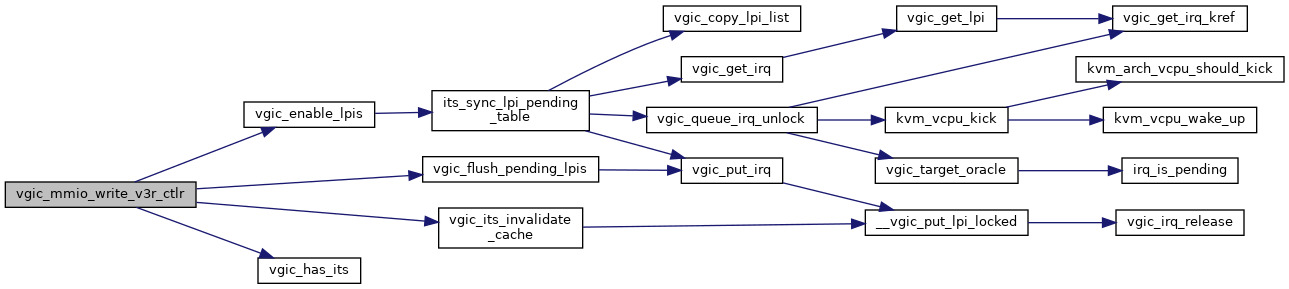

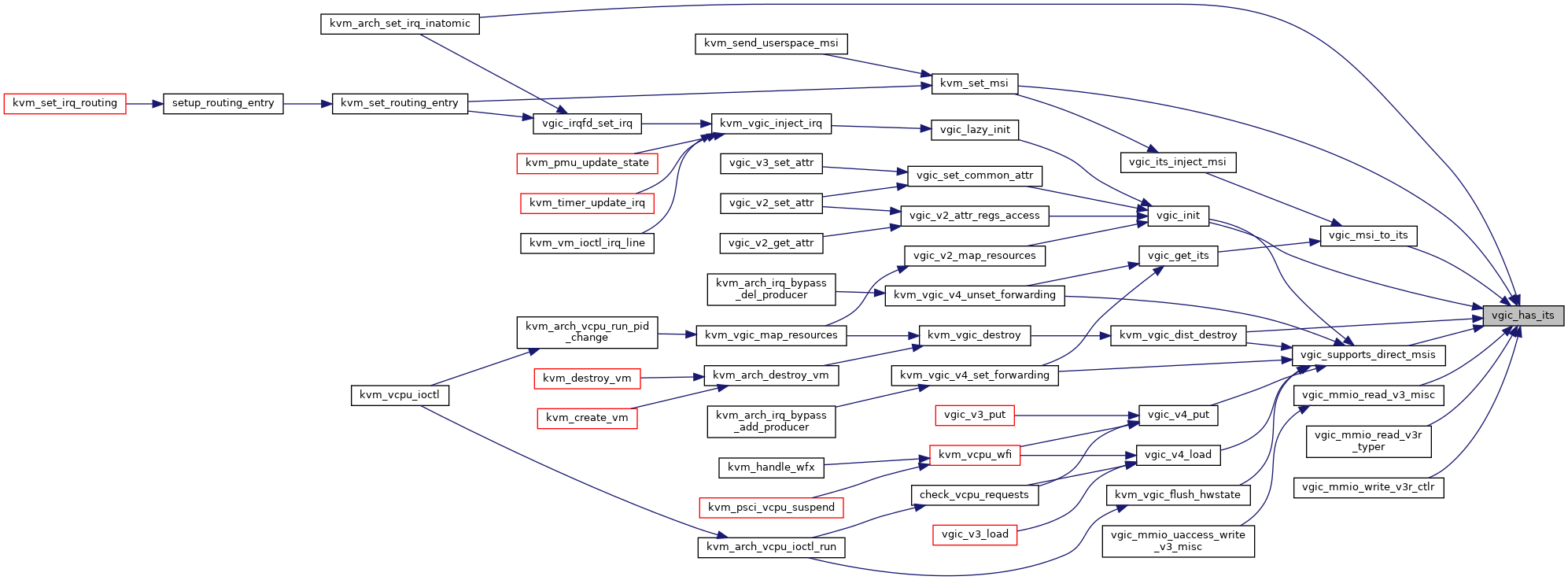

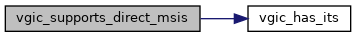

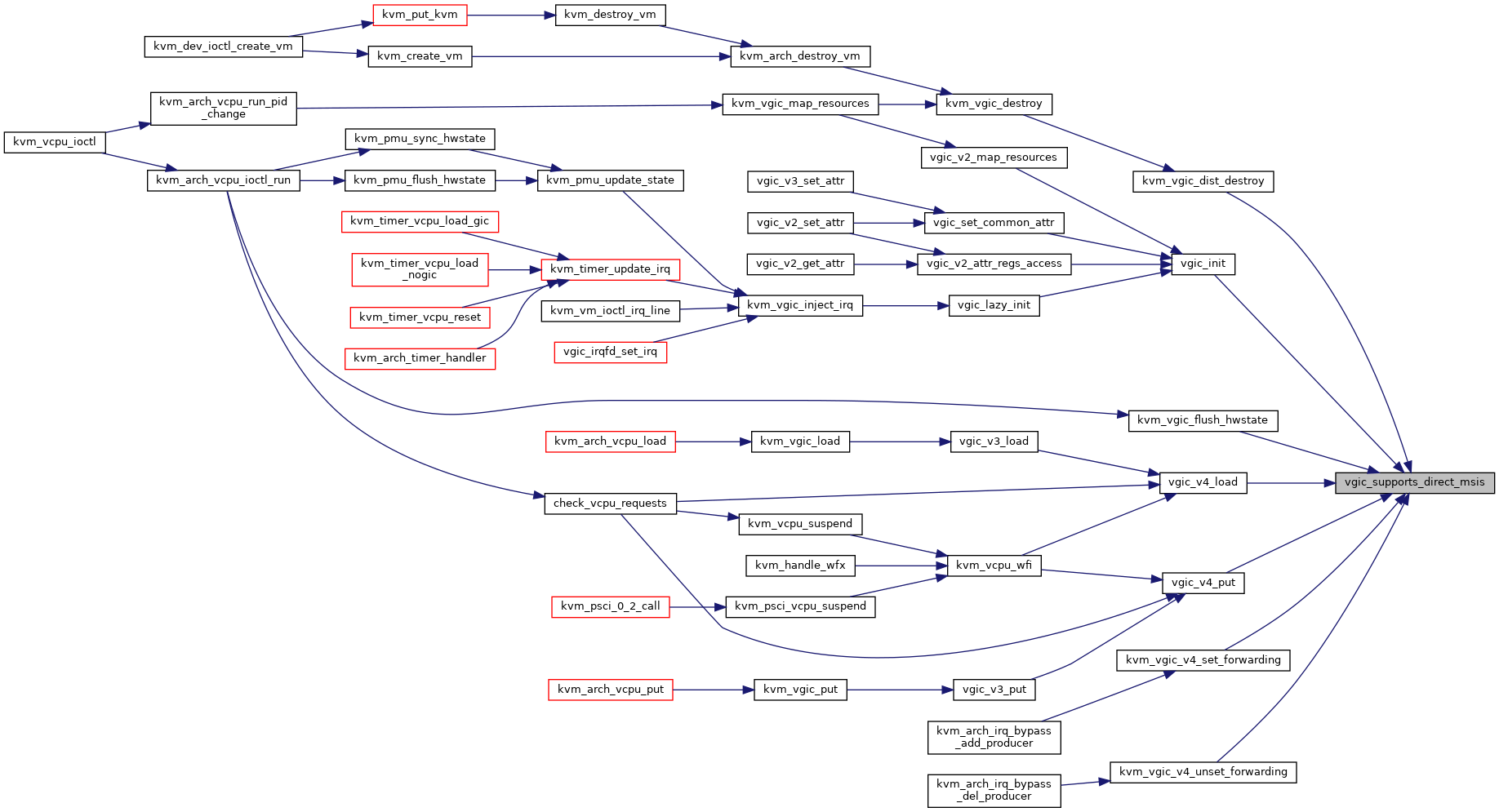

| bool | vgic_has_its (struct kvm *kvm) |

| bool | vgic_supports_direct_msis (struct kvm *kvm) |

| static unsigned long | vgic_mmio_read_v3_misc (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

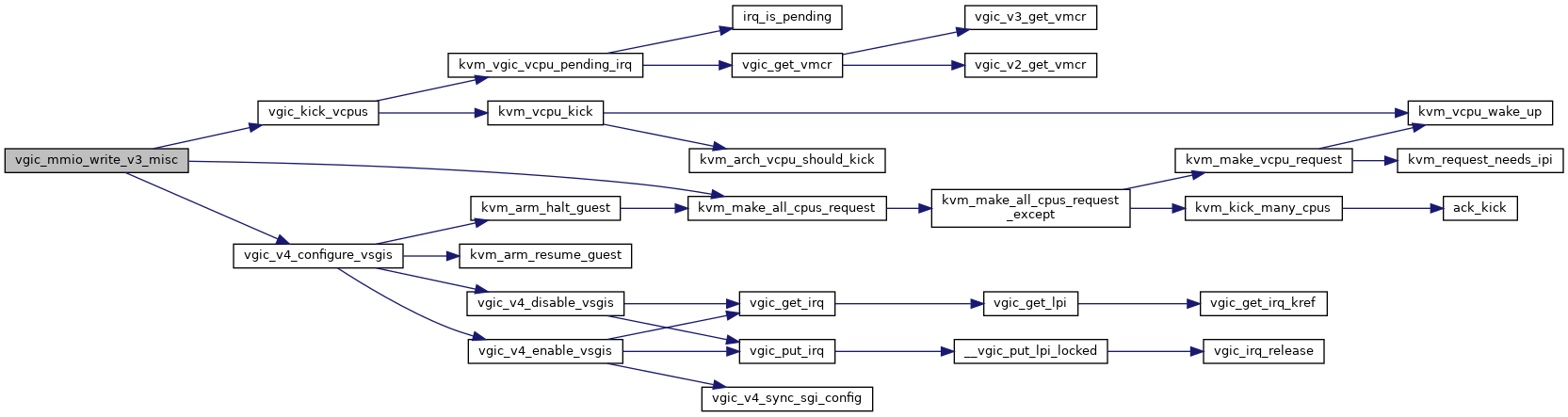

| static void | vgic_mmio_write_v3_misc (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

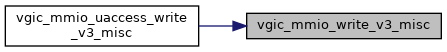

| static int | vgic_mmio_uaccess_write_v3_misc (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

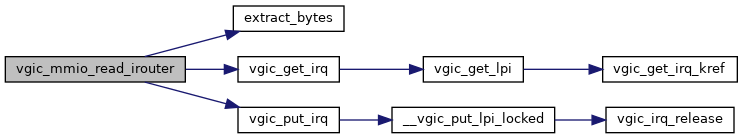

| static unsigned long | vgic_mmio_read_irouter (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static void | vgic_mmio_write_irouter (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

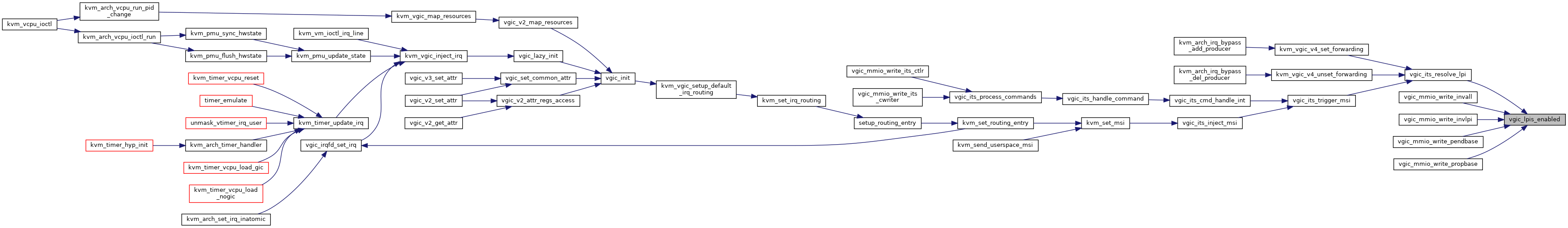

| bool | vgic_lpis_enabled (struct kvm_vcpu *vcpu) |

| static unsigned long | vgic_mmio_read_v3r_ctlr (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static void | vgic_mmio_write_v3r_ctlr (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

| static bool | vgic_mmio_vcpu_rdist_is_last (struct kvm_vcpu *vcpu) |

| static unsigned long | vgic_mmio_read_v3r_typer (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static unsigned long | vgic_mmio_read_v3r_iidr (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static unsigned long | vgic_mmio_read_v3_idregs (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static int | vgic_v3_uaccess_write_pending (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

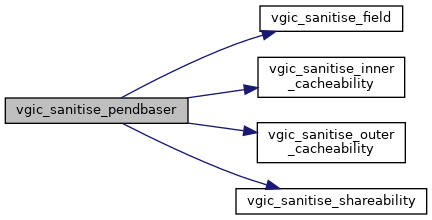

| u64 | vgic_sanitise_shareability (u64 field) |

| u64 | vgic_sanitise_inner_cacheability (u64 field) |

| u64 | vgic_sanitise_outer_cacheability (u64 field) |

| u64 | vgic_sanitise_field (u64 reg, u64 field_mask, int field_shift, u64(*sanitise_fn)(u64)) |

| static u64 | vgic_sanitise_pendbaser (u64 reg) |

| static u64 | vgic_sanitise_propbaser (u64 reg) |

| static unsigned long | vgic_mmio_read_propbase (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static void | vgic_mmio_write_propbase (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

| static unsigned long | vgic_mmio_read_pendbase (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static void | vgic_mmio_write_pendbase (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

| static unsigned long | vgic_mmio_read_sync (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len) |

| static void | vgic_set_rdist_busy (struct kvm_vcpu *vcpu, bool busy) |

| static void | vgic_mmio_write_invlpi (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

| static void | vgic_mmio_write_invall (struct kvm_vcpu *vcpu, gpa_t addr, unsigned int len, unsigned long val) |

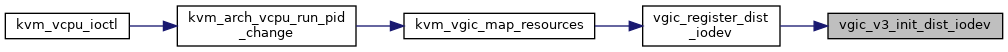

| unsigned int | vgic_v3_init_dist_iodev (struct vgic_io_device *dev) |

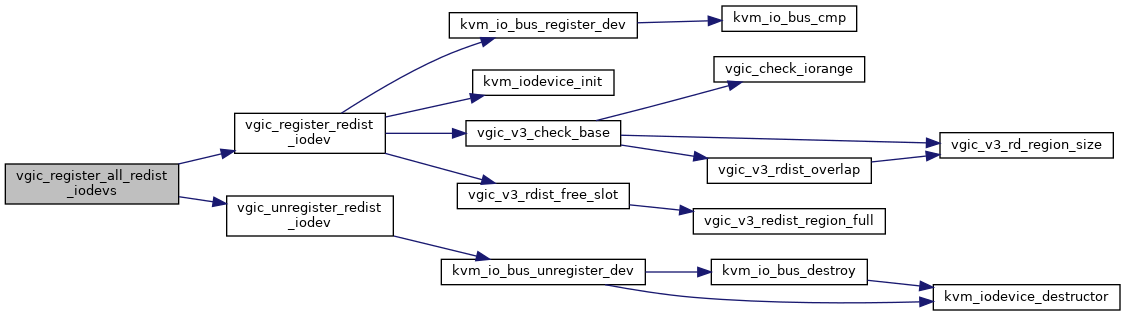

| int | vgic_register_redist_iodev (struct kvm_vcpu *vcpu) |

| void | vgic_unregister_redist_iodev (struct kvm_vcpu *vcpu) |

| static int | vgic_register_all_redist_iodevs (struct kvm *kvm) |

| static int | vgic_v3_alloc_redist_region (struct kvm *kvm, uint32_t index, gpa_t base, uint32_t count) |

| void | vgic_v3_free_redist_region (struct vgic_redist_region *rdreg) |

| int | vgic_v3_set_redist_base (struct kvm *kvm, u32 index, u64 addr, u32 count) |

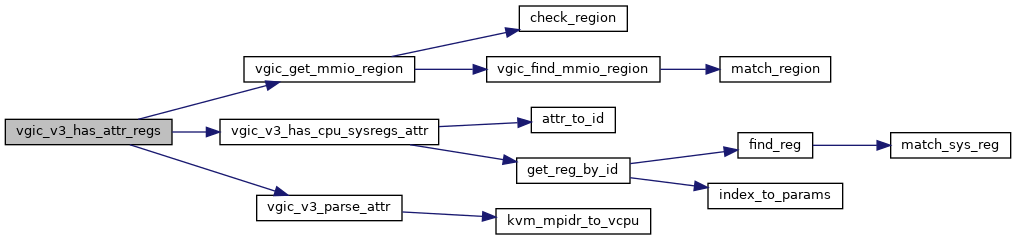

| int | vgic_v3_has_attr_regs (struct kvm_device *dev, struct kvm_device_attr *attr) |

| static void | vgic_v3_queue_sgi (struct kvm_vcpu *vcpu, u32 sgi, bool allow_group1) |

| void | vgic_v3_dispatch_sgi (struct kvm_vcpu *vcpu, u64 reg, bool allow_group1) |

| int | vgic_v3_dist_uaccess (struct kvm_vcpu *vcpu, bool is_write, int offset, u32 *val) |

| int | vgic_v3_redist_uaccess (struct kvm_vcpu *vcpu, bool is_write, int offset, u32 *val) |

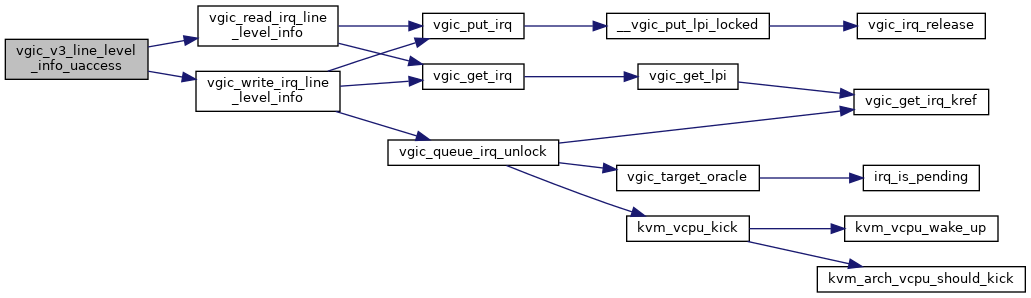

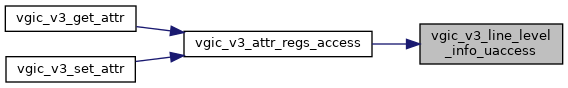

| int | vgic_v3_line_level_info_uaccess (struct kvm_vcpu *vcpu, bool is_write, u32 intid, u32 *val) |

Variables | |

| static const struct vgic_register_region | vgic_v3_dist_registers [] |

| static const struct vgic_register_region | vgic_v3_rd_registers [] |

Macro Definition Documentation

◆ PENDBASER_RES0_MASK

| #define PENDBASER_RES0_MASK |

Definition at line 415 of file vgic-mmio-v3.c.

◆ PROPBASER_RES0_MASK

| #define PROPBASER_RES0_MASK (GENMASK_ULL(63, 59) | GENMASK_ULL(55, 52) | GENMASK_ULL(6, 5)) |

Definition at line 413 of file vgic-mmio-v3.c.

◆ REGISTER_DESC_WITH_BITS_PER_IRQ_SHARED

| #define REGISTER_DESC_WITH_BITS_PER_IRQ_SHARED | ( | off, | |

| rd, | |||

| wr, | |||

| ur, | |||

| uw, | |||

| bpi, | |||

| acc | |||

| ) |

Definition at line 575 of file vgic-mmio-v3.c.

◆ SGI_AFFINITY_LEVEL

| #define SGI_AFFINITY_LEVEL | ( | reg, | |

| level | |||

| ) |

Definition at line 1006 of file vgic-mmio-v3.c.

Function Documentation

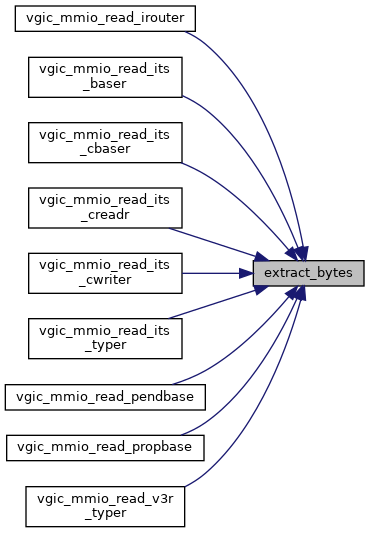

◆ extract_bytes()

| unsigned long extract_bytes | ( | u64 | data, |

| unsigned int | offset, | ||

| unsigned int | num | ||

| ) |

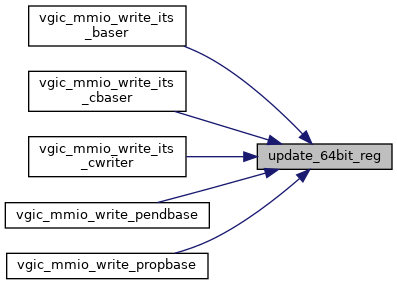

◆ update_64bit_reg()

| u64 update_64bit_reg | ( | u64 | reg, |

| unsigned int | offset, | ||

| unsigned int | len, | ||

| unsigned long | val | ||

| ) |

◆ vgic_has_its()

| bool vgic_has_its | ( | struct kvm * | kvm | ) |

Definition at line 41 of file vgic-mmio-v3.c.

◆ vgic_lpis_enabled()

| bool vgic_lpis_enabled | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 238 of file vgic-mmio-v3.c.

◆ vgic_mmio_read_irouter()

|

static |

Definition at line 193 of file vgic-mmio-v3.c.

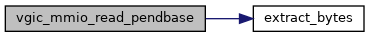

◆ vgic_mmio_read_pendbase()

|

static |

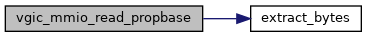

◆ vgic_mmio_read_propbase()

|

static |

◆ vgic_mmio_read_sync()

|

static |

Definition at line 511 of file vgic-mmio-v3.c.

◆ vgic_mmio_read_v3_idregs()

|

static |

Definition at line 344 of file vgic-mmio-v3.c.

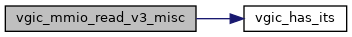

◆ vgic_mmio_read_v3_misc()

|

static |

Definition at line 64 of file vgic-mmio-v3.c.

◆ vgic_mmio_read_v3r_ctlr()

|

static |

Definition at line 245 of file vgic-mmio-v3.c.

◆ vgic_mmio_read_v3r_iidr()

|

static |

Definition at line 338 of file vgic-mmio-v3.c.

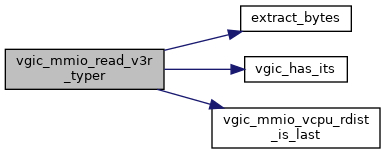

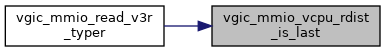

◆ vgic_mmio_read_v3r_typer()

|

static |

Definition at line 319 of file vgic-mmio-v3.c.

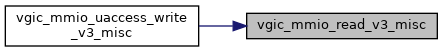

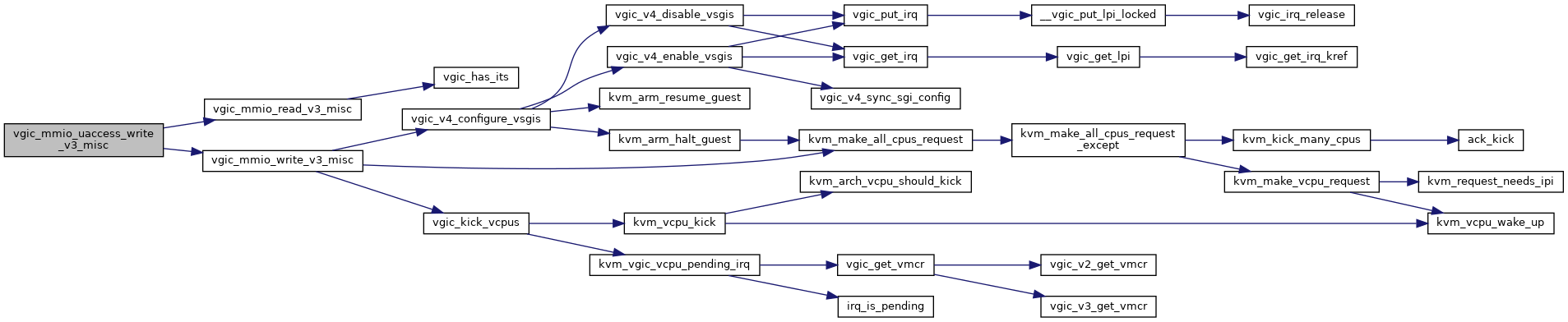

◆ vgic_mmio_uaccess_write_v3_misc()

|

static |

Definition at line 153 of file vgic-mmio-v3.c.

◆ vgic_mmio_vcpu_rdist_is_last()

|

static |

Definition at line 292 of file vgic-mmio-v3.c.

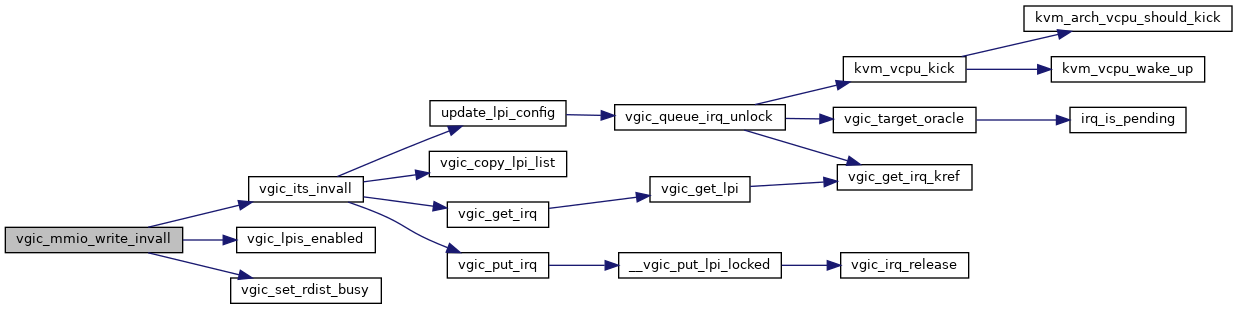

◆ vgic_mmio_write_invall()

|

static |

Definition at line 555 of file vgic-mmio-v3.c.

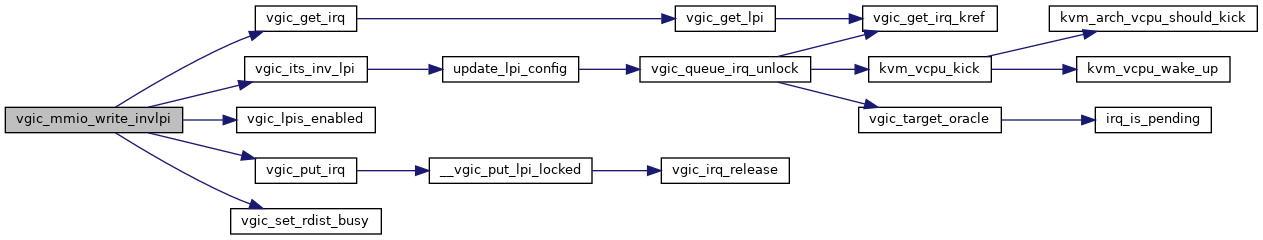

◆ vgic_mmio_write_invlpi()

|

static |

Definition at line 528 of file vgic-mmio-v3.c.

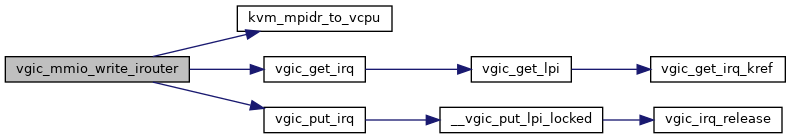

◆ vgic_mmio_write_irouter()

|

static |

Definition at line 211 of file vgic-mmio-v3.c.

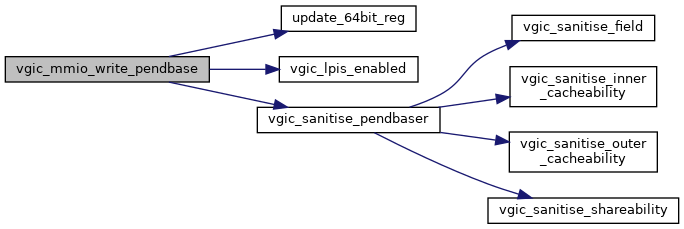

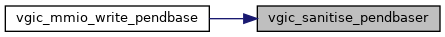

◆ vgic_mmio_write_pendbase()

|

static |

Definition at line 491 of file vgic-mmio-v3.c.

◆ vgic_mmio_write_propbase()

|

static |

◆ vgic_mmio_write_v3_misc()

|

static |

Definition at line 104 of file vgic-mmio-v3.c.

◆ vgic_mmio_write_v3r_ctlr()

|

static |

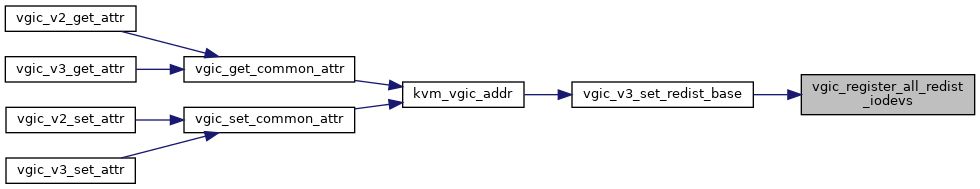

◆ vgic_register_all_redist_iodevs()

|

static |

Definition at line 812 of file vgic-mmio-v3.c.

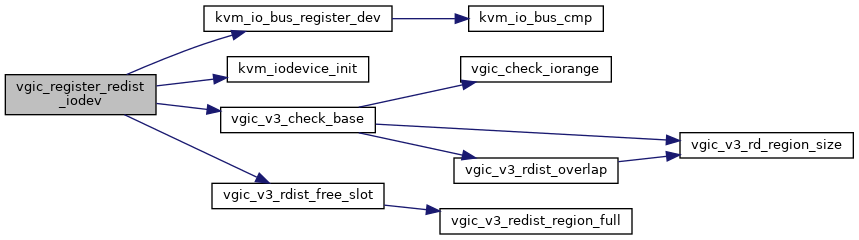

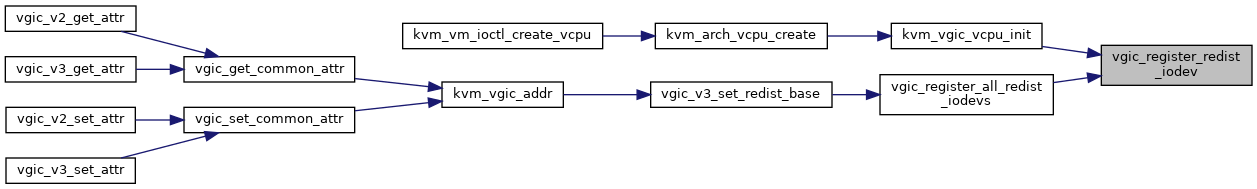

◆ vgic_register_redist_iodev()

| int vgic_register_redist_iodev | ( | struct kvm_vcpu * | vcpu | ) |

vgic_register_redist_iodev - register a single redist iodev @vcpu: The VCPU to which the redistributor belongs

Register a KVM iodev for this VCPU's redistributor using the address provided.

Return 0 on success, -ERRNO otherwise.

Definition at line 746 of file vgic-mmio-v3.c.

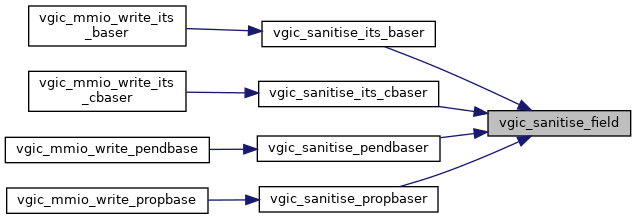

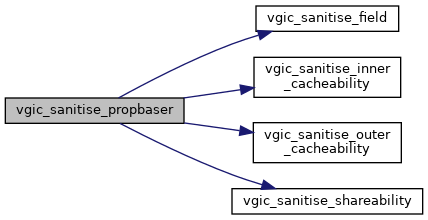

◆ vgic_sanitise_field()

| u64 vgic_sanitise_field | ( | u64 | reg, |

| u64 | field_mask, | ||

| int | field_shift, | ||

| u64(*)(u64) | sanitise_fn | ||

| ) |

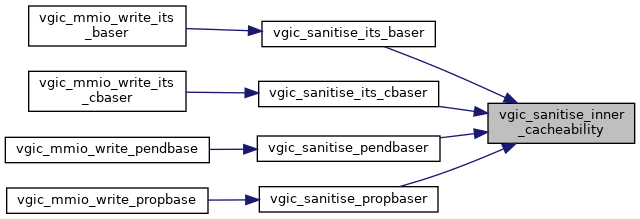

◆ vgic_sanitise_inner_cacheability()

| u64 vgic_sanitise_inner_cacheability | ( | u64 | field | ) |

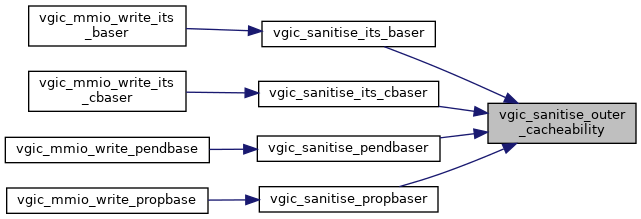

◆ vgic_sanitise_outer_cacheability()

| u64 vgic_sanitise_outer_cacheability | ( | u64 | field | ) |

◆ vgic_sanitise_pendbaser()

|

static |

Definition at line 419 of file vgic-mmio-v3.c.

◆ vgic_sanitise_propbaser()

|

static |

Definition at line 436 of file vgic-mmio-v3.c.

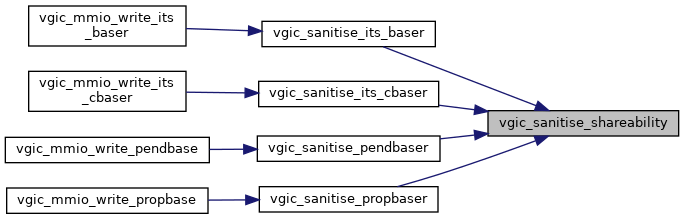

◆ vgic_sanitise_shareability()

| u64 vgic_sanitise_shareability | ( | u64 | field | ) |

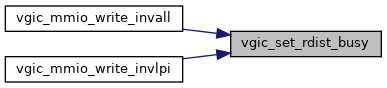

◆ vgic_set_rdist_busy()

|

static |

◆ vgic_supports_direct_msis()

| bool vgic_supports_direct_msis | ( | struct kvm * | kvm | ) |

Definition at line 51 of file vgic-mmio-v3.c.

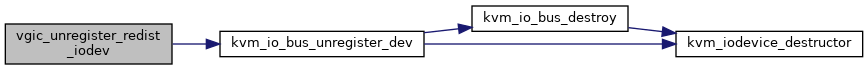

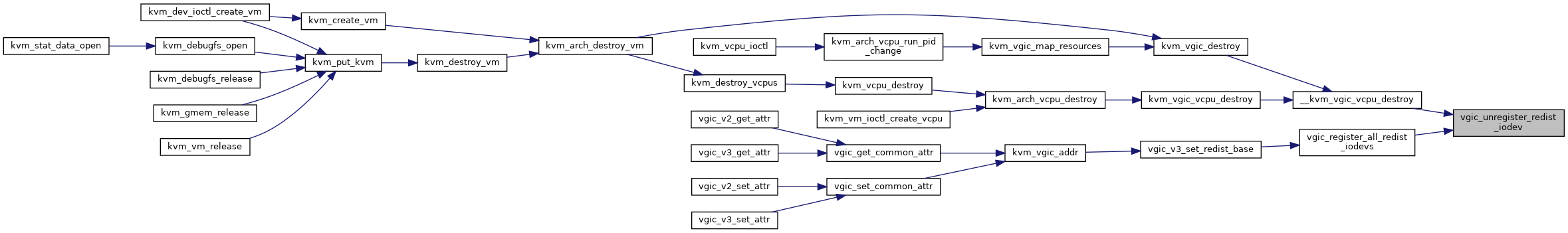

◆ vgic_unregister_redist_iodev()

| void vgic_unregister_redist_iodev | ( | struct kvm_vcpu * | vcpu | ) |

Definition at line 805 of file vgic-mmio-v3.c.

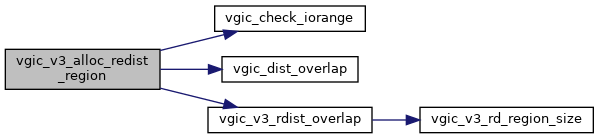

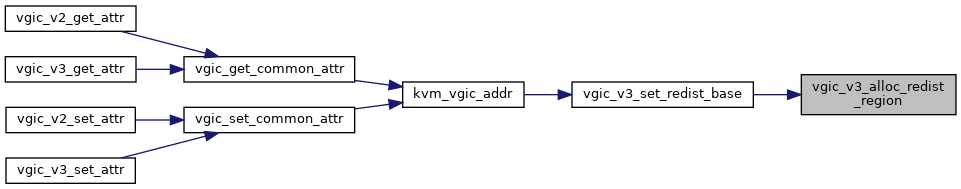

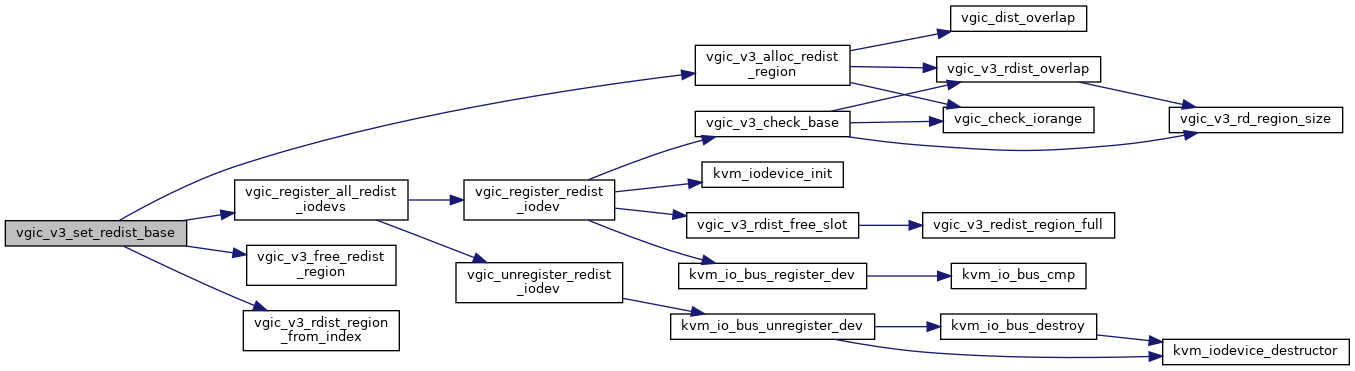

◆ vgic_v3_alloc_redist_region()

|

static |

vgic_v3_alloc_redist_region - Allocate a new redistributor region

Performs various checks before inserting the rdist region in the list. Those tests depend on whether the size of the rdist region is known (ie. count != 0). The list is sorted by rdist region index.

@kvm: kvm handle @index: redist region index @base: base of the new rdist region @count: number of redistributors the region is made of (0 in the old style single region, whose size is induced from the number of vcpus)

Return 0 on success, < 0 otherwise

Definition at line 854 of file vgic-mmio-v3.c.

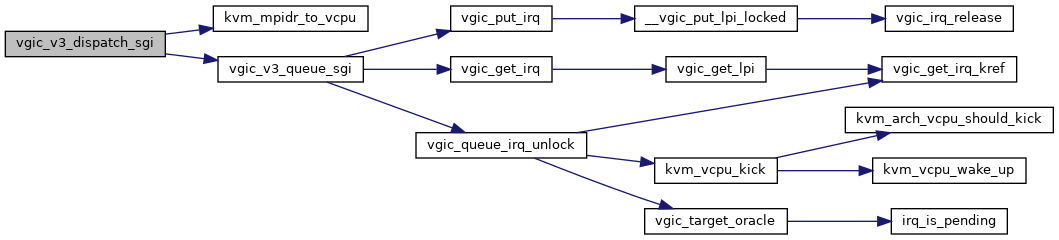

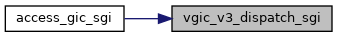

◆ vgic_v3_dispatch_sgi()

| void vgic_v3_dispatch_sgi | ( | struct kvm_vcpu * | vcpu, |

| u64 | reg, | ||

| bool | allow_group1 | ||

| ) |

vgic_v3_dispatch_sgi - handle SGI requests from VCPUs @vcpu: The VCPU requesting a SGI @reg: The value written into ICC_{ASGI1,SGI0,SGI1}R by that VCPU @allow_group1: Does the sysreg access allow generation of G1 SGIs

With GICv3 (and ARE=1) CPUs trigger SGIs by writing to a system register. This will trap in sys_regs.c and call this function. This ICC_SGI1R_EL1 register contains the upper three affinity levels of the target processors as well as a bitmask of 16 Aff0 CPUs.

If the interrupt routing mode bit is not set, we iterate over the Aff0 bits and signal the VCPUs matching the provided Aff{3,2,1}.

If this bit is set, we signal all, but not the calling VCPU.

Definition at line 1058 of file vgic-mmio-v3.c.

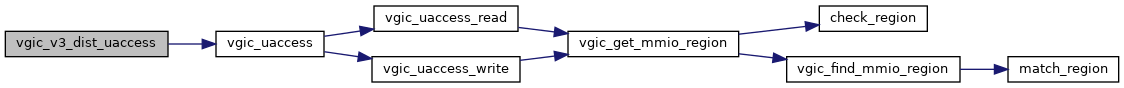

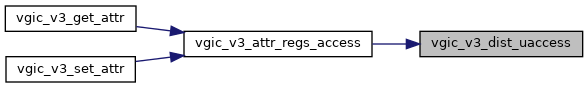

◆ vgic_v3_dist_uaccess()

| int vgic_v3_dist_uaccess | ( | struct kvm_vcpu * | vcpu, |

| bool | is_write, | ||

| int | offset, | ||

| u32 * | val | ||

| ) |

Definition at line 1095 of file vgic-mmio-v3.c.

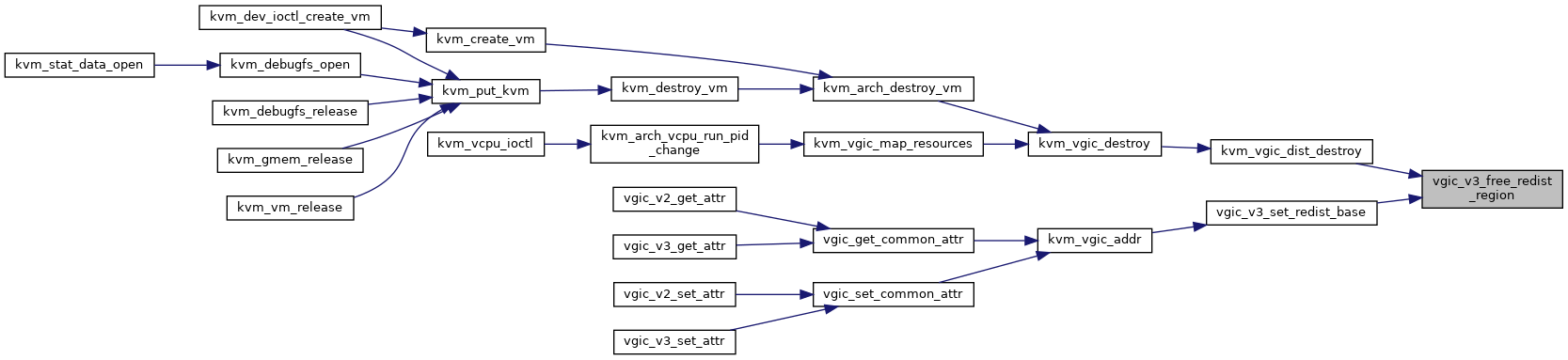

◆ vgic_v3_free_redist_region()

| void vgic_v3_free_redist_region | ( | struct vgic_redist_region * | rdreg | ) |

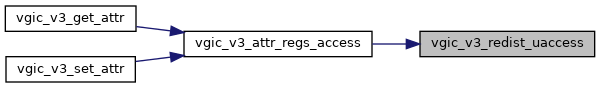

◆ vgic_v3_has_attr_regs()

| int vgic_v3_has_attr_regs | ( | struct kvm_device * | dev, |

| struct kvm_device_attr * | attr | ||

| ) |

Definition at line 956 of file vgic-mmio-v3.c.

◆ vgic_v3_init_dist_iodev()

| unsigned int vgic_v3_init_dist_iodev | ( | struct vgic_io_device * | dev | ) |

Definition at line 727 of file vgic-mmio-v3.c.

◆ vgic_v3_line_level_info_uaccess()

| int vgic_v3_line_level_info_uaccess | ( | struct kvm_vcpu * | vcpu, |

| bool | is_write, | ||

| u32 | intid, | ||

| u32 * | val | ||

| ) |

Definition at line 1117 of file vgic-mmio-v3.c.

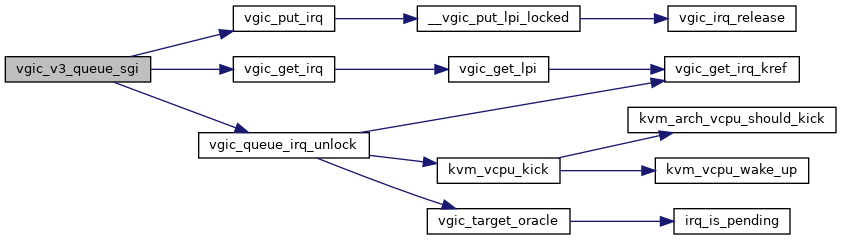

◆ vgic_v3_queue_sgi()

|

static |

Definition at line 1010 of file vgic-mmio-v3.c.

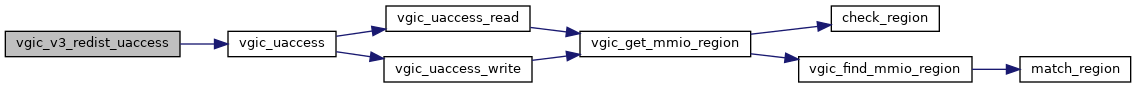

◆ vgic_v3_redist_uaccess()

| int vgic_v3_redist_uaccess | ( | struct kvm_vcpu * | vcpu, |

| bool | is_write, | ||

| int | offset, | ||

| u32 * | val | ||

| ) |

Definition at line 1106 of file vgic-mmio-v3.c.

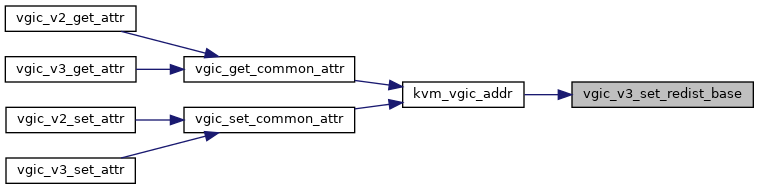

◆ vgic_v3_set_redist_base()

| int vgic_v3_set_redist_base | ( | struct kvm * | kvm, |

| u32 | index, | ||

| u64 | addr, | ||

| u32 | count | ||

| ) |

Definition at line 928 of file vgic-mmio-v3.c.

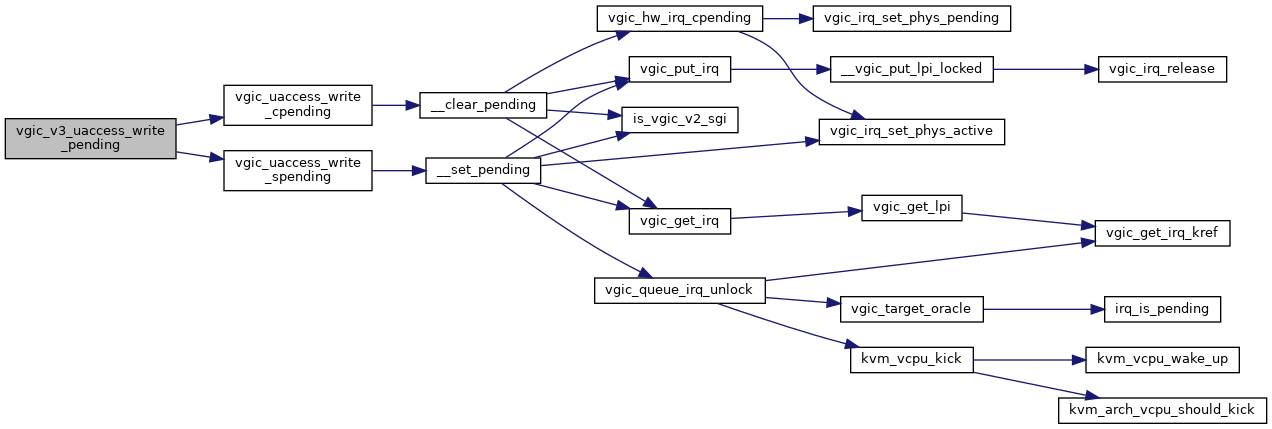

◆ vgic_v3_uaccess_write_pending()

|

static |

Definition at line 356 of file vgic-mmio-v3.c.

Variable Documentation

◆ vgic_v3_dist_registers

|

static |

Definition at line 555 of file vgic-mmio-v3.c.

◆ vgic_v3_rd_registers

|

static |

Definition at line 555 of file vgic-mmio-v3.c.