#include <linux/kvm_host.h>#include "irq.h"#include "mmu.h"#include "kvm_cache_regs.h"#include "x86.h"#include "smm.h"#include "cpuid.h"#include "pmu.h"#include <linux/module.h>#include <linux/mod_devicetable.h>#include <linux/kernel.h>#include <linux/vmalloc.h>#include <linux/highmem.h>#include <linux/amd-iommu.h>#include <linux/sched.h>#include <linux/trace_events.h>#include <linux/slab.h>#include <linux/hashtable.h>#include <linux/objtool.h>#include <linux/psp-sev.h>#include <linux/file.h>#include <linux/pagemap.h>#include <linux/swap.h>#include <linux/rwsem.h>#include <linux/cc_platform.h>#include <linux/smp.h>#include <asm/apic.h>#include <asm/perf_event.h>#include <asm/tlbflush.h>#include <asm/desc.h>#include <asm/debugreg.h>#include <asm/kvm_para.h>#include <asm/irq_remapping.h>#include <asm/spec-ctrl.h>#include <asm/cpu_device_id.h>#include <asm/traps.h>#include <asm/reboot.h>#include <asm/fpu/api.h>#include <trace/events/ipi.h>#include "trace.h"#include "svm.h"#include "svm_ops.h"#include "kvm_onhyperv.h"#include "svm_onhyperv.h"

Go to the source code of this file.

Classes | |

| struct | svm_direct_access_msrs |

| struct | __x86_intercept |

Macros | |

| #define | pr_fmt(fmt) KBUILD_MODNAME ": " fmt |

| #define | SEG_TYPE_LDT 2 |

| #define | SEG_TYPE_BUSY_TSS16 3 |

| #define | X2APIC_MSR(x) (APIC_BASE_MSR + (x >> 4)) |

| #define | NUM_MSR_MAPS ARRAY_SIZE(msrpm_ranges) |

| #define | MSRS_RANGE_SIZE 2048 |

| #define | MSRS_IN_RANGE (MSRS_RANGE_SIZE * 8 / 2) |

| #define | CR_VALID (1ULL << 63) |

| #define | PRE_EX(exit) |

| #define | POST_EX(exit) |

| #define | POST_MEM(exit) |

Enumerations | |

| enum | { NONE_SVM_INSTR , SVM_INSTR_VMRUN , SVM_INSTR_VMLOAD , SVM_INSTR_VMSAVE } |

Functions | |

| MODULE_AUTHOR ("Qumranet") | |

| MODULE_LICENSE ("GPL") | |

| static | DEFINE_PER_CPU (u64, current_tsc_ratio) |

| module_param (pause_filter_thresh, ushort, 0444) | |

| module_param (pause_filter_count, ushort, 0444) | |

| module_param (pause_filter_count_grow, ushort, 0444) | |

| module_param (pause_filter_count_shrink, ushort, 0444) | |

| module_param (pause_filter_count_max, ushort, 0444) | |

| module_param_named (npt, npt_enabled, bool, 0444) | |

| module_param (nested, int, 0444) | |

| module_param (nrips, int, 0444) | |

| module_param (vls, int, 0444) | |

| module_param (vgif, int, 0444) | |

| module_param (lbrv, int, 0444) | |

| module_param (tsc_scaling, int, 0444) | |

| module_param (avic, bool, 0444) | |

| module_param (dump_invalid_vmcb, bool, 0644) | |

| module_param (intercept_smi, bool, 0444) | |

| module_param (vnmi, bool, 0444) | |

| DEFINE_PER_CPU (struct svm_cpu_data, svm_data) | |

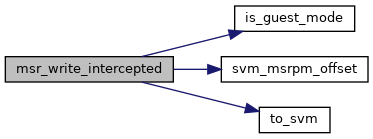

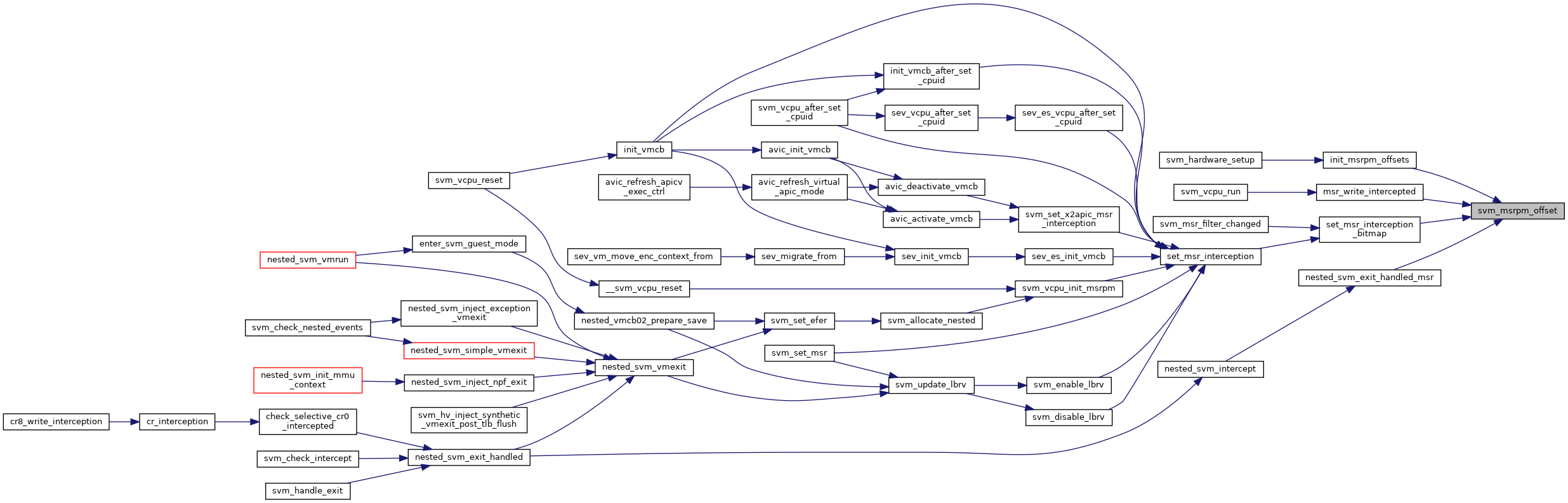

| u32 | svm_msrpm_offset (u32 msr) |

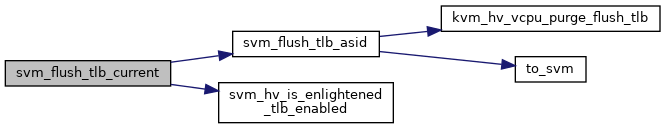

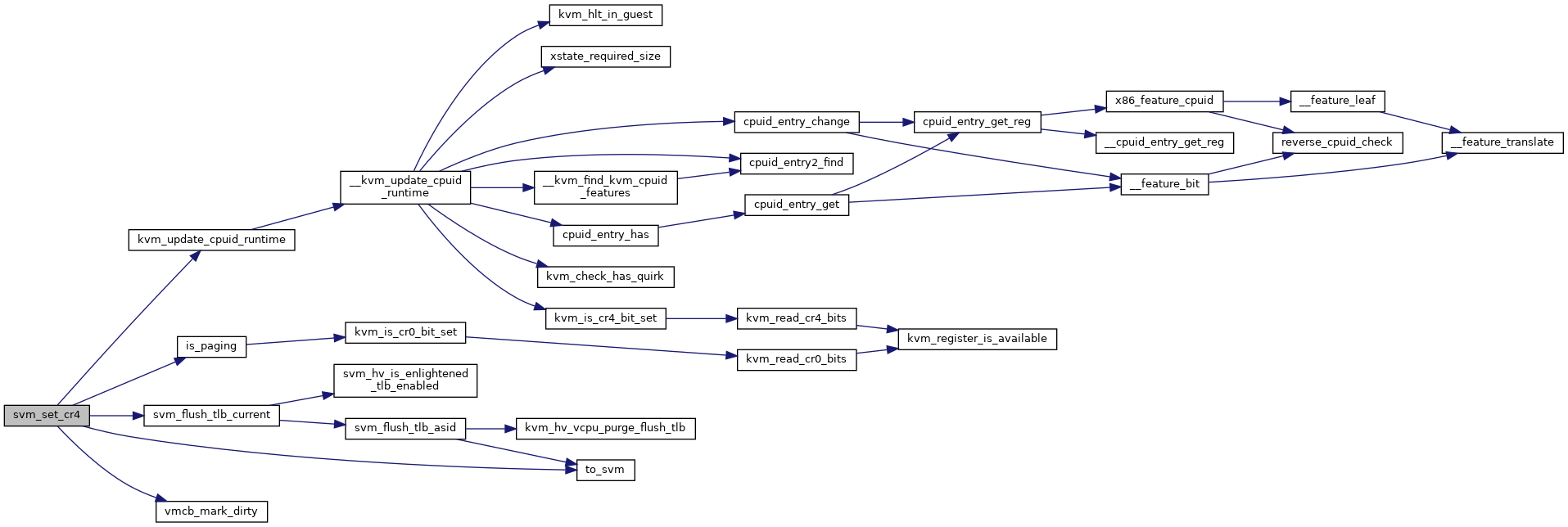

| static void | svm_flush_tlb_current (struct kvm_vcpu *vcpu) |

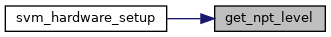

| static int | get_npt_level (void) |

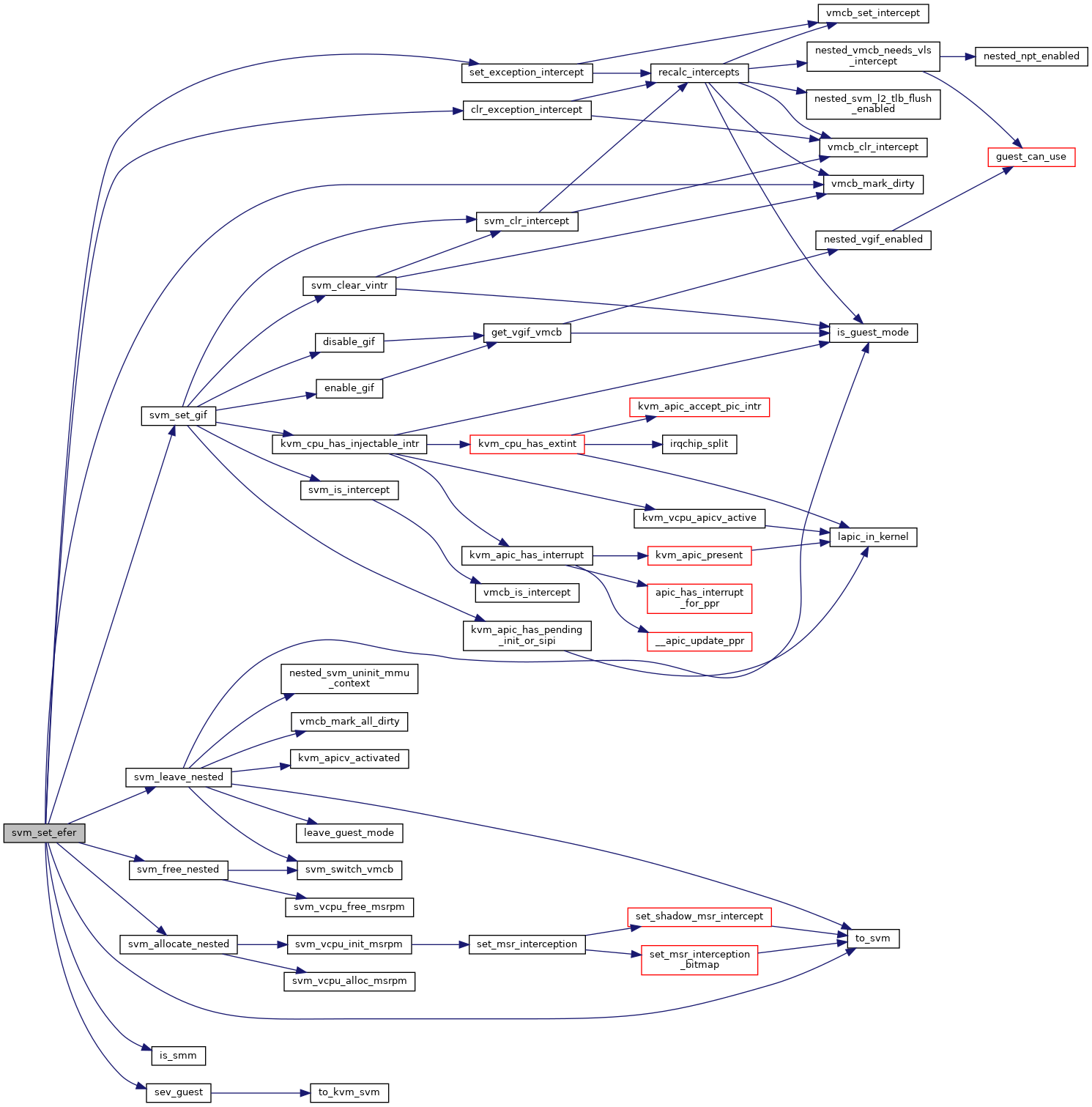

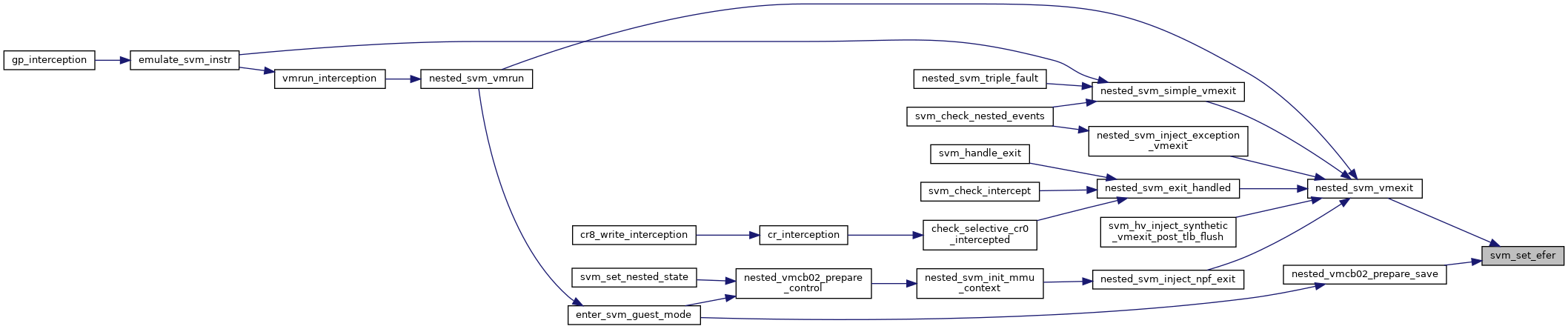

| int | svm_set_efer (struct kvm_vcpu *vcpu, u64 efer) |

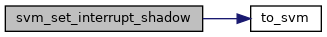

| static u32 | svm_get_interrupt_shadow (struct kvm_vcpu *vcpu) |

| static void | svm_set_interrupt_shadow (struct kvm_vcpu *vcpu, int mask) |

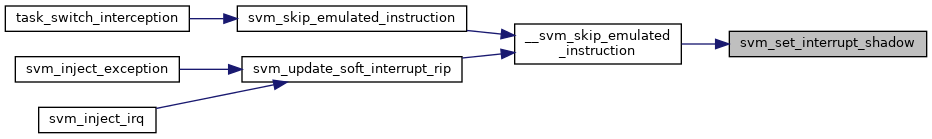

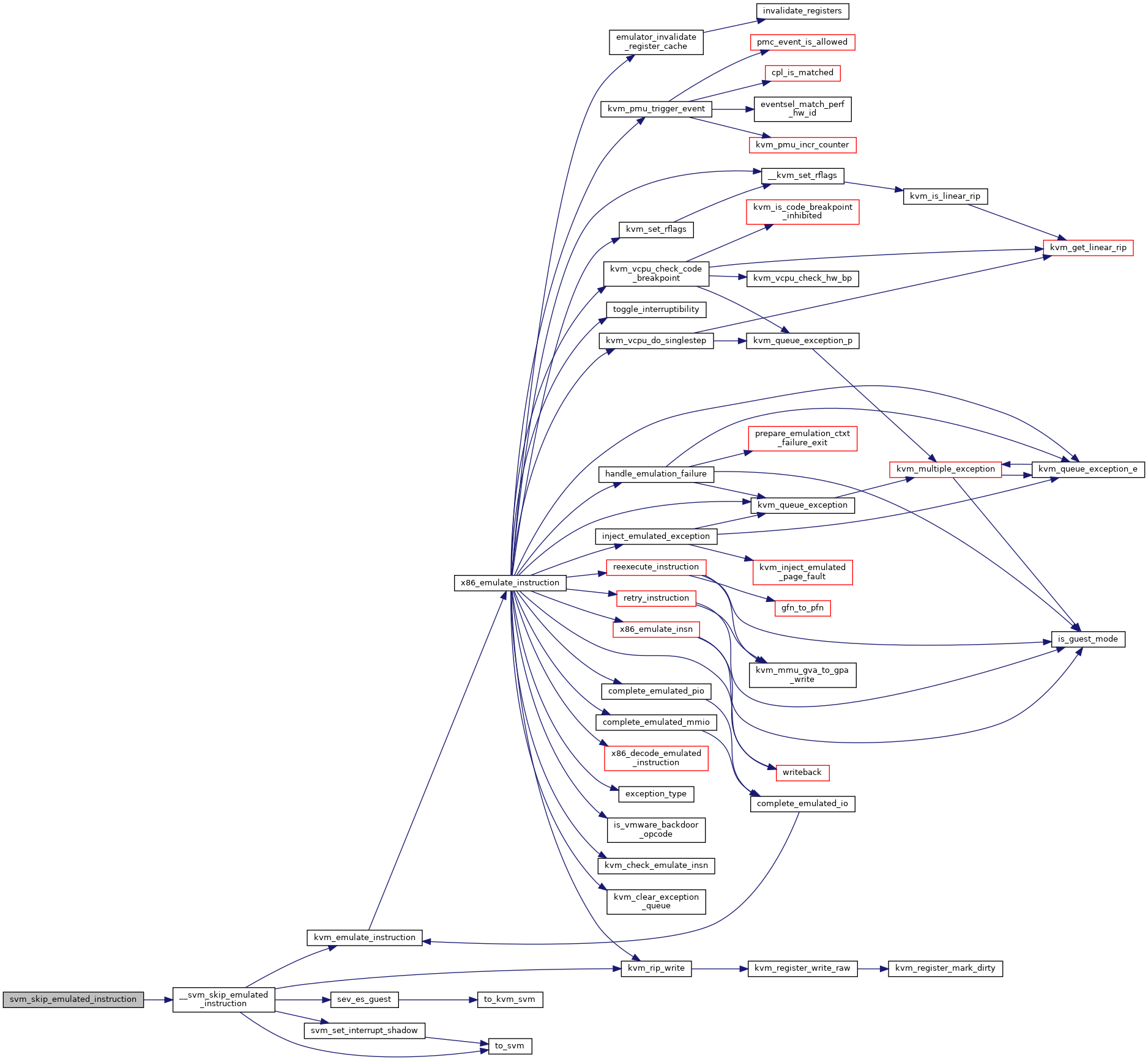

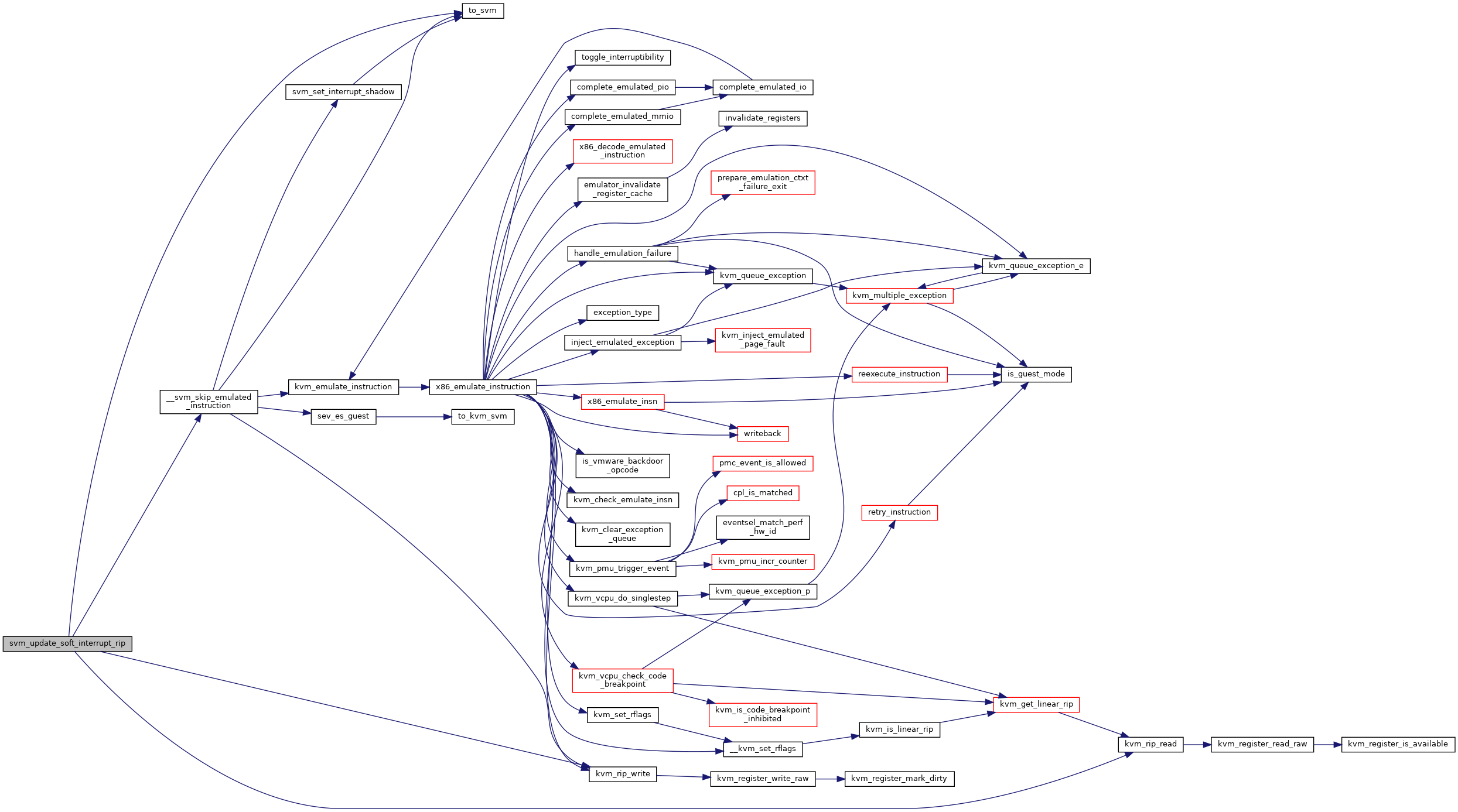

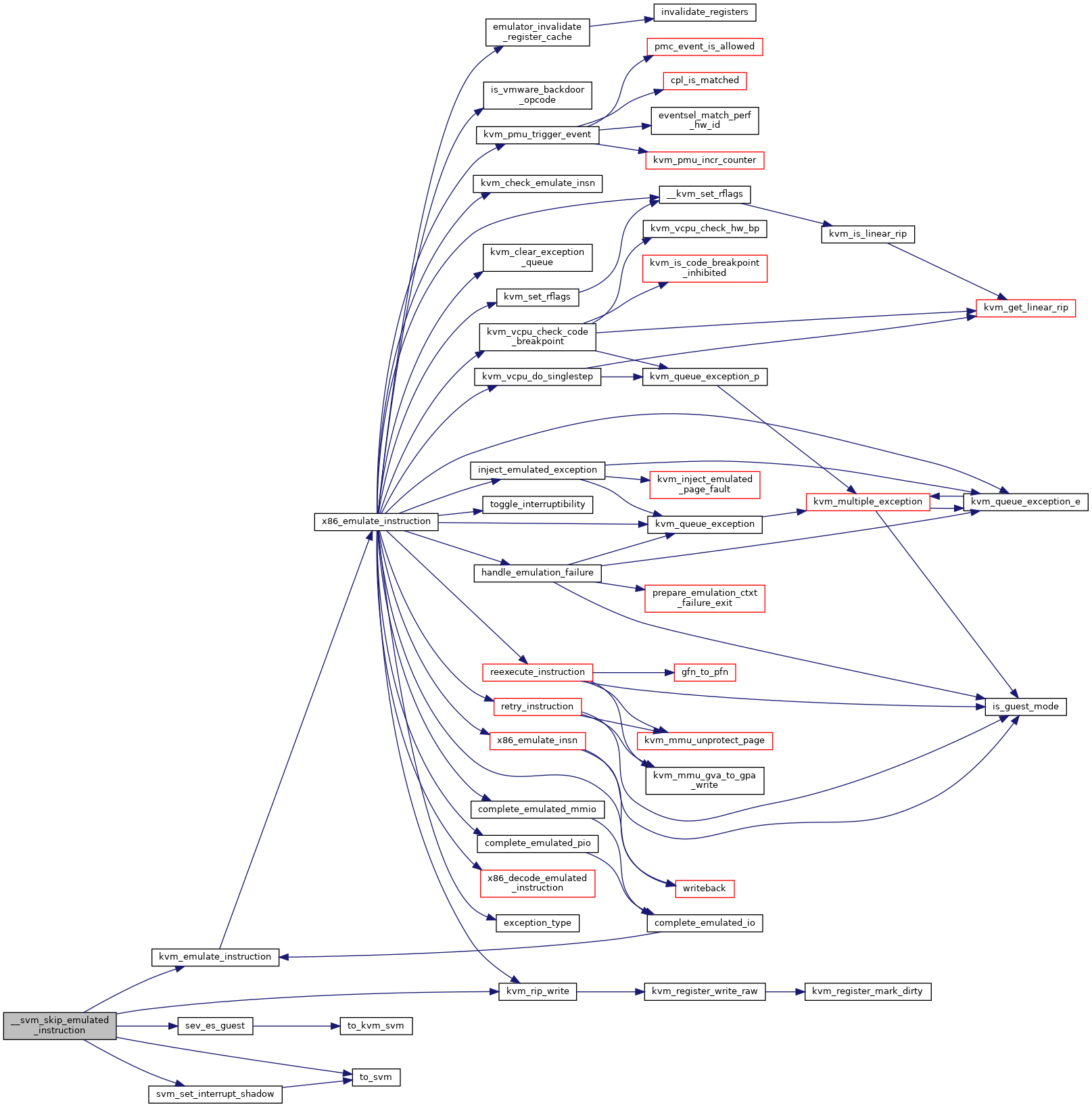

| static int | __svm_skip_emulated_instruction (struct kvm_vcpu *vcpu, bool commit_side_effects) |

| static int | svm_skip_emulated_instruction (struct kvm_vcpu *vcpu) |

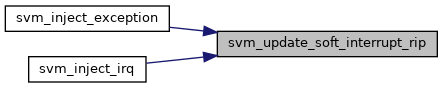

| static int | svm_update_soft_interrupt_rip (struct kvm_vcpu *vcpu) |

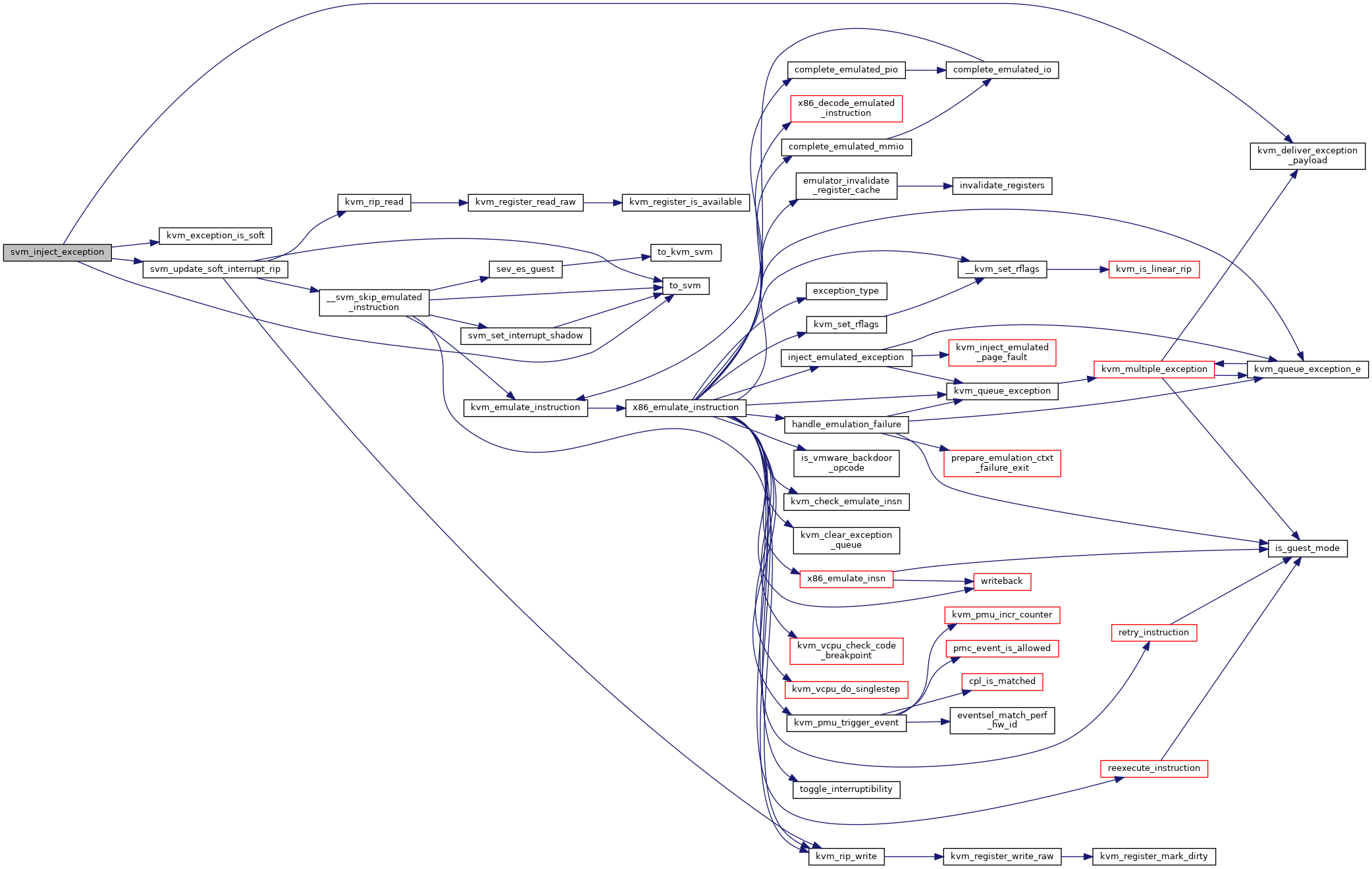

| static void | svm_inject_exception (struct kvm_vcpu *vcpu) |

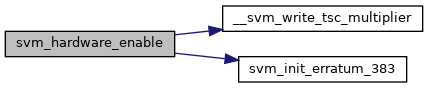

| static void | svm_init_erratum_383 (void) |

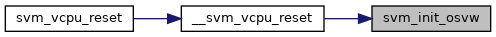

| static void | svm_init_osvw (struct kvm_vcpu *vcpu) |

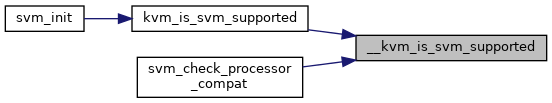

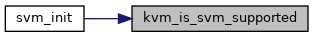

| static bool | __kvm_is_svm_supported (void) |

| static bool | kvm_is_svm_supported (void) |

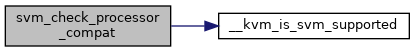

| static int | svm_check_processor_compat (void) |

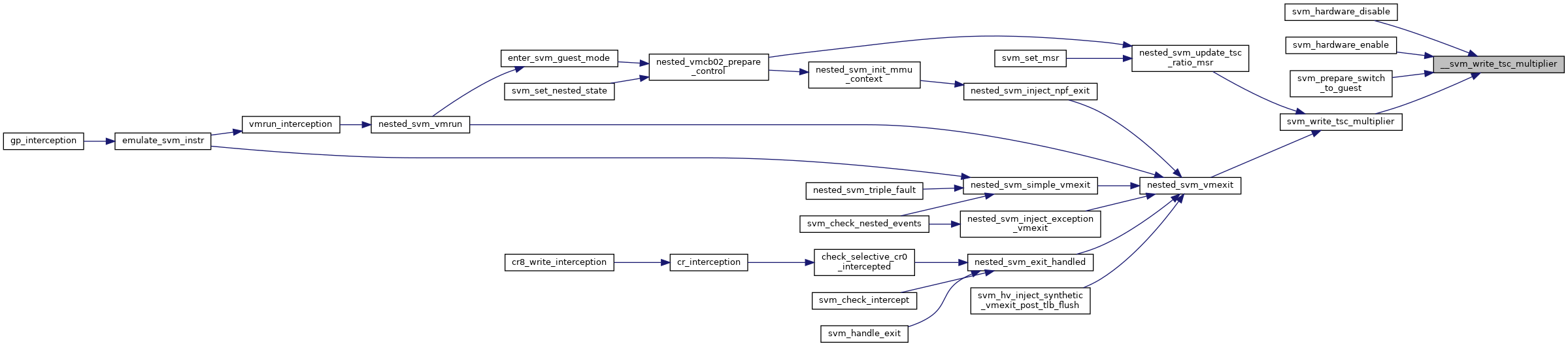

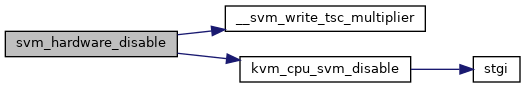

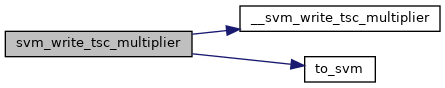

| static void | __svm_write_tsc_multiplier (u64 multiplier) |

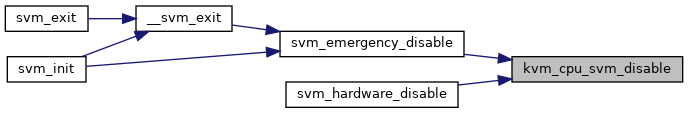

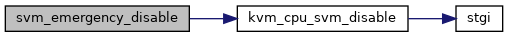

| static void | kvm_cpu_svm_disable (void) |

| static void | svm_emergency_disable (void) |

| static void | svm_hardware_disable (void) |

| static int | svm_hardware_enable (void) |

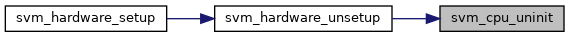

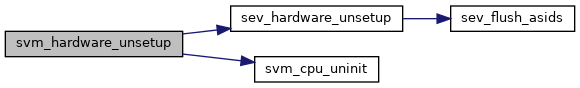

| static void | svm_cpu_uninit (int cpu) |

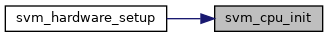

| static int | svm_cpu_init (int cpu) |

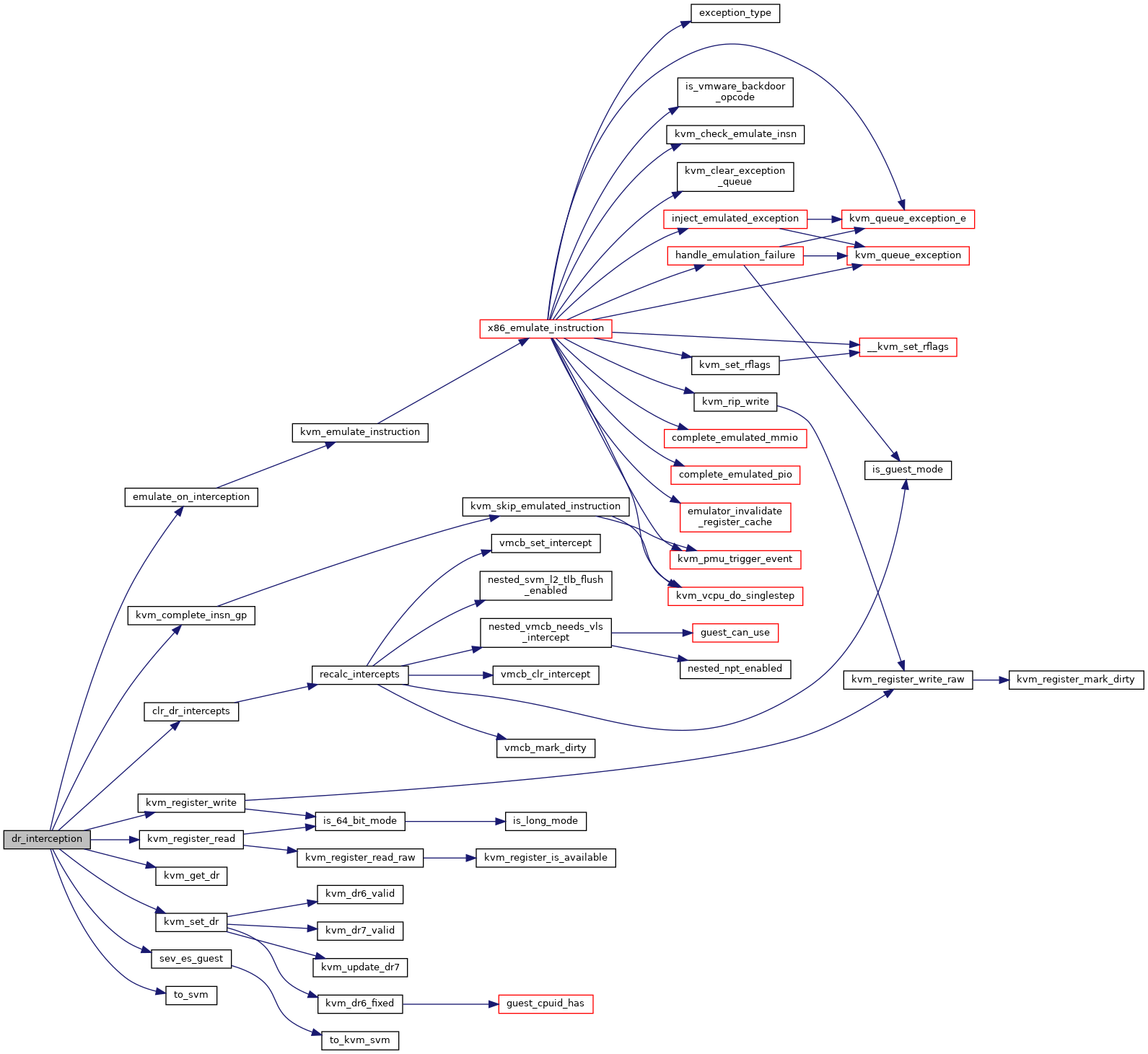

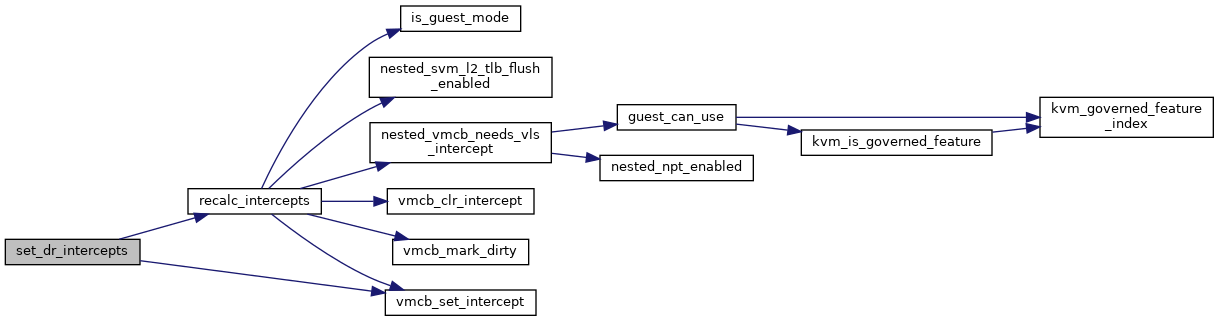

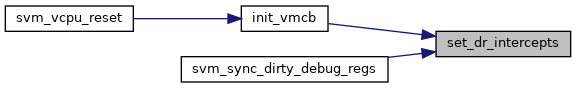

| static void | set_dr_intercepts (struct vcpu_svm *svm) |

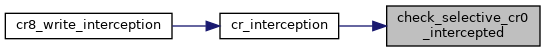

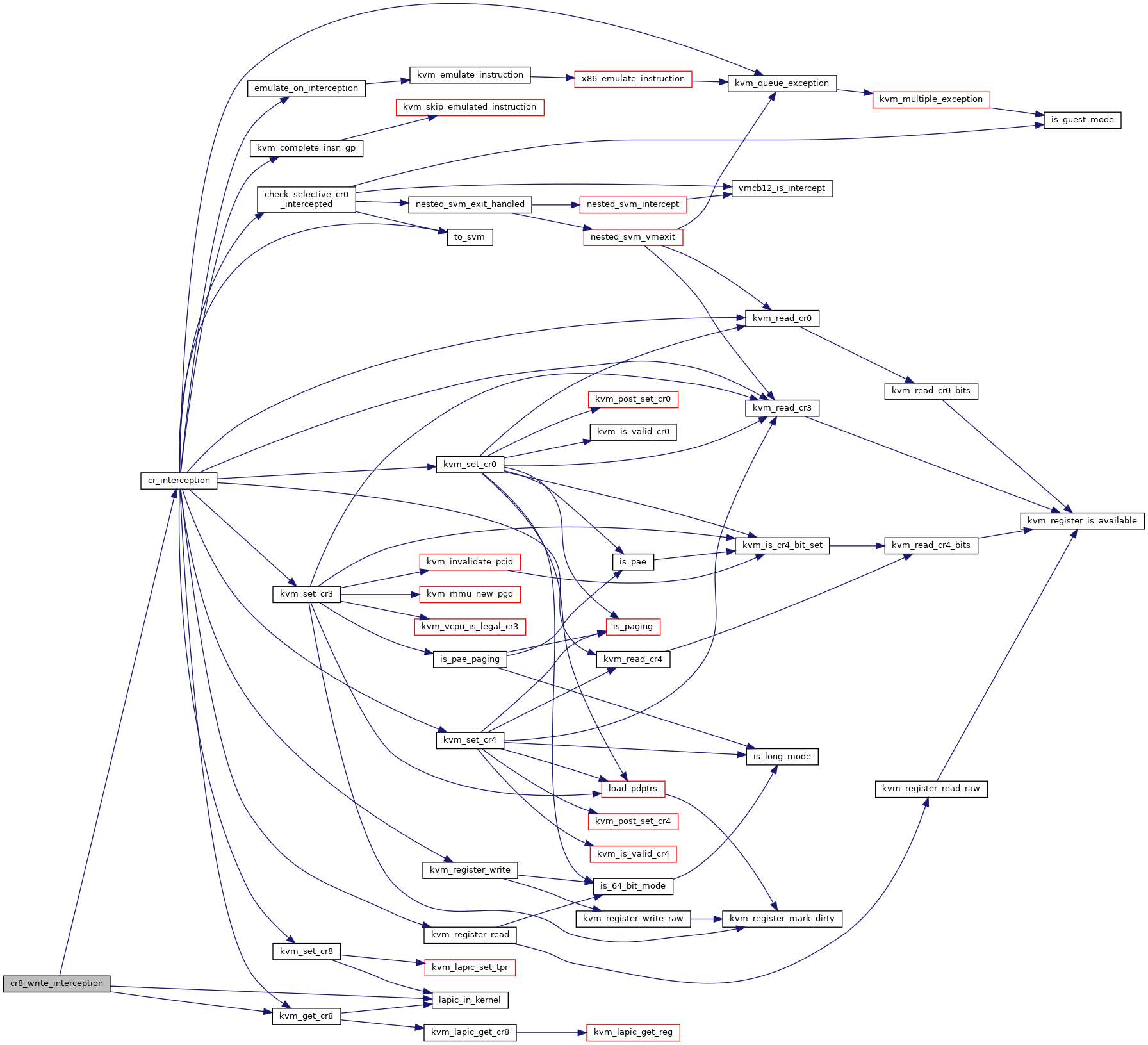

| static void | clr_dr_intercepts (struct vcpu_svm *svm) |

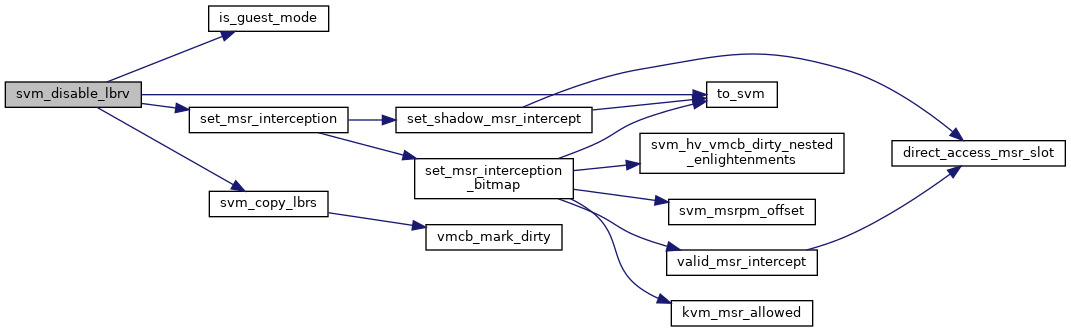

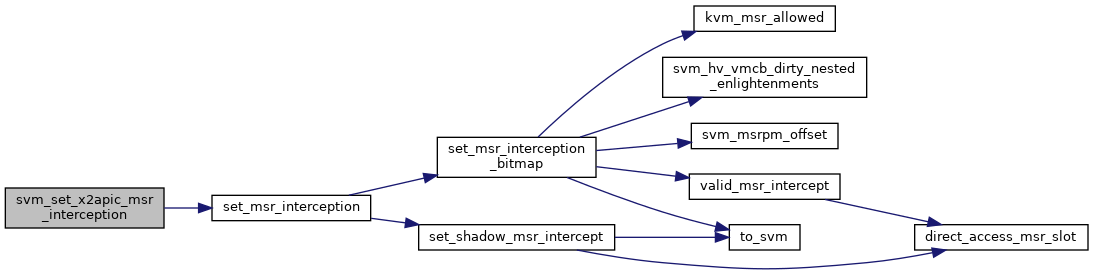

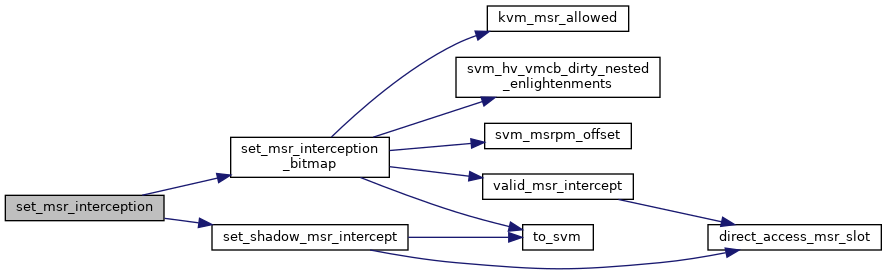

| static int | direct_access_msr_slot (u32 msr) |

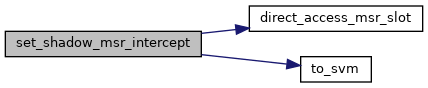

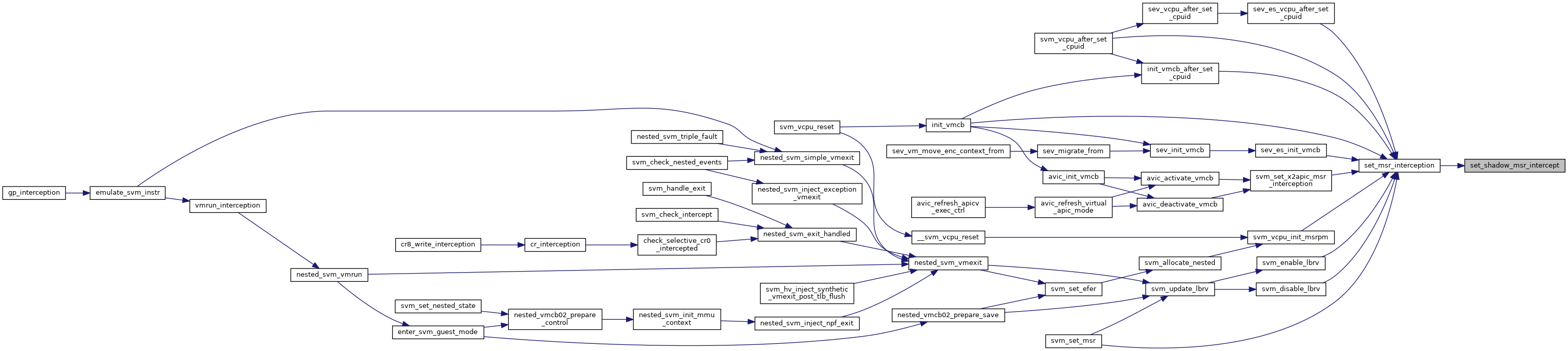

| static void | set_shadow_msr_intercept (struct kvm_vcpu *vcpu, u32 msr, int read, int write) |

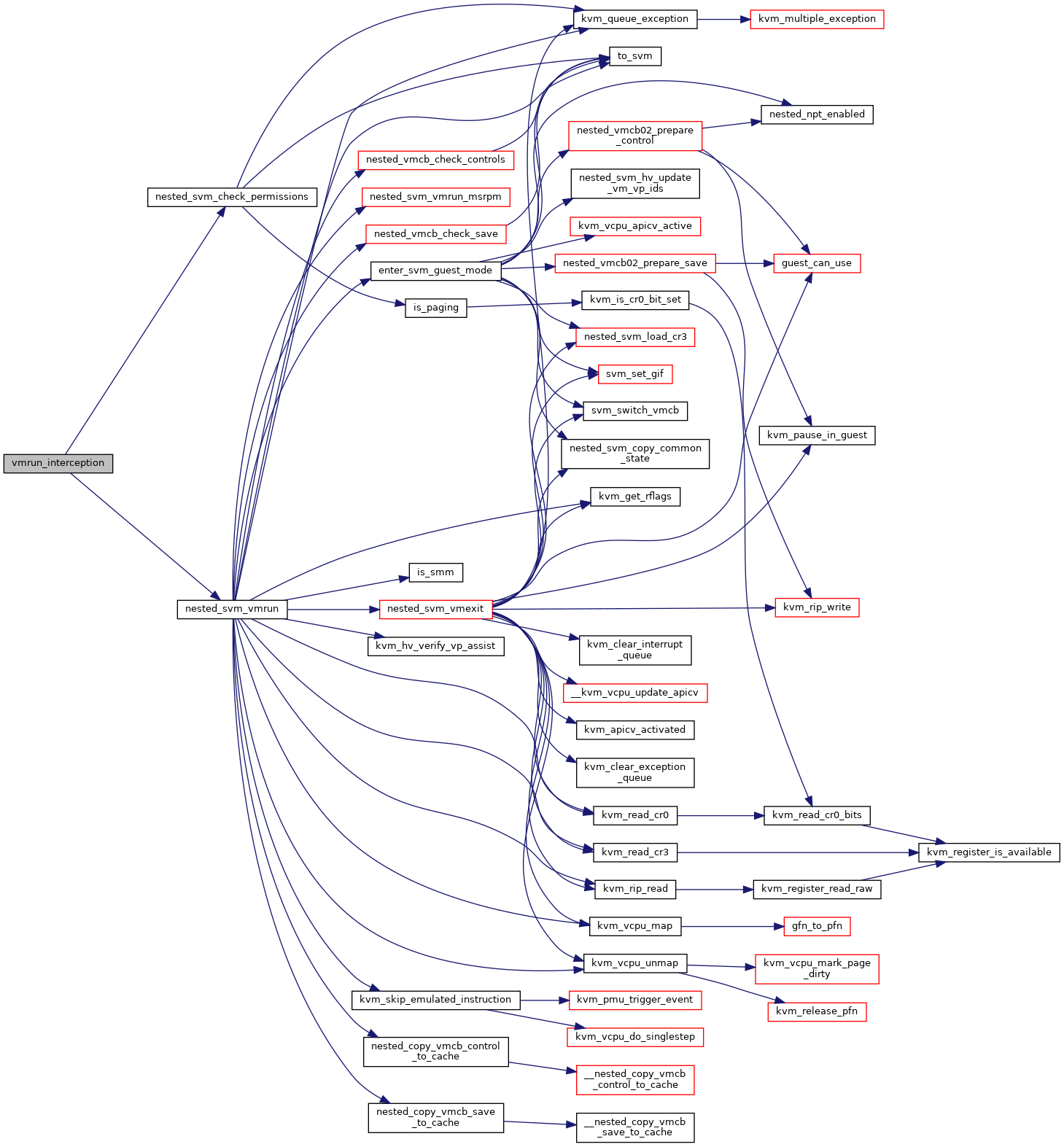

| static bool | valid_msr_intercept (u32 index) |

| static bool | msr_write_intercepted (struct kvm_vcpu *vcpu, u32 msr) |

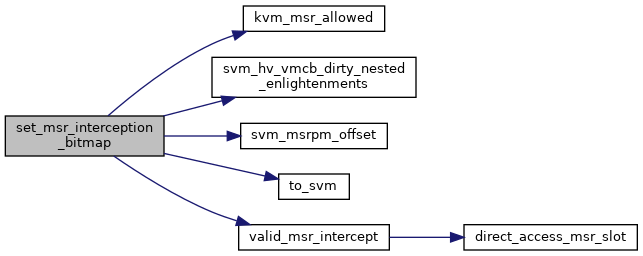

| static void | set_msr_interception_bitmap (struct kvm_vcpu *vcpu, u32 *msrpm, u32 msr, int read, int write) |

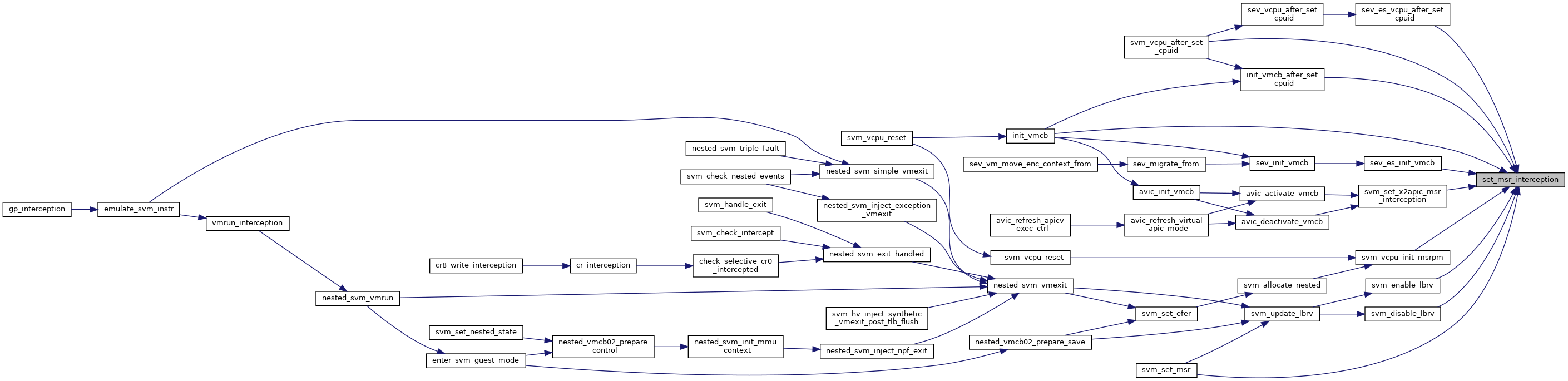

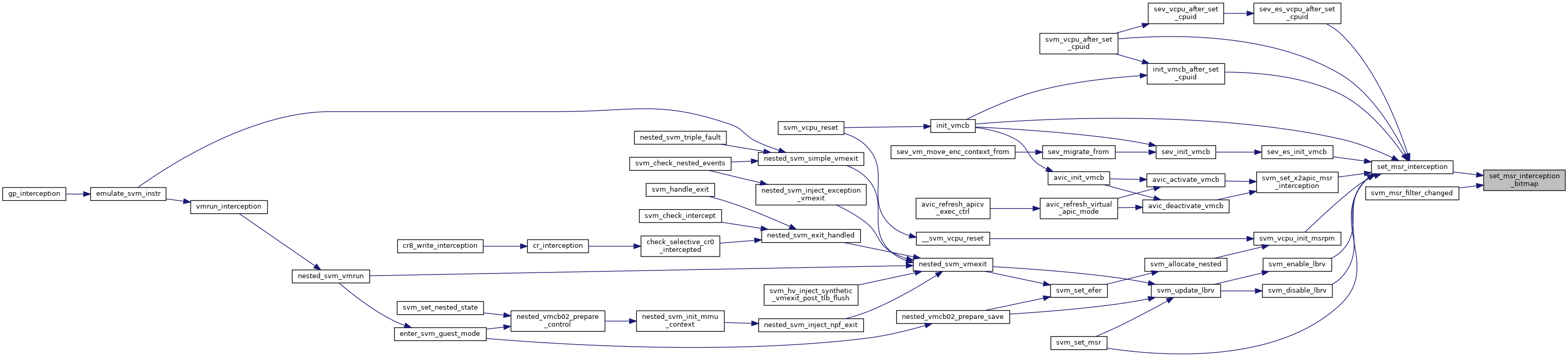

| void | set_msr_interception (struct kvm_vcpu *vcpu, u32 *msrpm, u32 msr, int read, int write) |

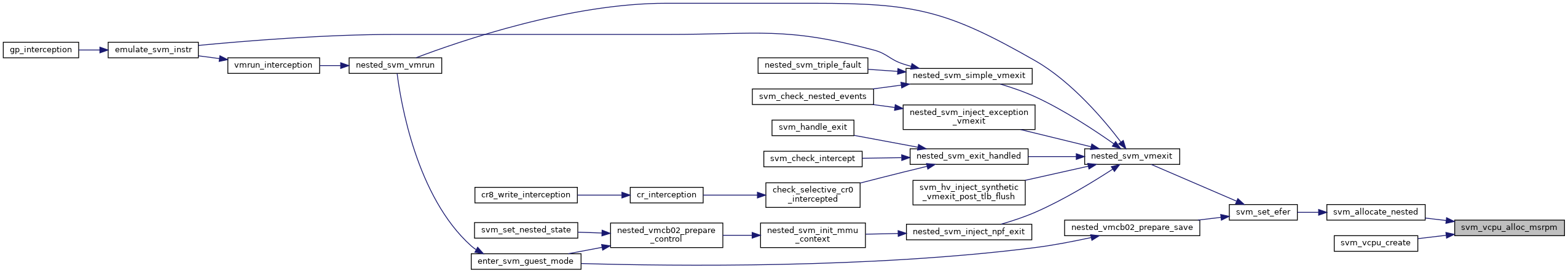

| u32 * | svm_vcpu_alloc_msrpm (void) |

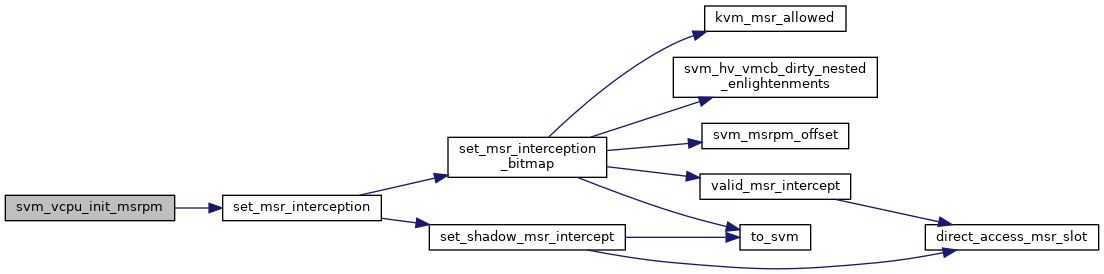

| void | svm_vcpu_init_msrpm (struct kvm_vcpu *vcpu, u32 *msrpm) |

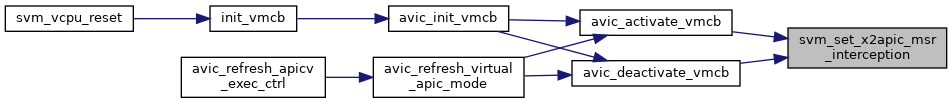

| void | svm_set_x2apic_msr_interception (struct vcpu_svm *svm, bool intercept) |

| void | svm_vcpu_free_msrpm (u32 *msrpm) |

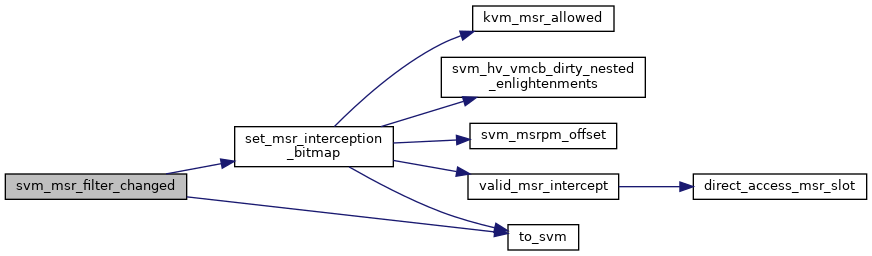

| static void | svm_msr_filter_changed (struct kvm_vcpu *vcpu) |

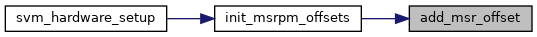

| static void | add_msr_offset (u32 offset) |

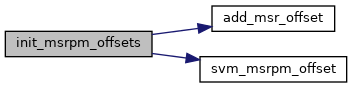

| static void | init_msrpm_offsets (void) |

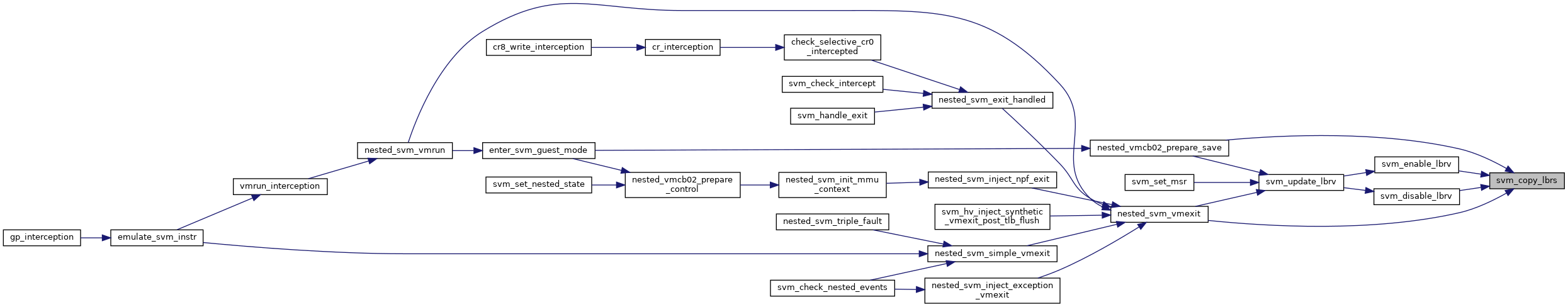

| void | svm_copy_lbrs (struct vmcb *to_vmcb, struct vmcb *from_vmcb) |

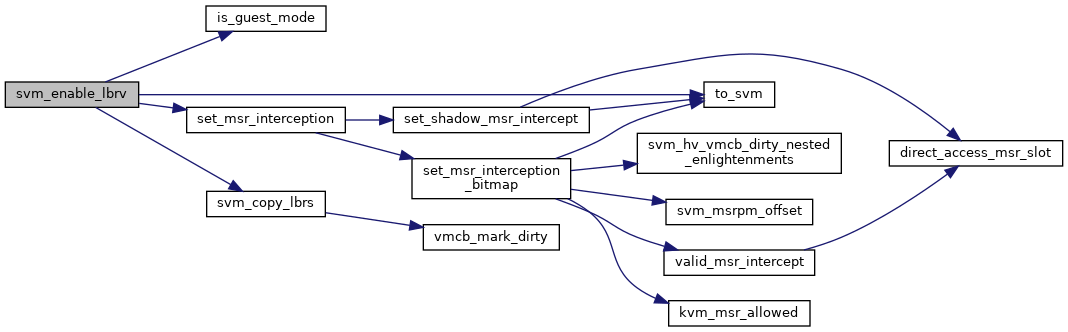

| static void | svm_enable_lbrv (struct kvm_vcpu *vcpu) |

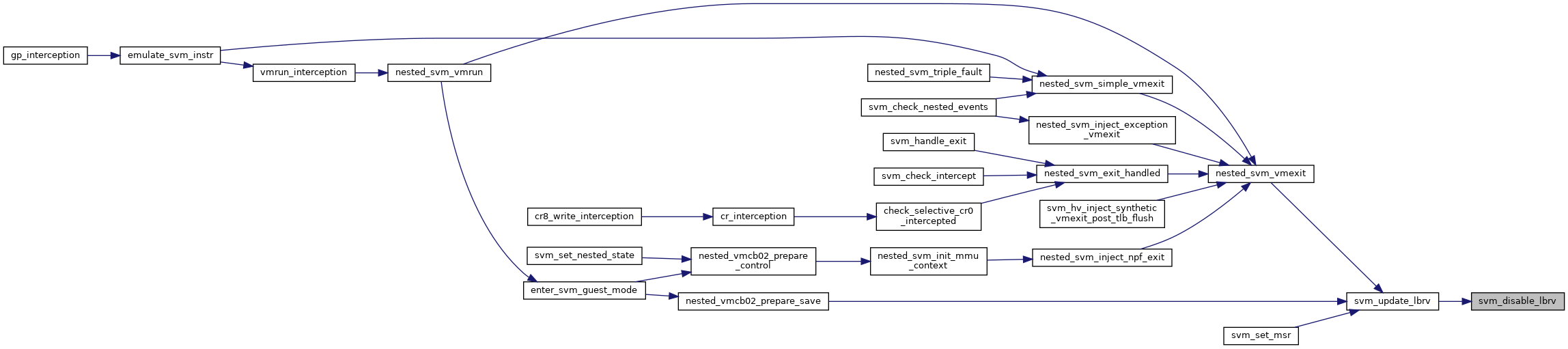

| static void | svm_disable_lbrv (struct kvm_vcpu *vcpu) |

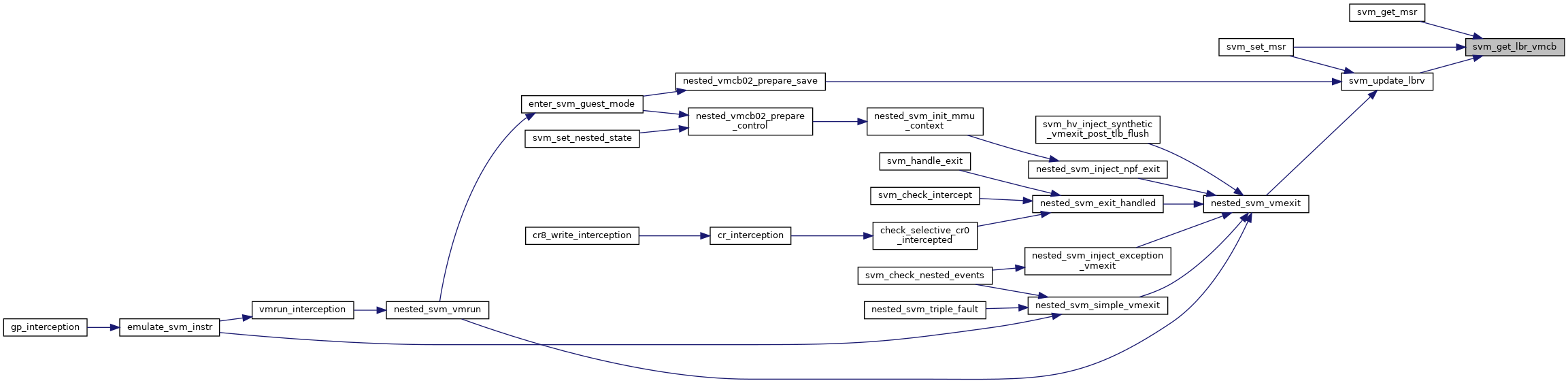

| static struct vmcb * | svm_get_lbr_vmcb (struct vcpu_svm *svm) |

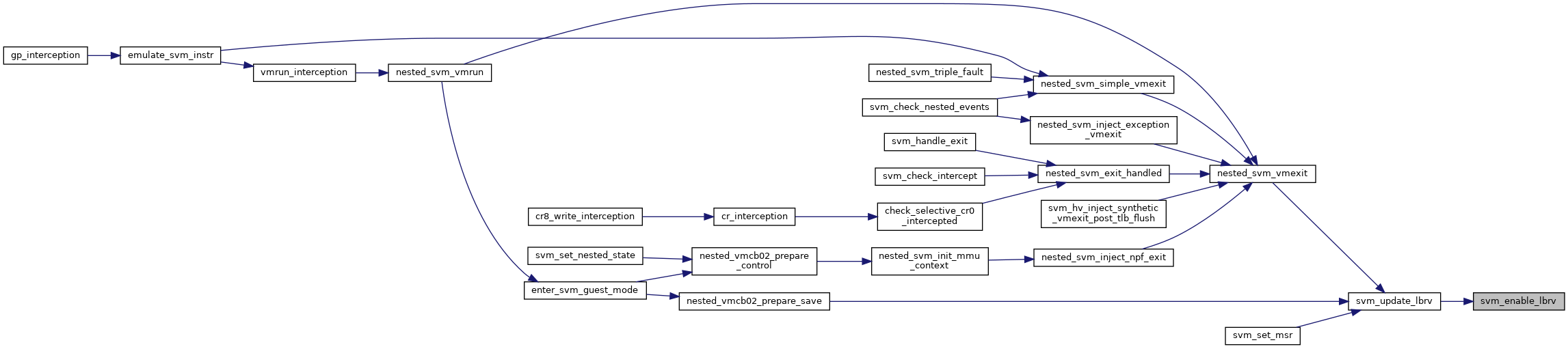

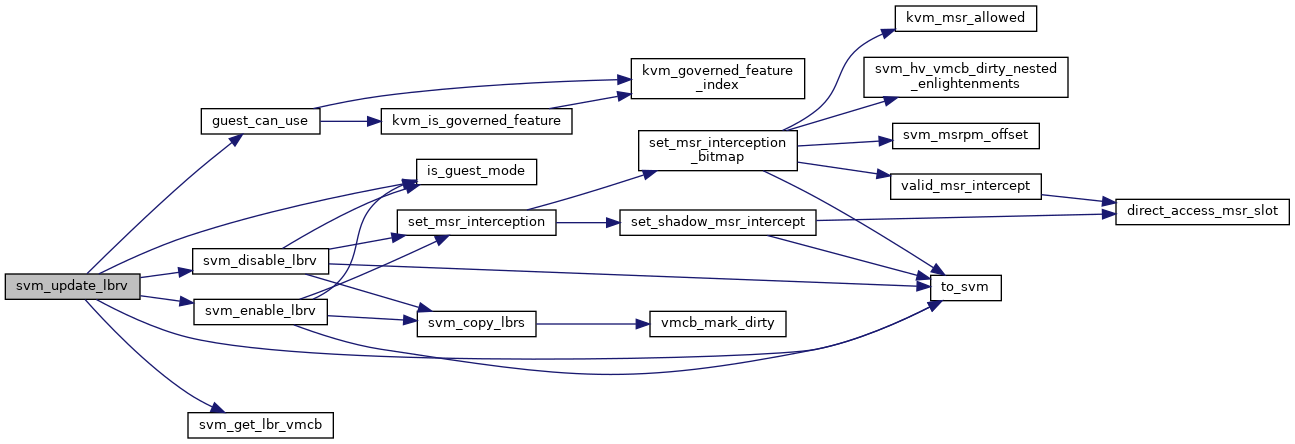

| void | svm_update_lbrv (struct kvm_vcpu *vcpu) |

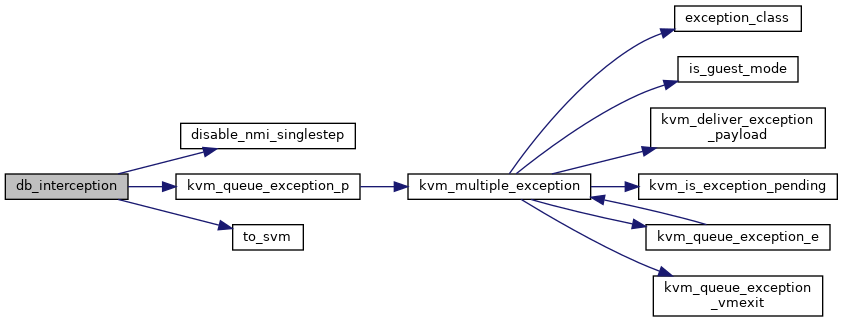

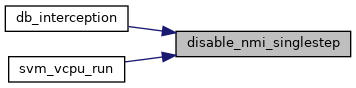

| void | disable_nmi_singlestep (struct vcpu_svm *svm) |

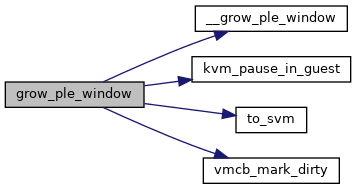

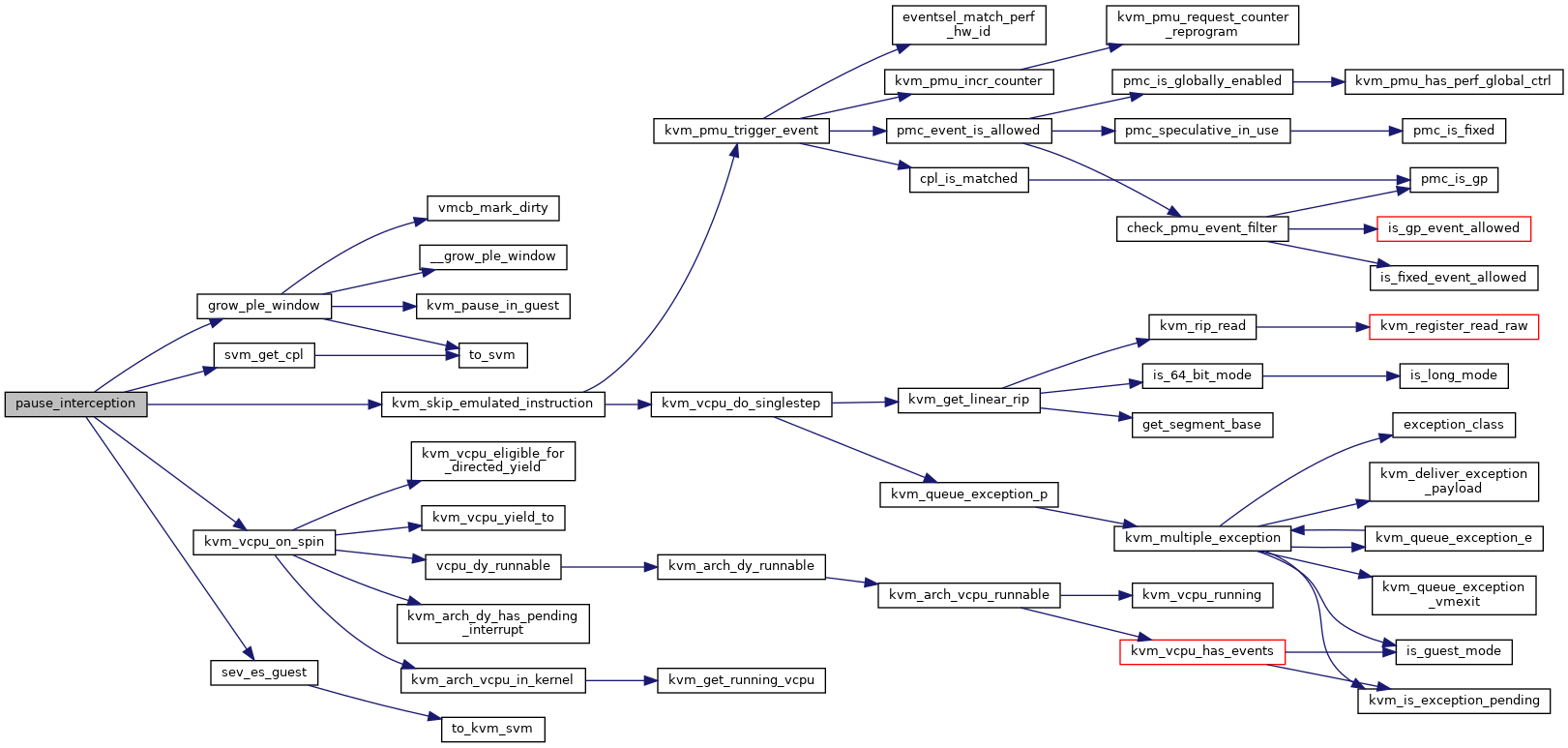

| static void | grow_ple_window (struct kvm_vcpu *vcpu) |

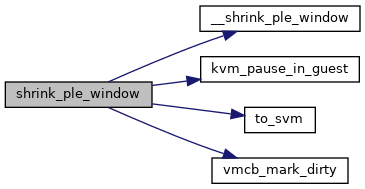

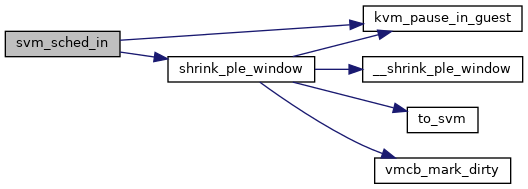

| static void | shrink_ple_window (struct kvm_vcpu *vcpu) |

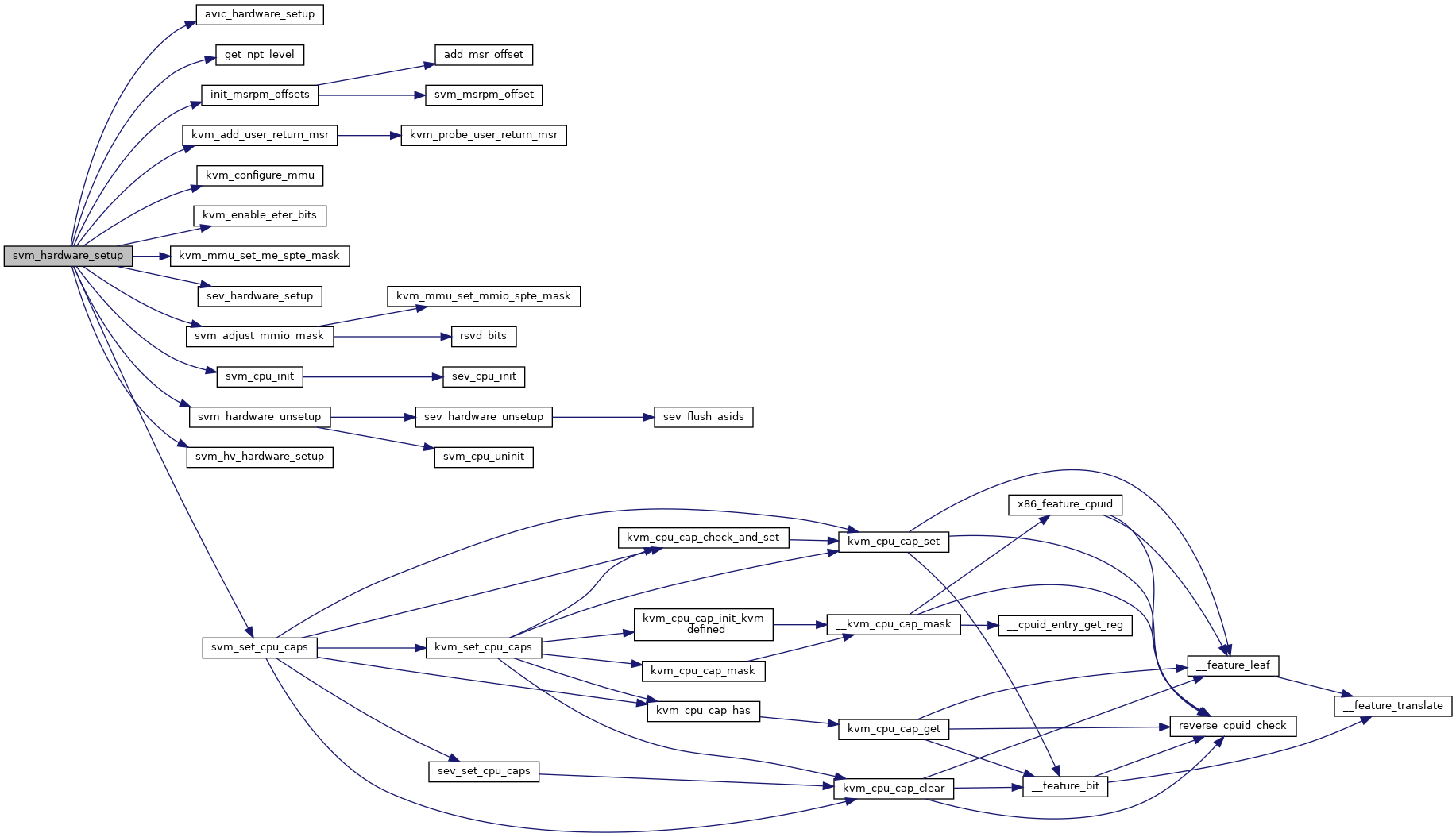

| static void | svm_hardware_unsetup (void) |

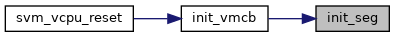

| static void | init_seg (struct vmcb_seg *seg) |

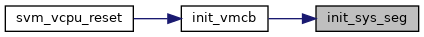

| static void | init_sys_seg (struct vmcb_seg *seg, uint32_t type) |

| static u64 | svm_get_l2_tsc_offset (struct kvm_vcpu *vcpu) |

| static u64 | svm_get_l2_tsc_multiplier (struct kvm_vcpu *vcpu) |

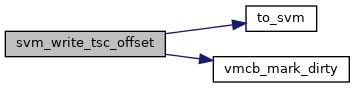

| static void | svm_write_tsc_offset (struct kvm_vcpu *vcpu) |

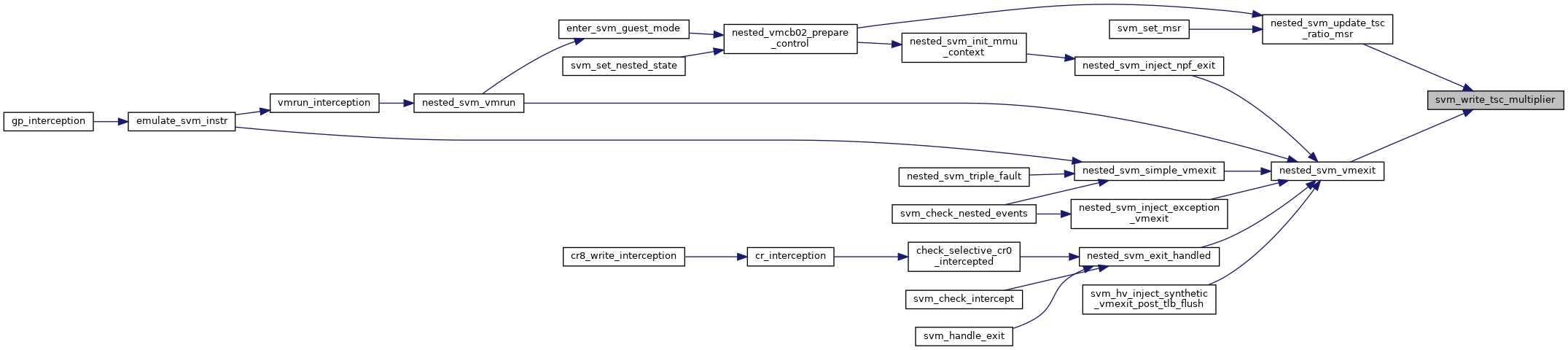

| void | svm_write_tsc_multiplier (struct kvm_vcpu *vcpu) |

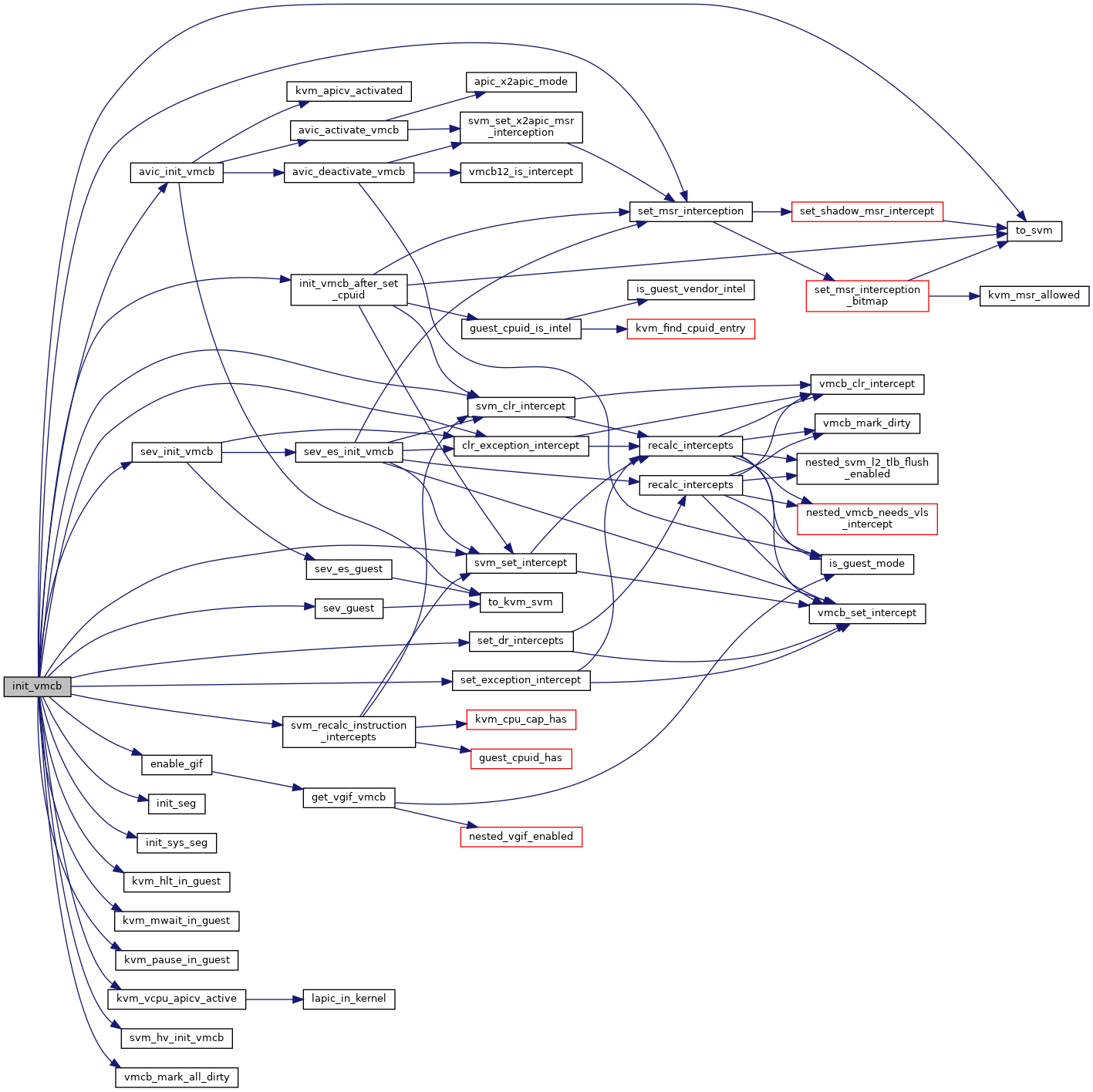

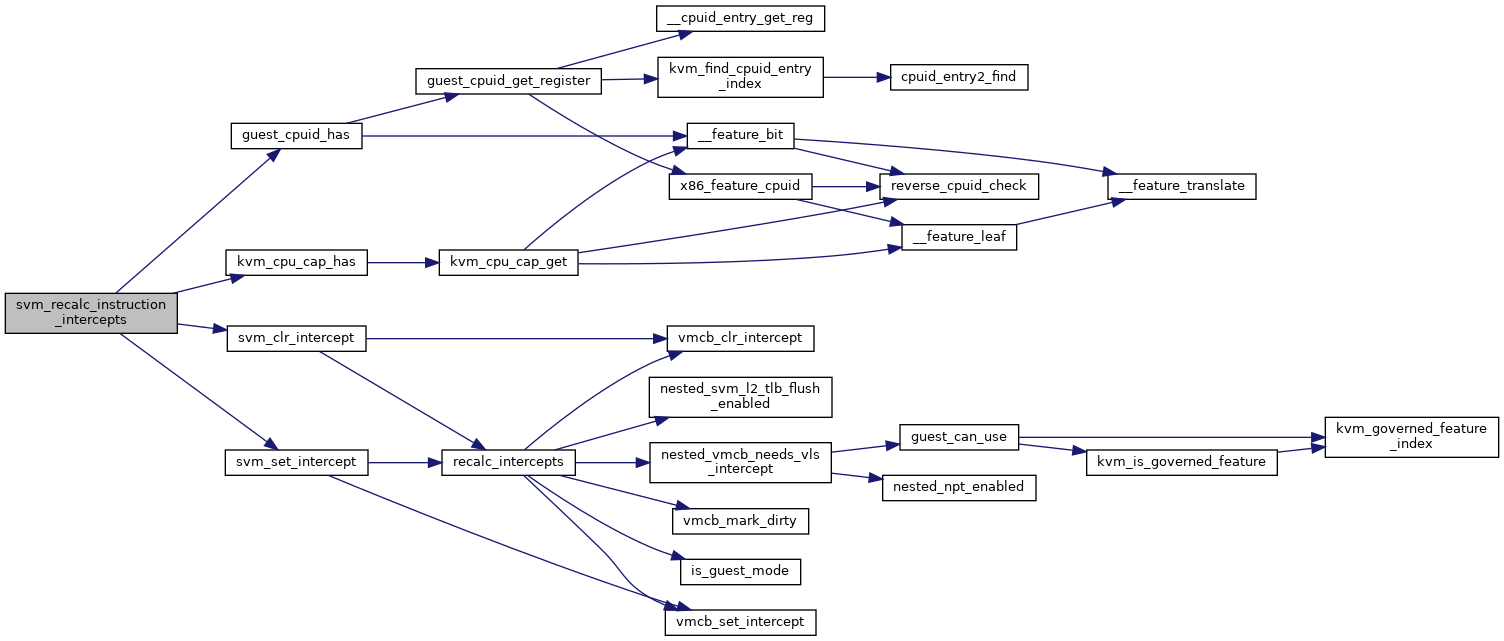

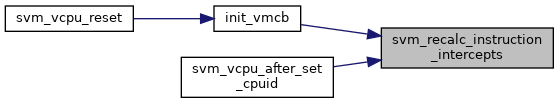

| static void | svm_recalc_instruction_intercepts (struct kvm_vcpu *vcpu, struct vcpu_svm *svm) |

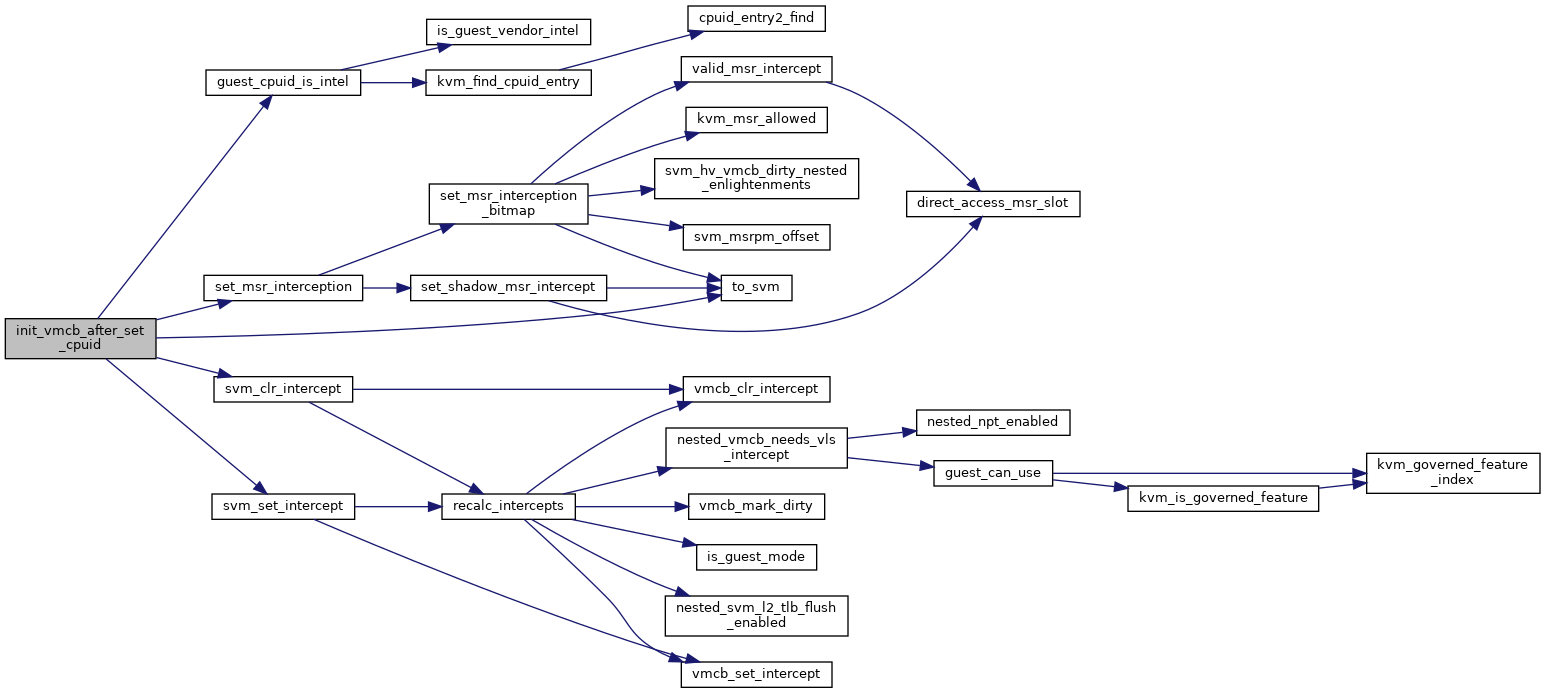

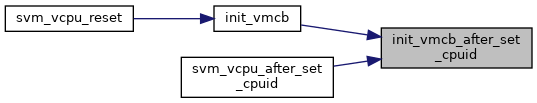

| static void | init_vmcb_after_set_cpuid (struct kvm_vcpu *vcpu) |

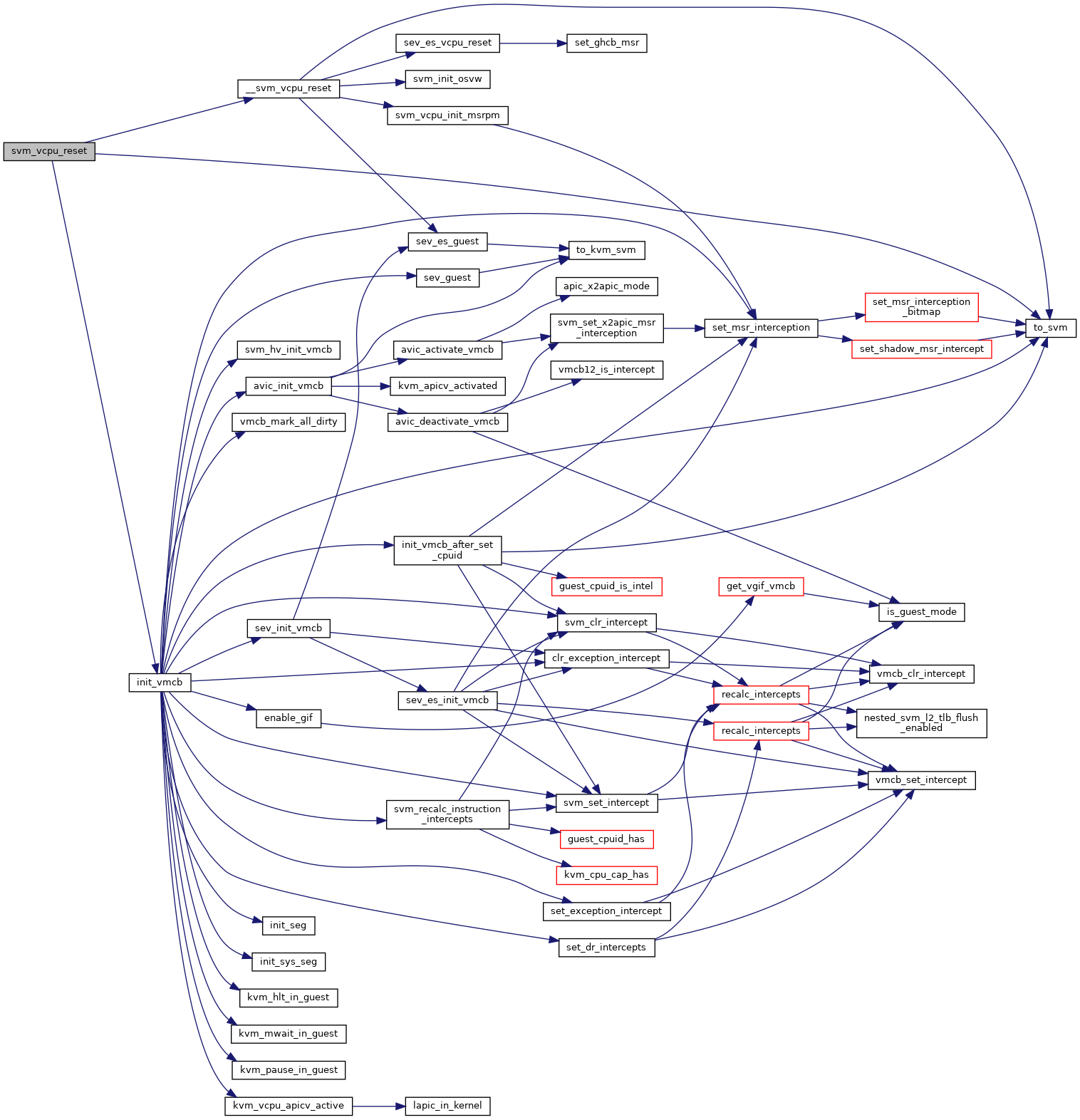

| static void | init_vmcb (struct kvm_vcpu *vcpu) |

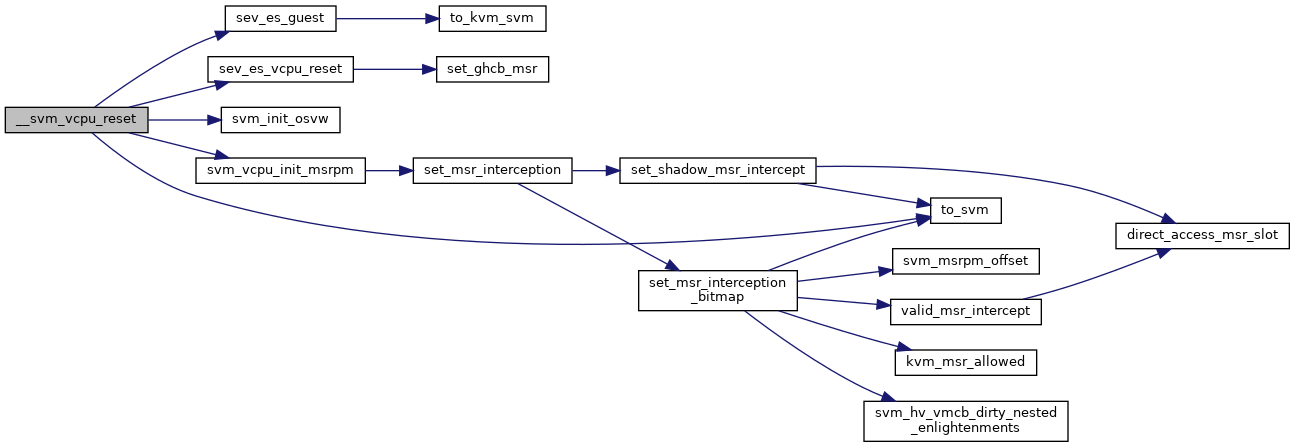

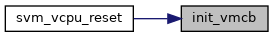

| static void | __svm_vcpu_reset (struct kvm_vcpu *vcpu) |

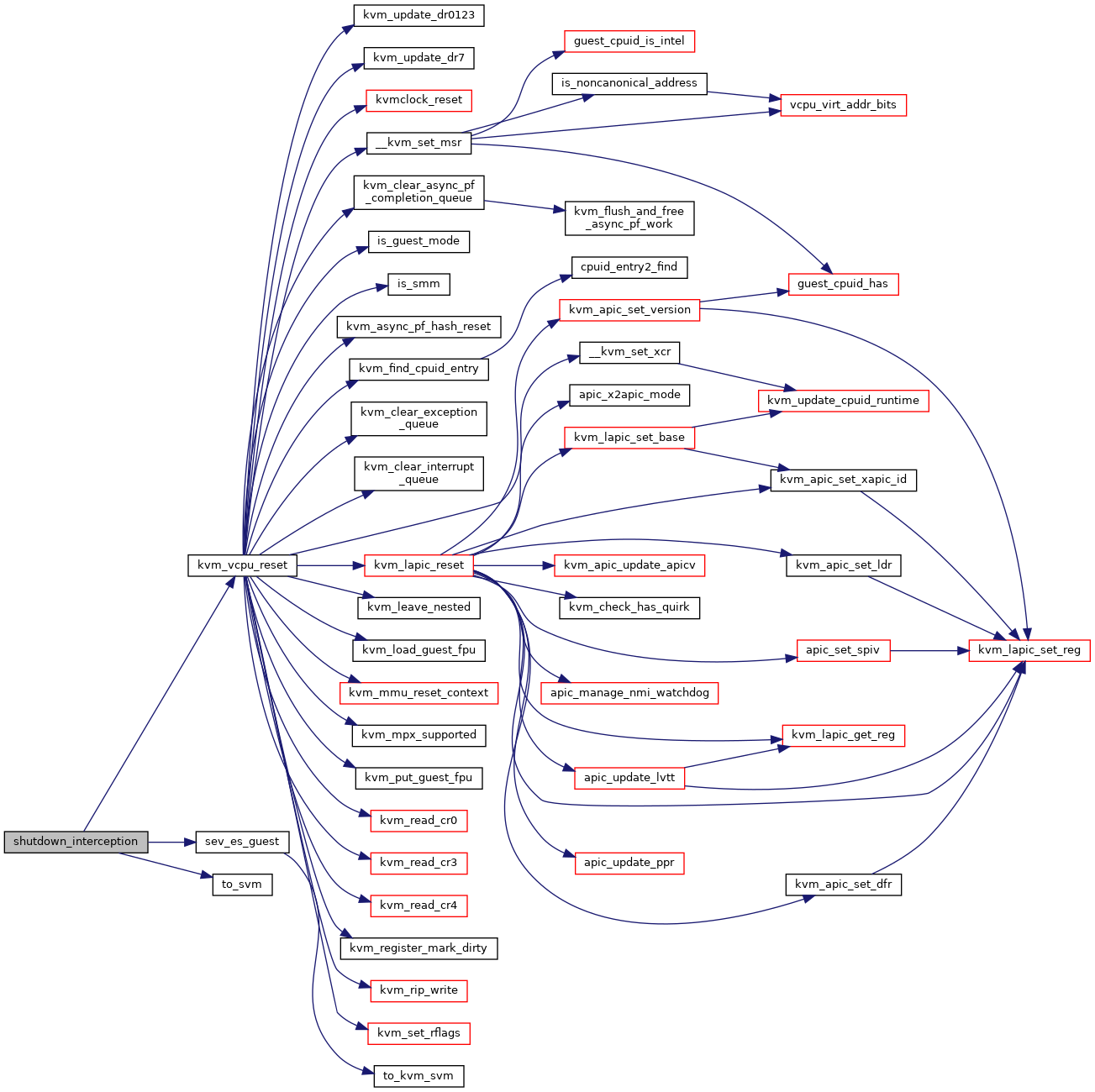

| static void | svm_vcpu_reset (struct kvm_vcpu *vcpu, bool init_event) |

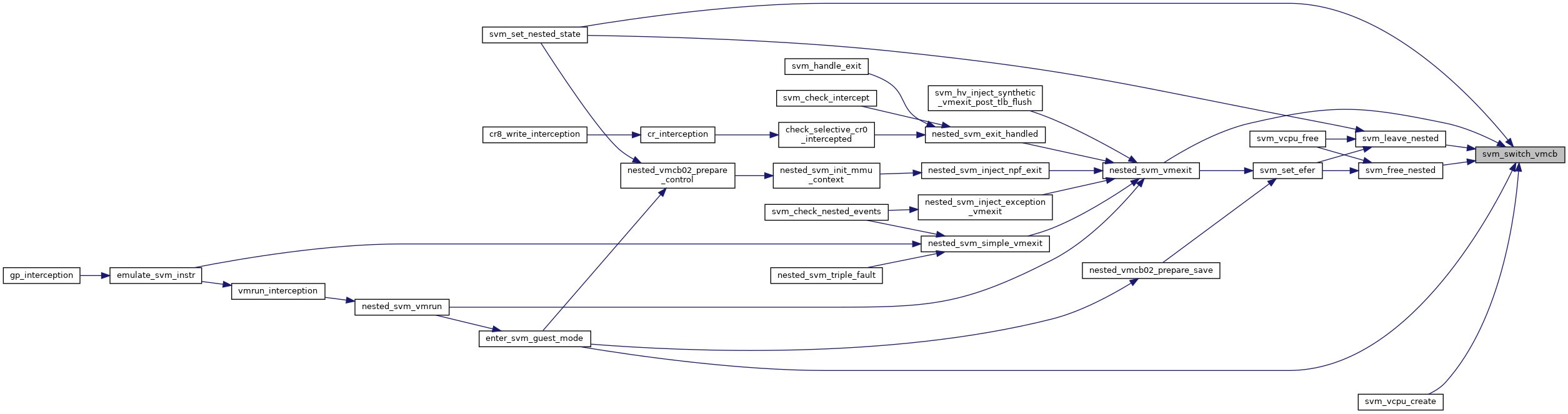

| void | svm_switch_vmcb (struct vcpu_svm *svm, struct kvm_vmcb_info *target_vmcb) |

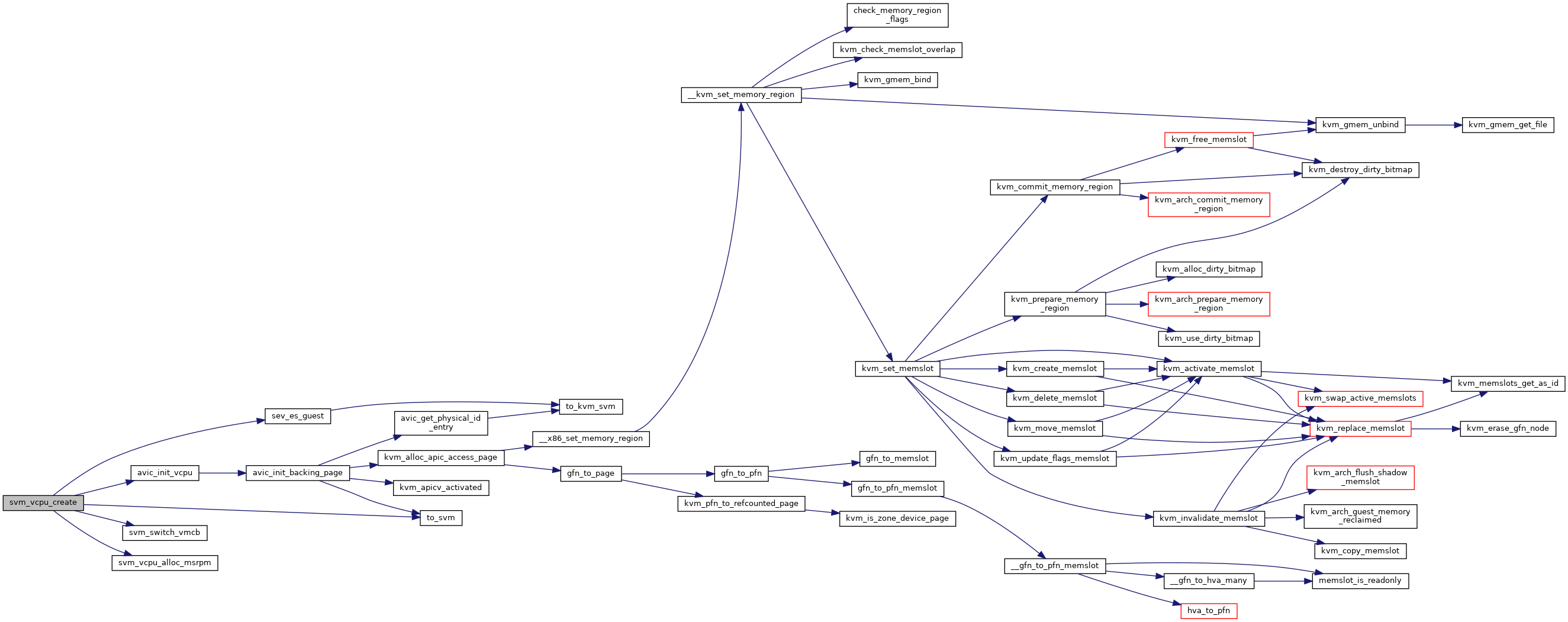

| static int | svm_vcpu_create (struct kvm_vcpu *vcpu) |

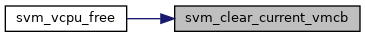

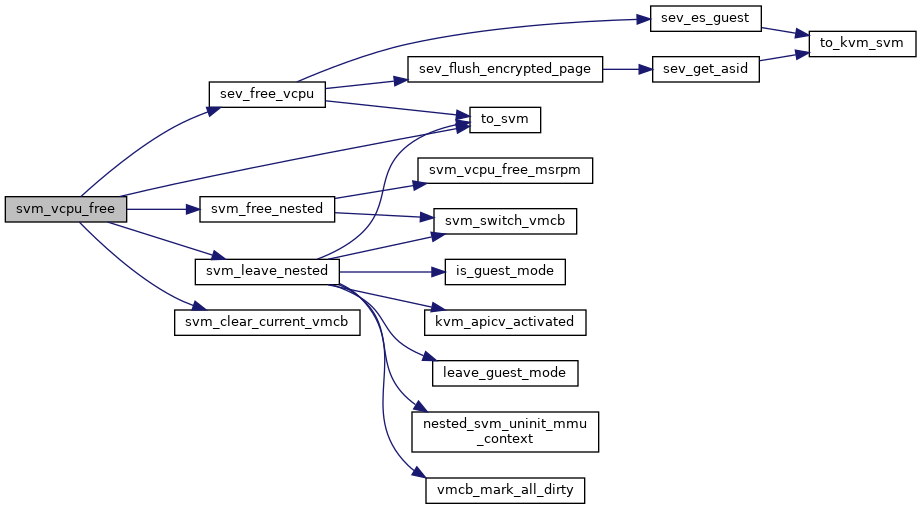

| static void | svm_clear_current_vmcb (struct vmcb *vmcb) |

| static void | svm_vcpu_free (struct kvm_vcpu *vcpu) |

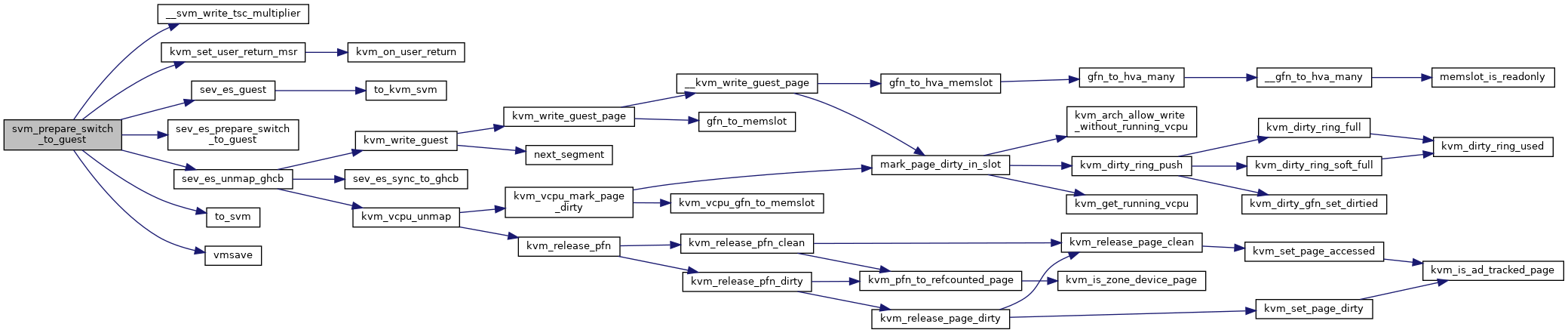

| static void | svm_prepare_switch_to_guest (struct kvm_vcpu *vcpu) |

| static void | svm_prepare_host_switch (struct kvm_vcpu *vcpu) |

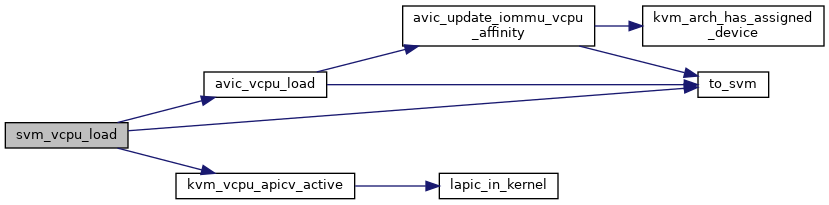

| static void | svm_vcpu_load (struct kvm_vcpu *vcpu, int cpu) |

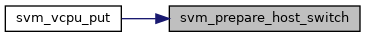

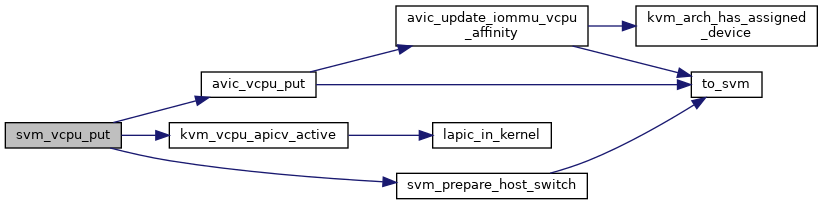

| static void | svm_vcpu_put (struct kvm_vcpu *vcpu) |

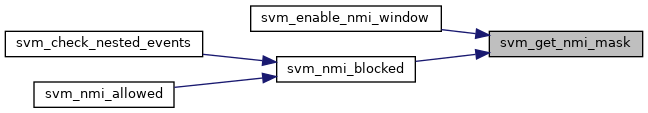

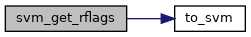

| static unsigned long | svm_get_rflags (struct kvm_vcpu *vcpu) |

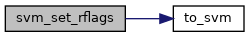

| static void | svm_set_rflags (struct kvm_vcpu *vcpu, unsigned long rflags) |

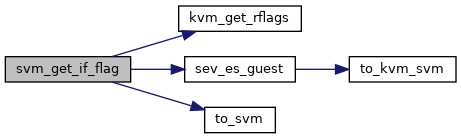

| static bool | svm_get_if_flag (struct kvm_vcpu *vcpu) |

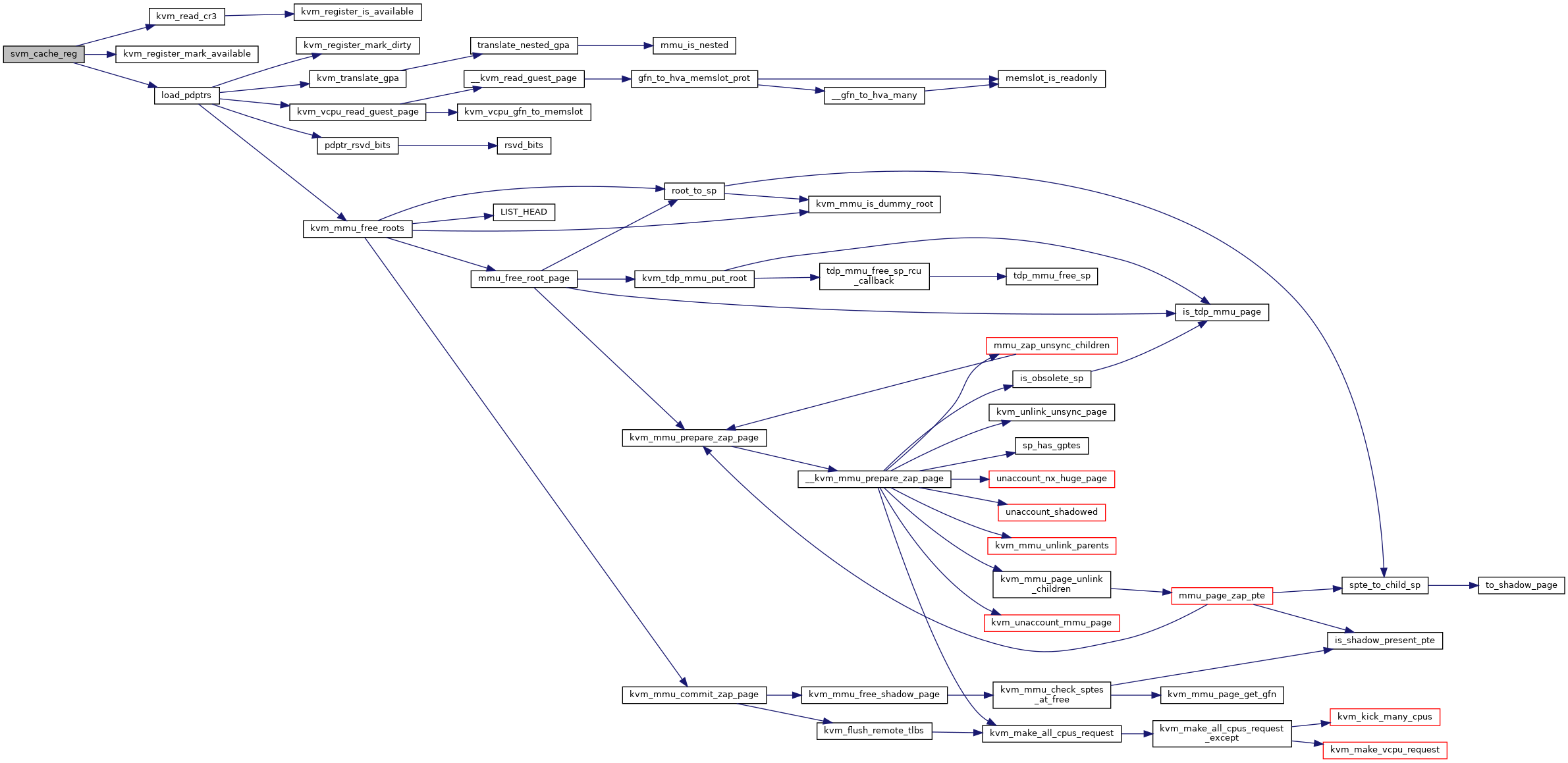

| static void | svm_cache_reg (struct kvm_vcpu *vcpu, enum kvm_reg reg) |

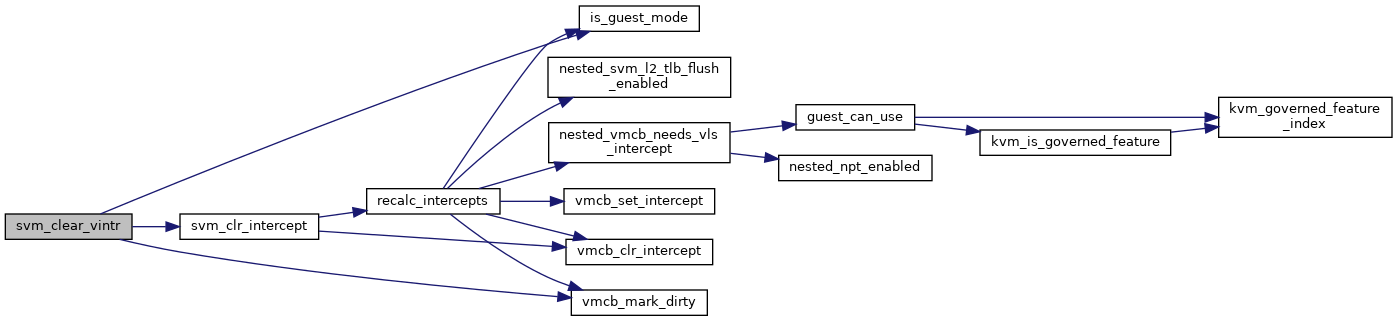

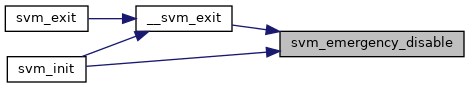

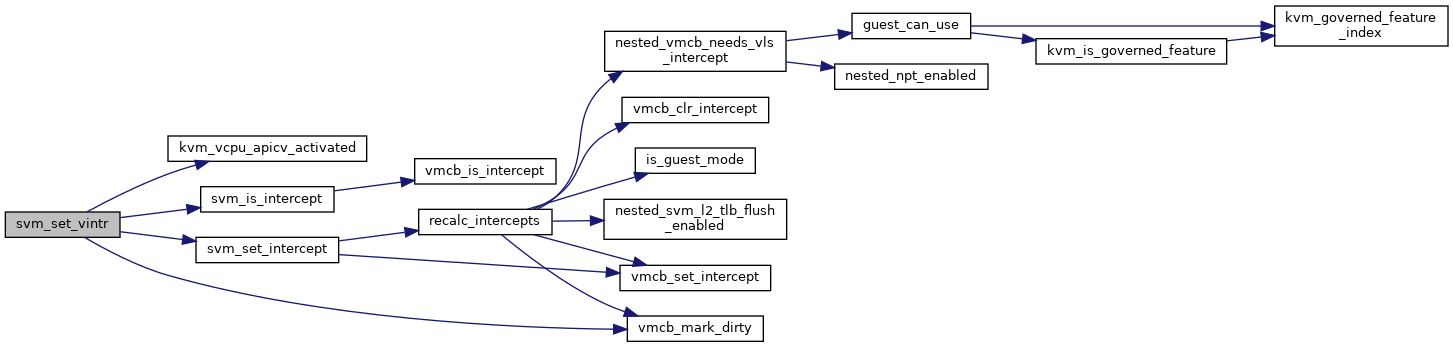

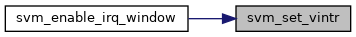

| static void | svm_set_vintr (struct vcpu_svm *svm) |

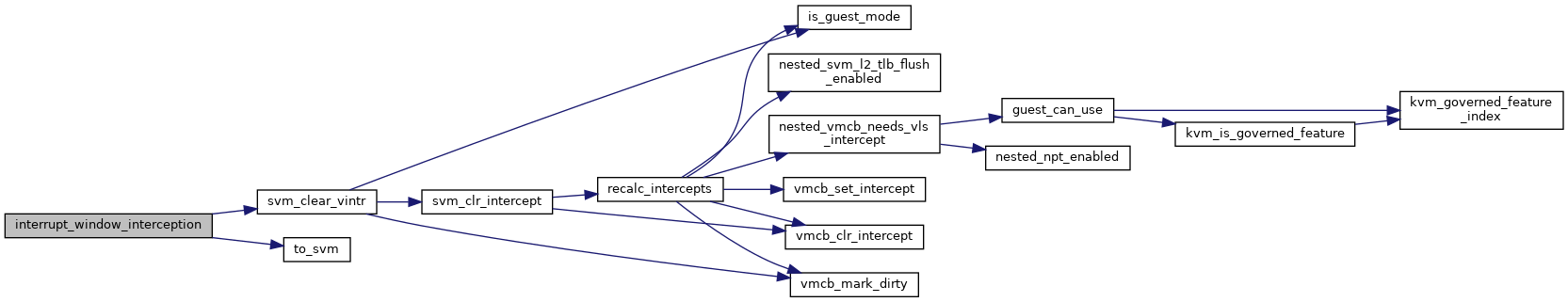

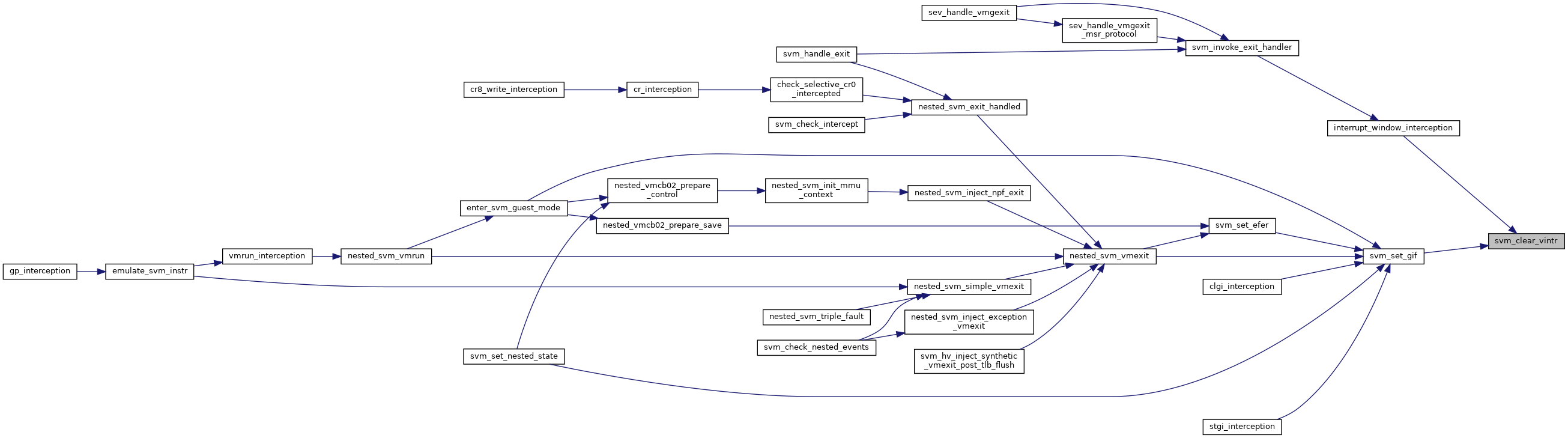

| static void | svm_clear_vintr (struct vcpu_svm *svm) |

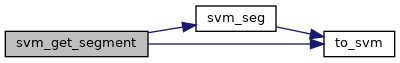

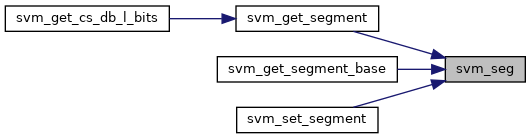

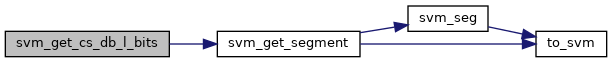

| static struct vmcb_seg * | svm_seg (struct kvm_vcpu *vcpu, int seg) |

| static u64 | svm_get_segment_base (struct kvm_vcpu *vcpu, int seg) |

| static void | svm_get_segment (struct kvm_vcpu *vcpu, struct kvm_segment *var, int seg) |

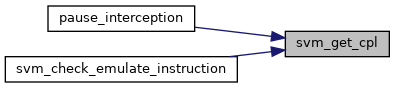

| static int | svm_get_cpl (struct kvm_vcpu *vcpu) |

| static void | svm_get_cs_db_l_bits (struct kvm_vcpu *vcpu, int *db, int *l) |

| static void | svm_get_idt (struct kvm_vcpu *vcpu, struct desc_ptr *dt) |

| static void | svm_set_idt (struct kvm_vcpu *vcpu, struct desc_ptr *dt) |

| static void | svm_get_gdt (struct kvm_vcpu *vcpu, struct desc_ptr *dt) |

| static void | svm_set_gdt (struct kvm_vcpu *vcpu, struct desc_ptr *dt) |

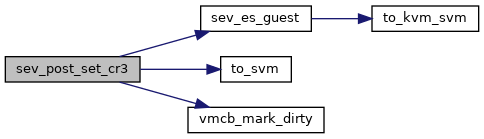

| static void | sev_post_set_cr3 (struct kvm_vcpu *vcpu, unsigned long cr3) |

| static bool | svm_is_valid_cr0 (struct kvm_vcpu *vcpu, unsigned long cr0) |

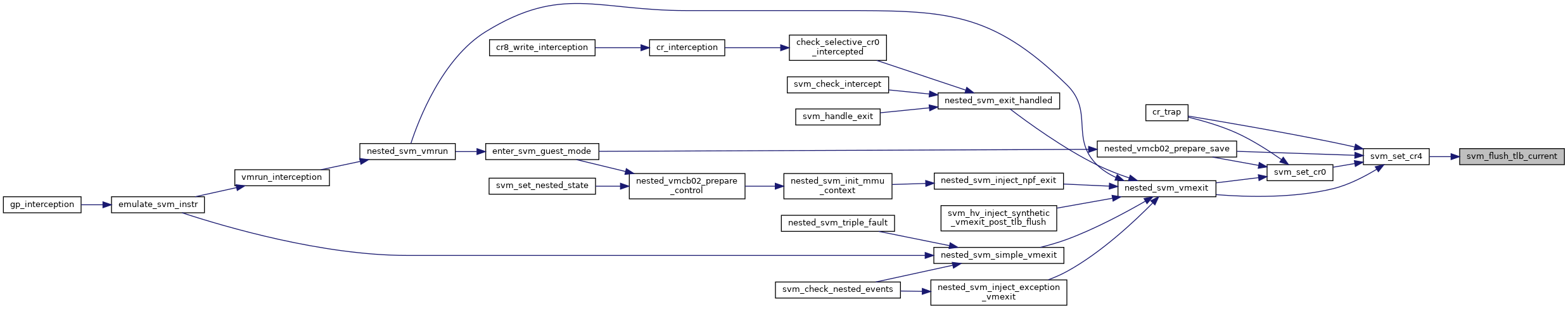

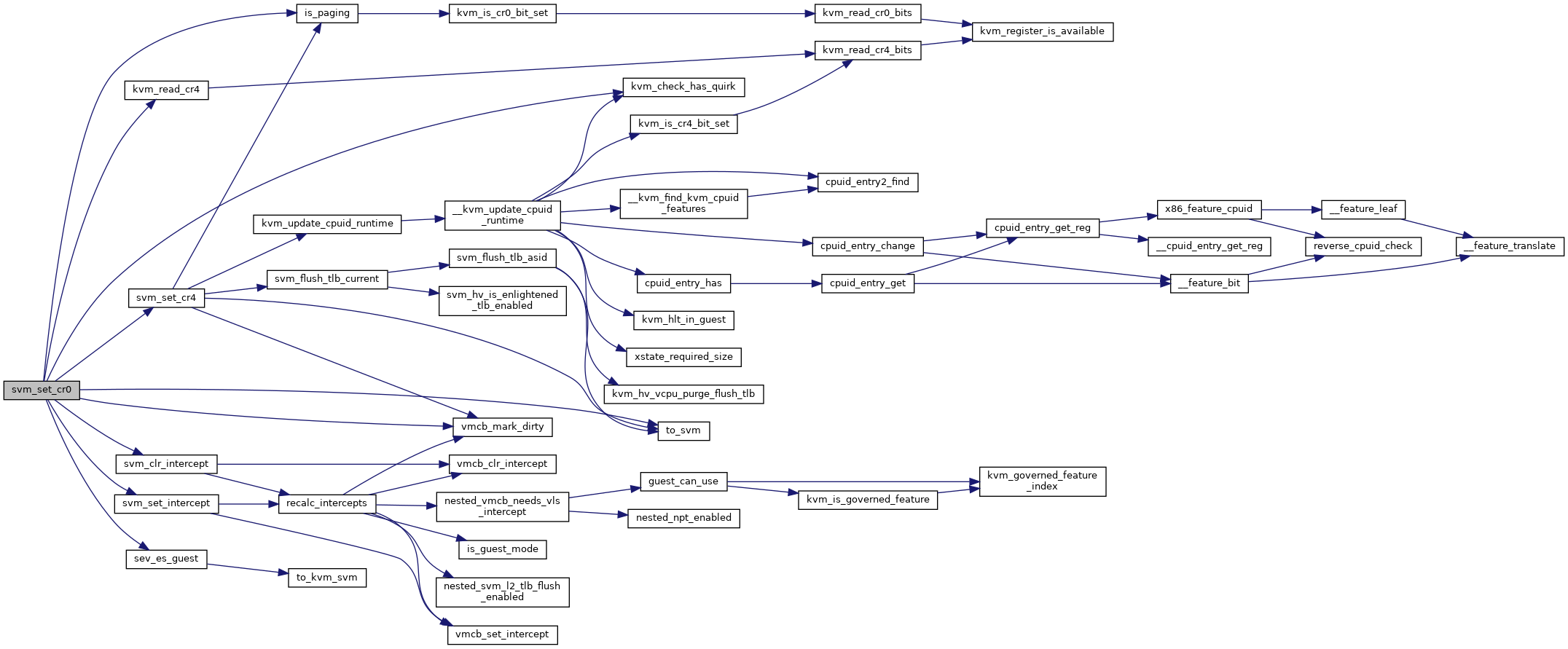

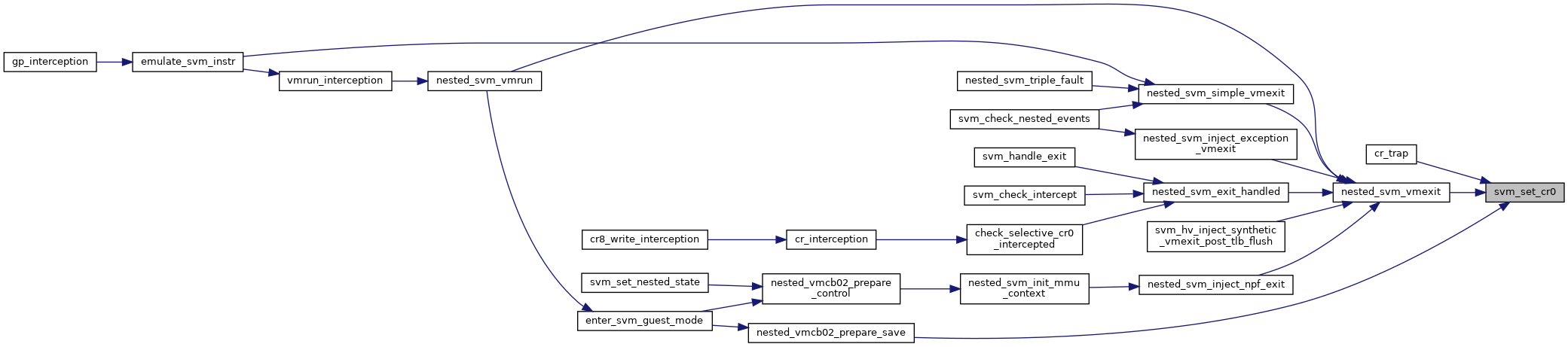

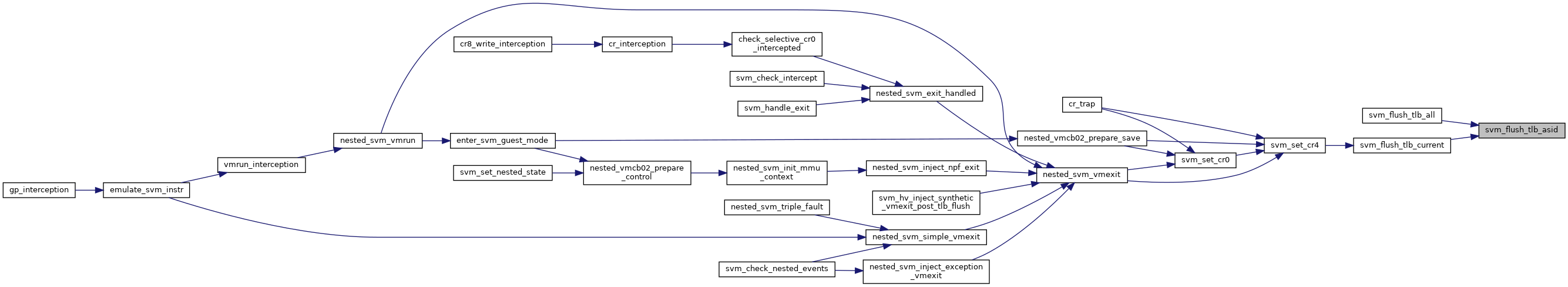

| void | svm_set_cr0 (struct kvm_vcpu *vcpu, unsigned long cr0) |

| static bool | svm_is_valid_cr4 (struct kvm_vcpu *vcpu, unsigned long cr4) |

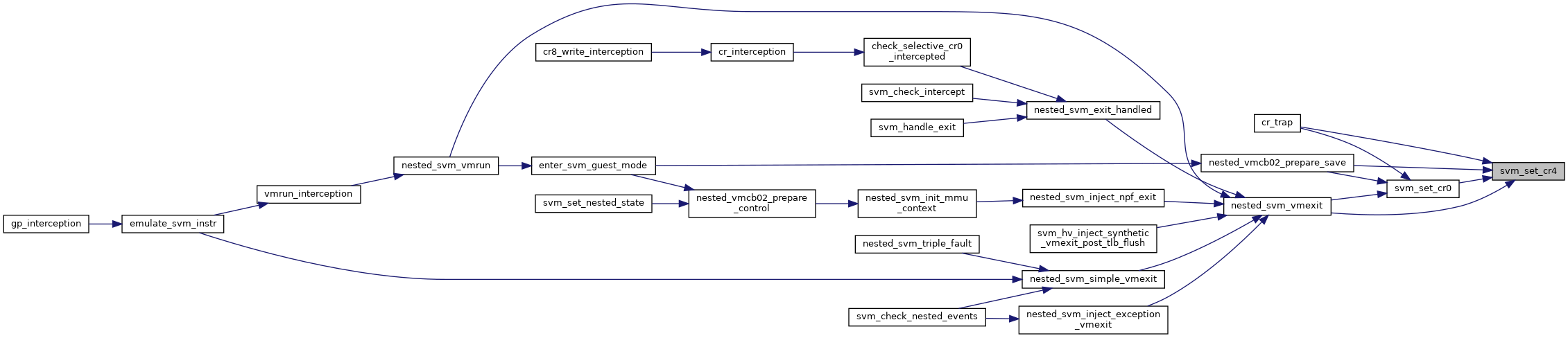

| void | svm_set_cr4 (struct kvm_vcpu *vcpu, unsigned long cr4) |

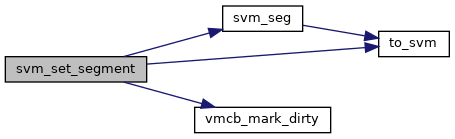

| static void | svm_set_segment (struct kvm_vcpu *vcpu, struct kvm_segment *var, int seg) |

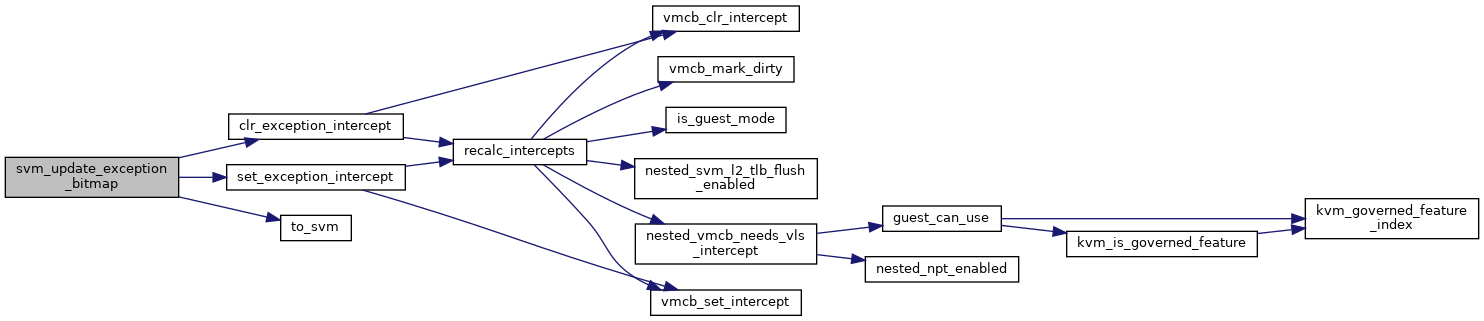

| static void | svm_update_exception_bitmap (struct kvm_vcpu *vcpu) |

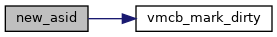

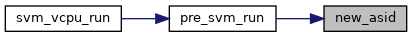

| static void | new_asid (struct vcpu_svm *svm, struct svm_cpu_data *sd) |

| static void | svm_set_dr6 (struct vcpu_svm *svm, unsigned long value) |

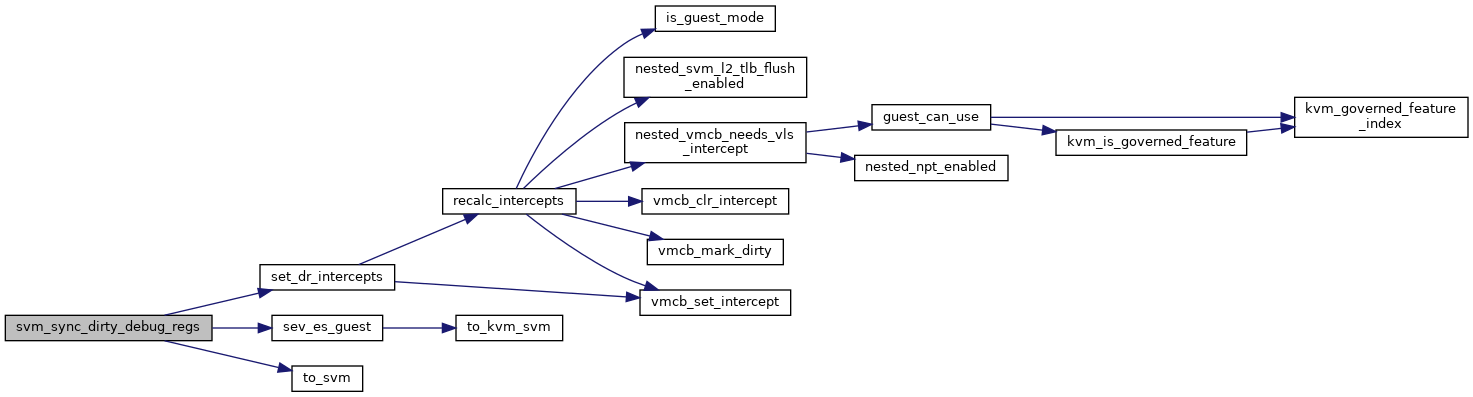

| static void | svm_sync_dirty_debug_regs (struct kvm_vcpu *vcpu) |

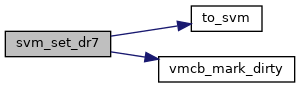

| static void | svm_set_dr7 (struct kvm_vcpu *vcpu, unsigned long value) |

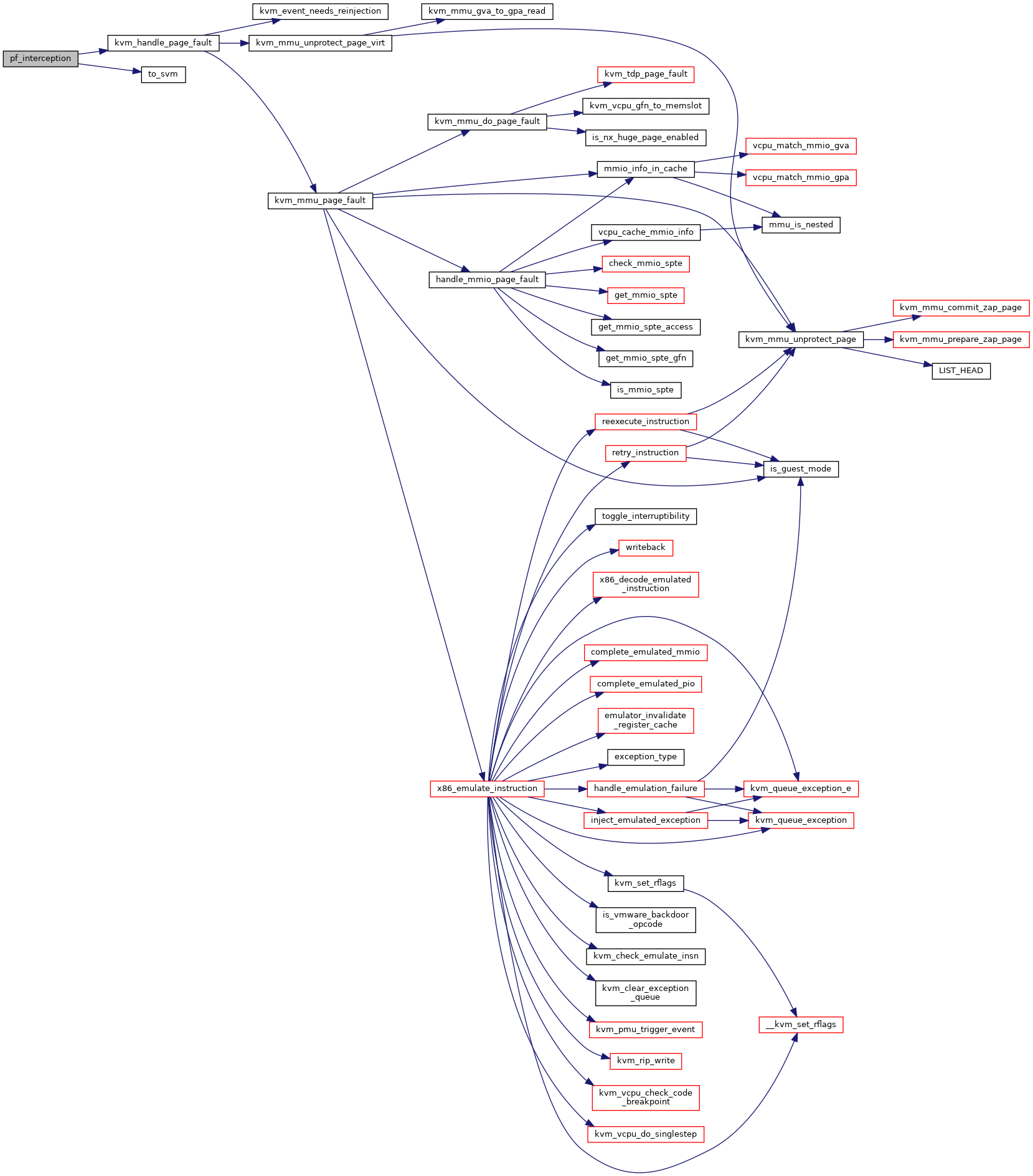

| static int | pf_interception (struct kvm_vcpu *vcpu) |

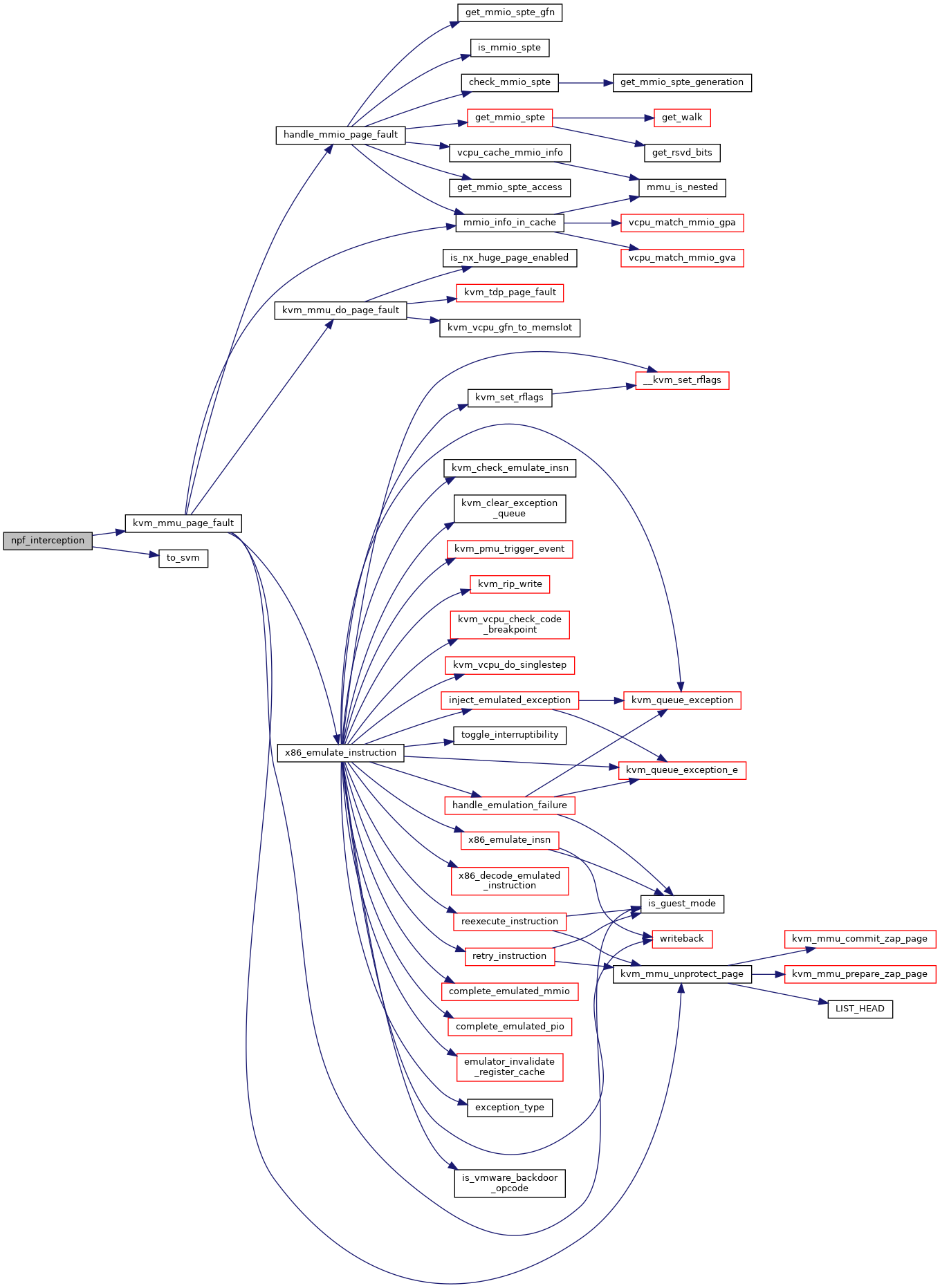

| static int | npf_interception (struct kvm_vcpu *vcpu) |

| static int | db_interception (struct kvm_vcpu *vcpu) |

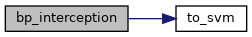

| static int | bp_interception (struct kvm_vcpu *vcpu) |

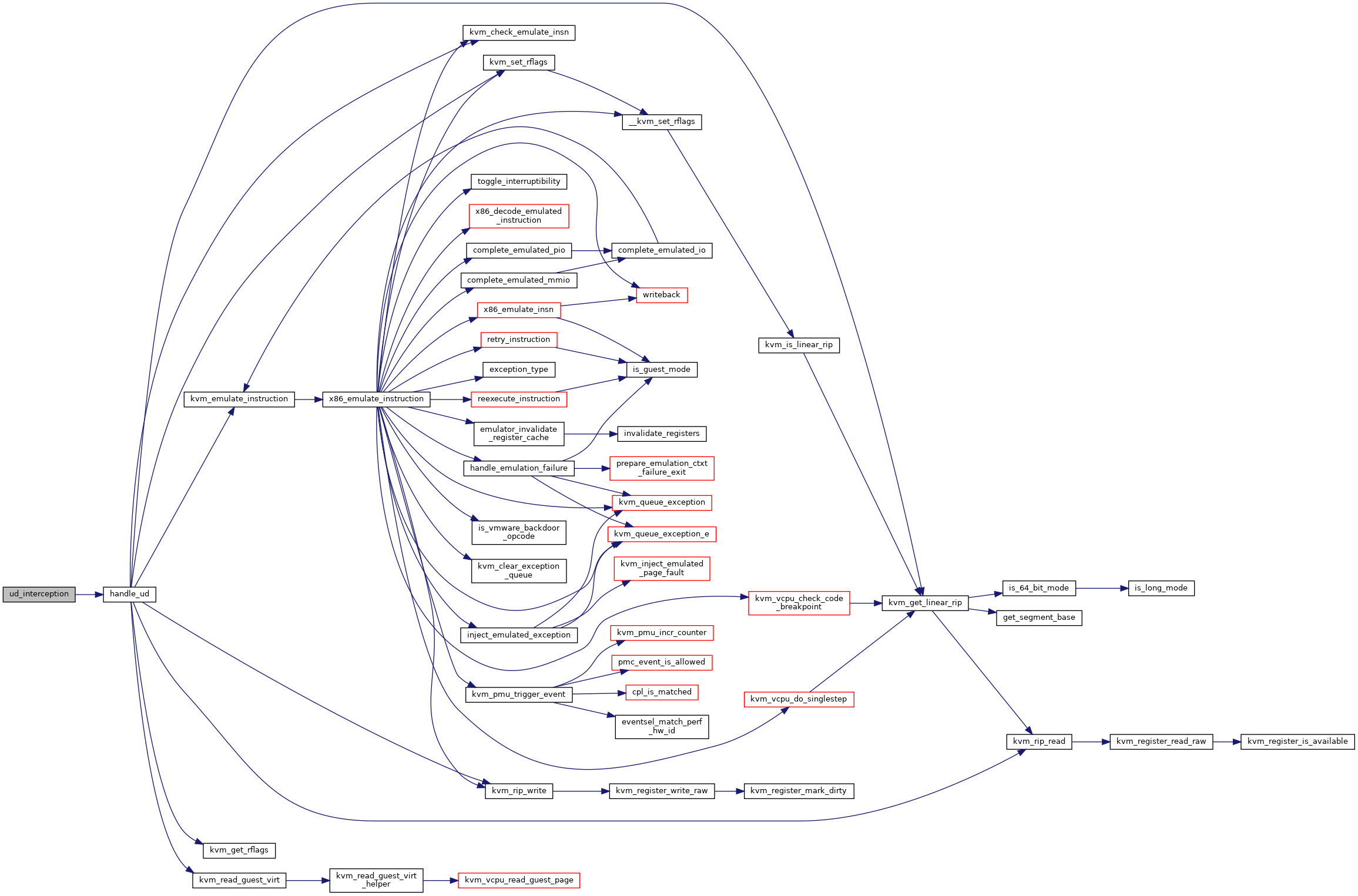

| static int | ud_interception (struct kvm_vcpu *vcpu) |

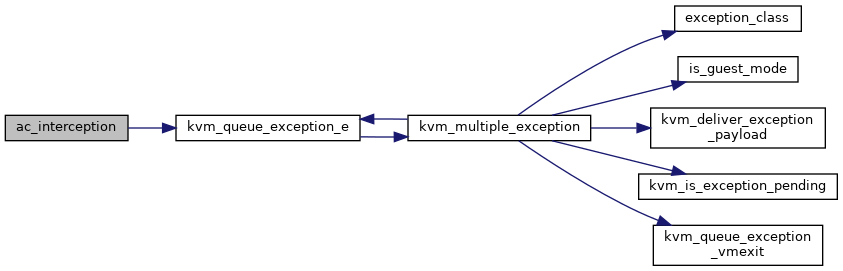

| static int | ac_interception (struct kvm_vcpu *vcpu) |

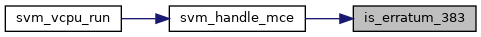

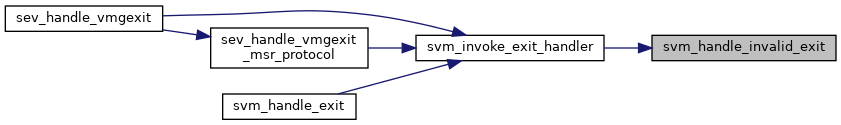

| static bool | is_erratum_383 (void) |

| static void | svm_handle_mce (struct kvm_vcpu *vcpu) |

| static int | mc_interception (struct kvm_vcpu *vcpu) |

| static int | shutdown_interception (struct kvm_vcpu *vcpu) |

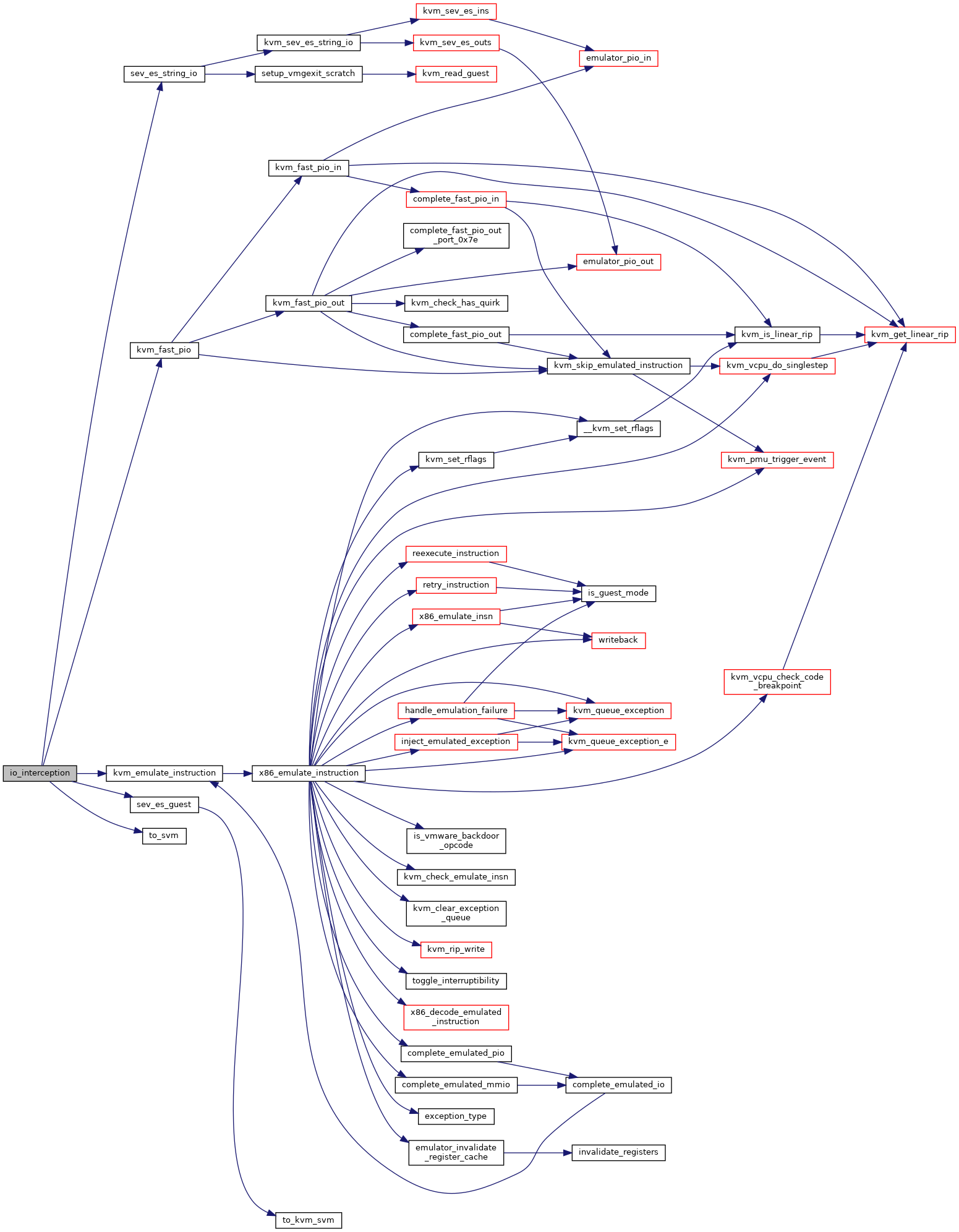

| static int | io_interception (struct kvm_vcpu *vcpu) |

| static int | nmi_interception (struct kvm_vcpu *vcpu) |

| static int | smi_interception (struct kvm_vcpu *vcpu) |

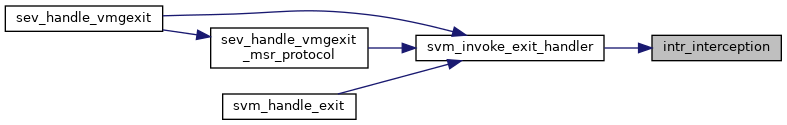

| static int | intr_interception (struct kvm_vcpu *vcpu) |

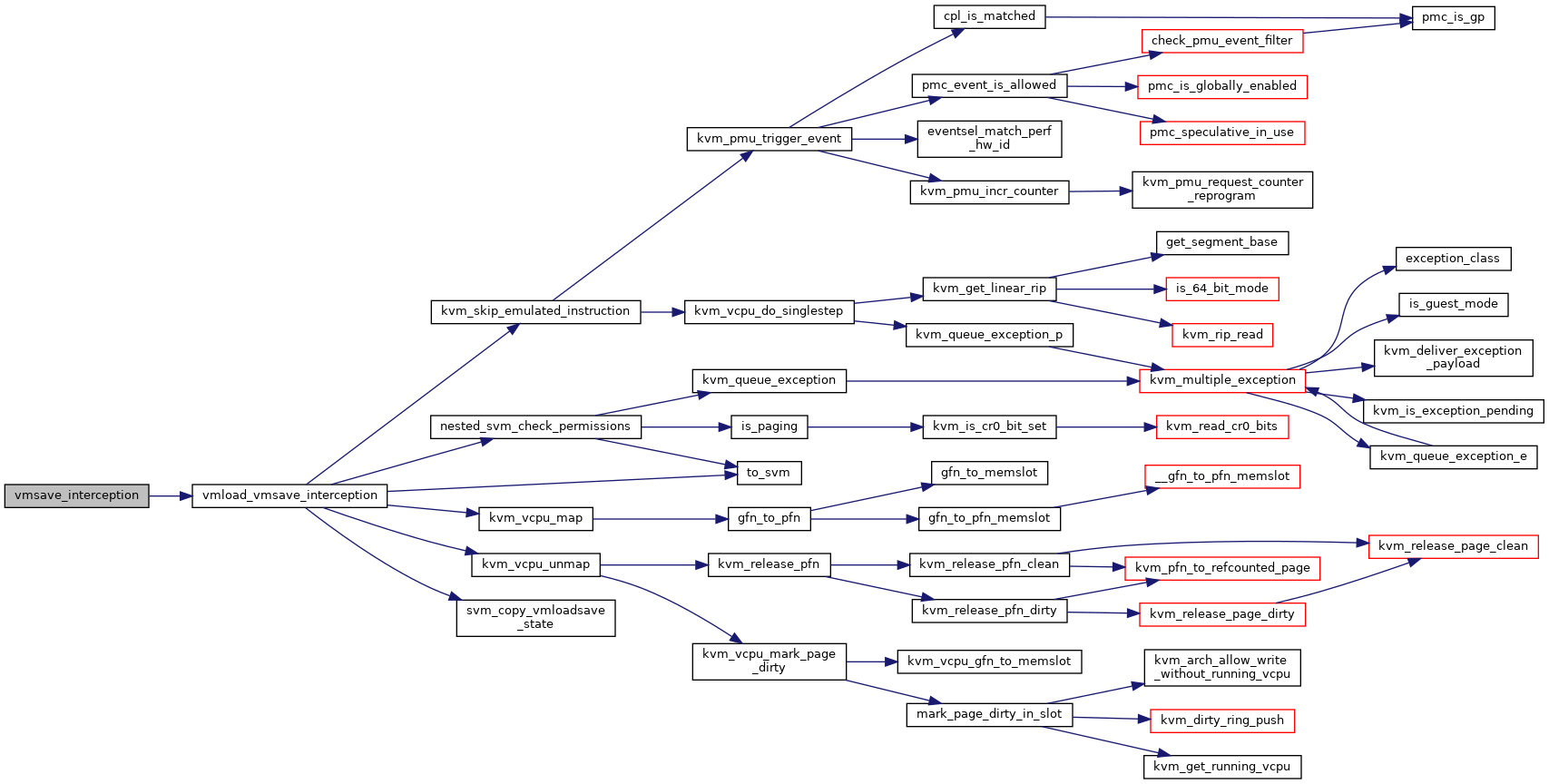

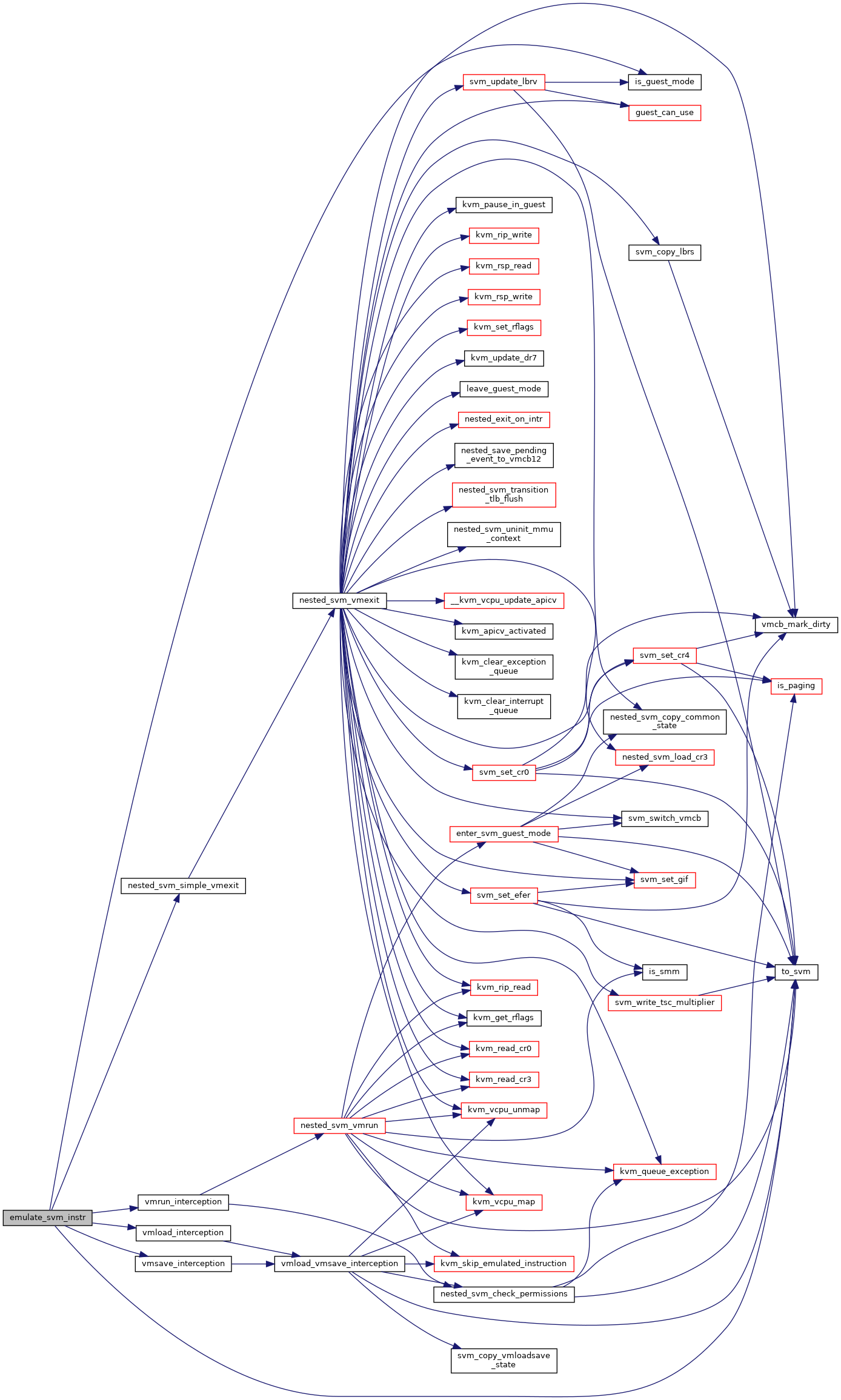

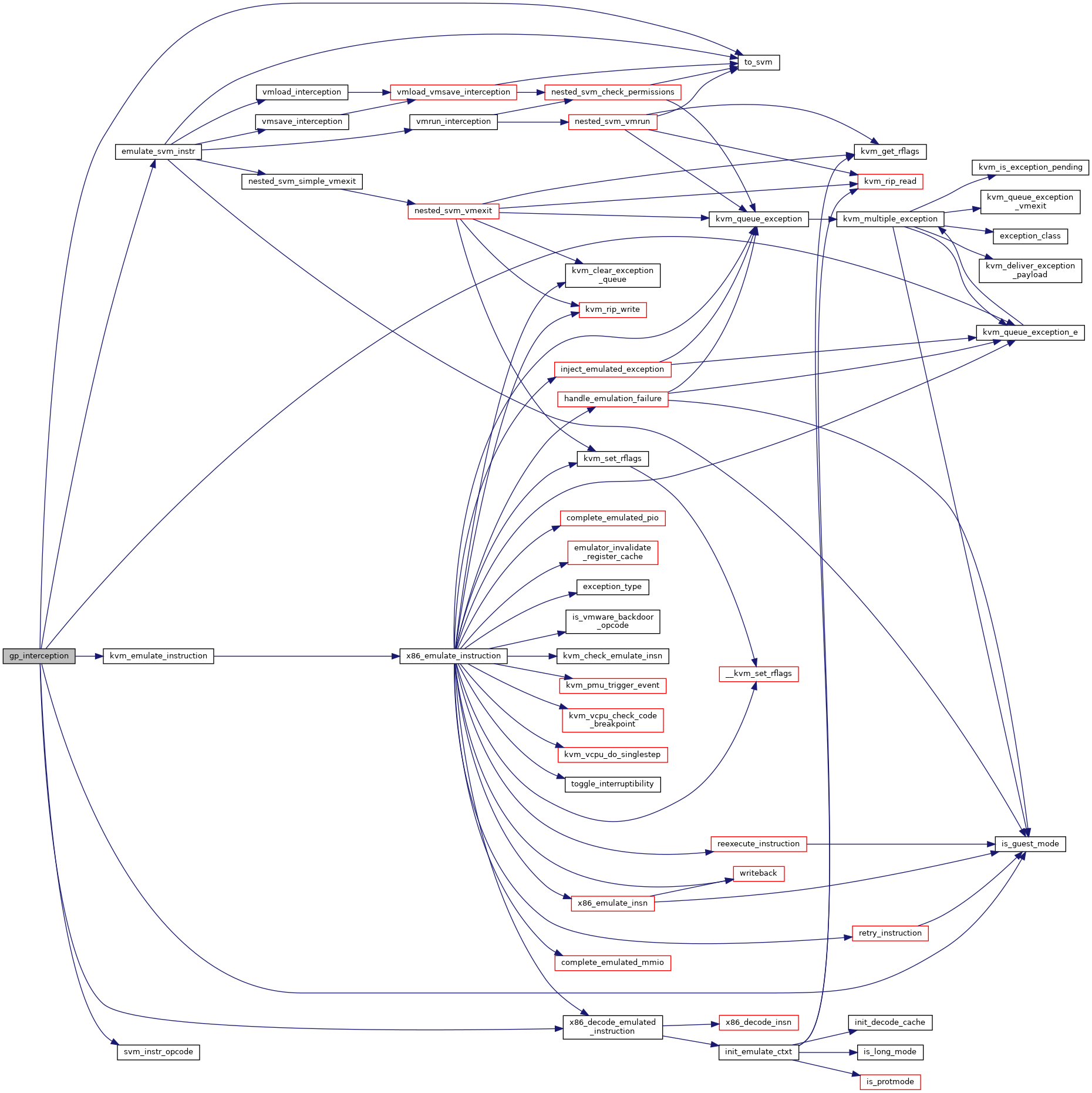

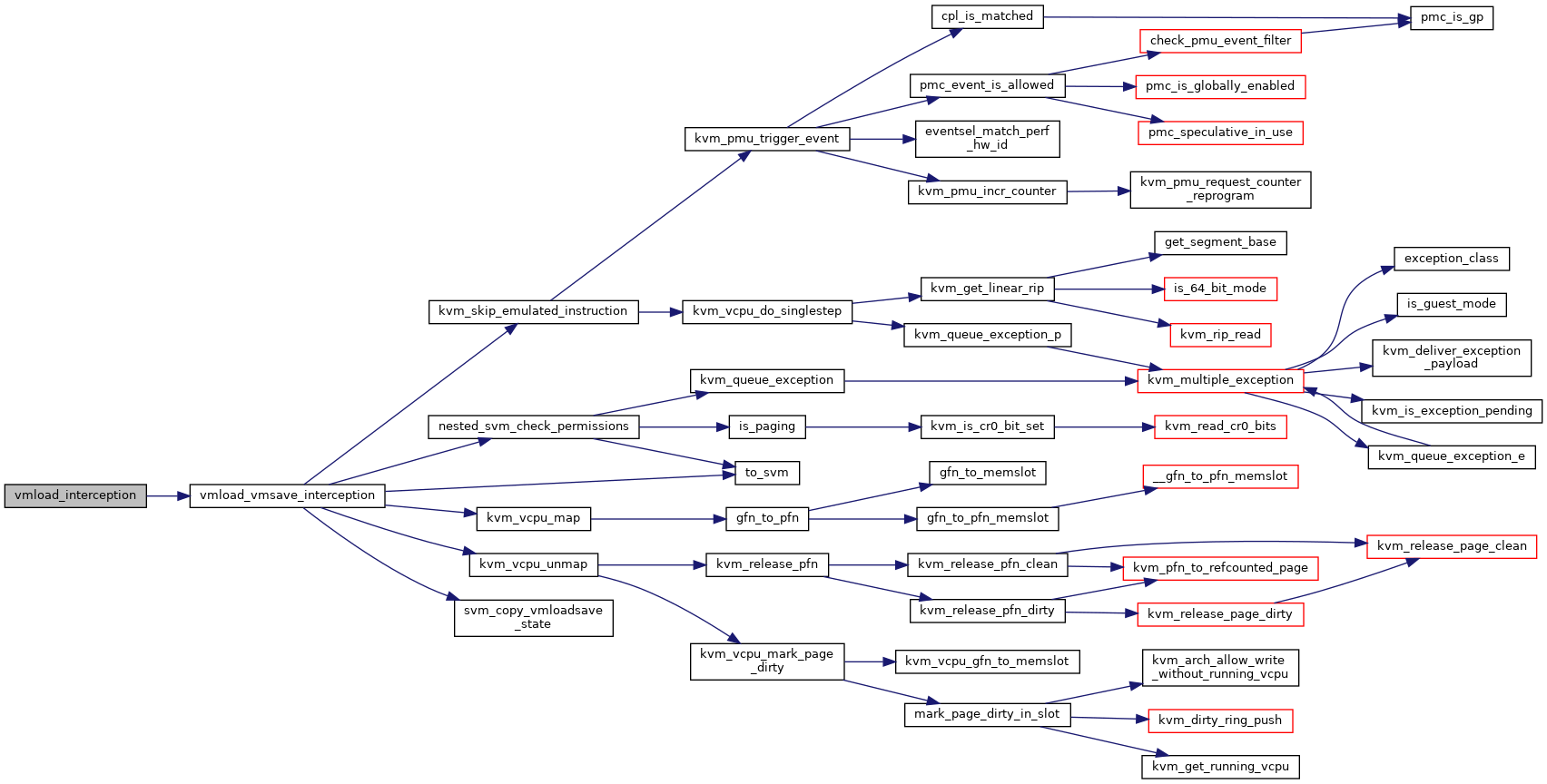

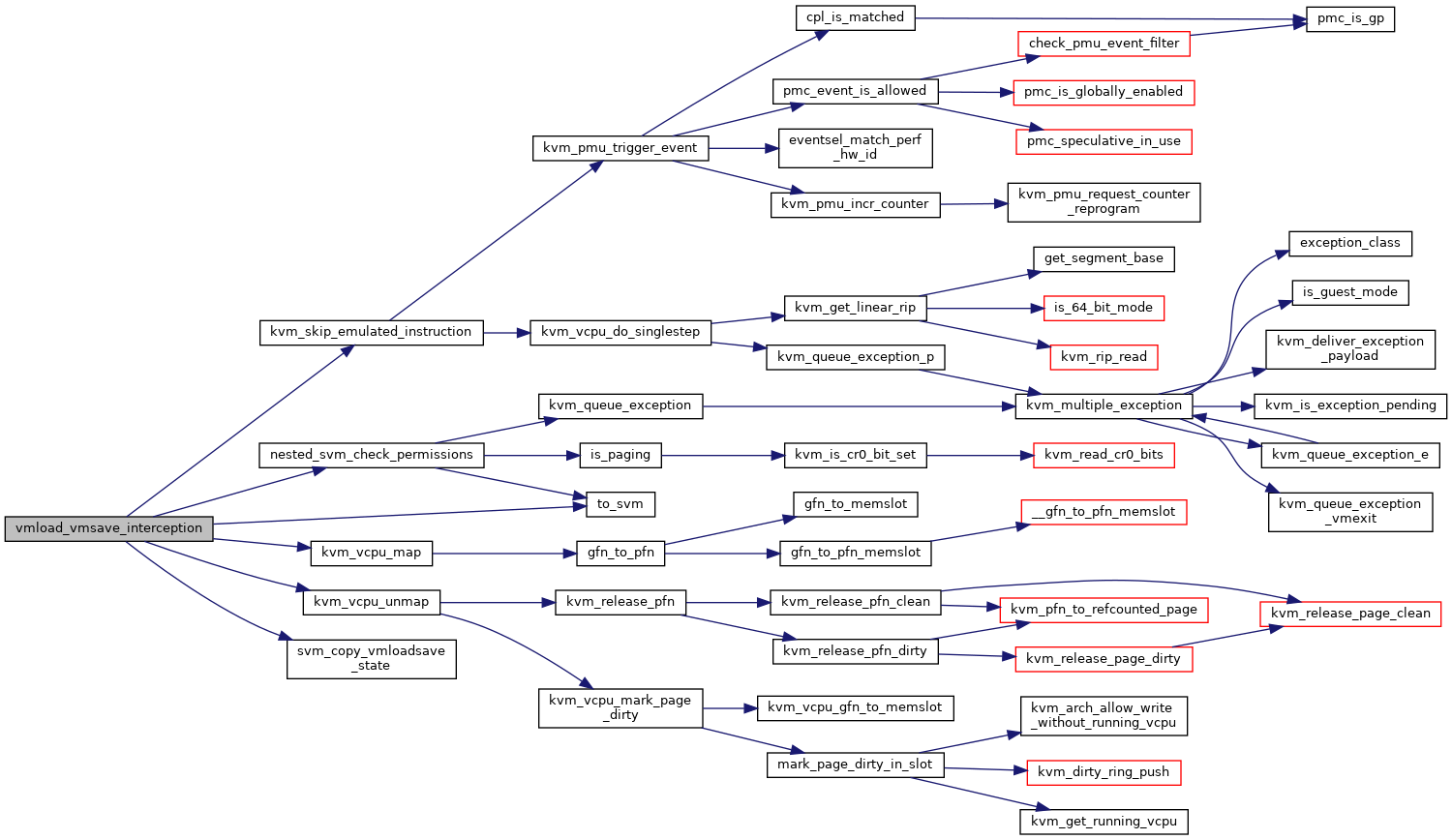

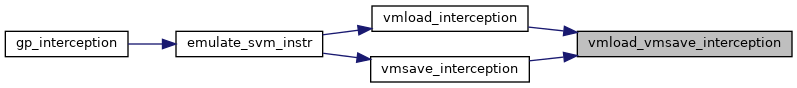

| static int | vmload_vmsave_interception (struct kvm_vcpu *vcpu, bool vmload) |

| static int | vmload_interception (struct kvm_vcpu *vcpu) |

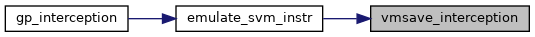

| static int | vmsave_interception (struct kvm_vcpu *vcpu) |

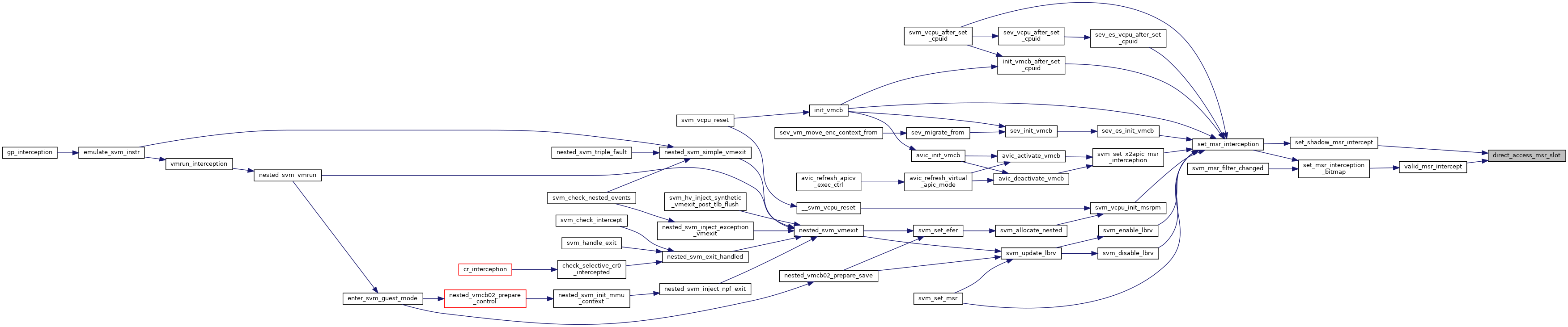

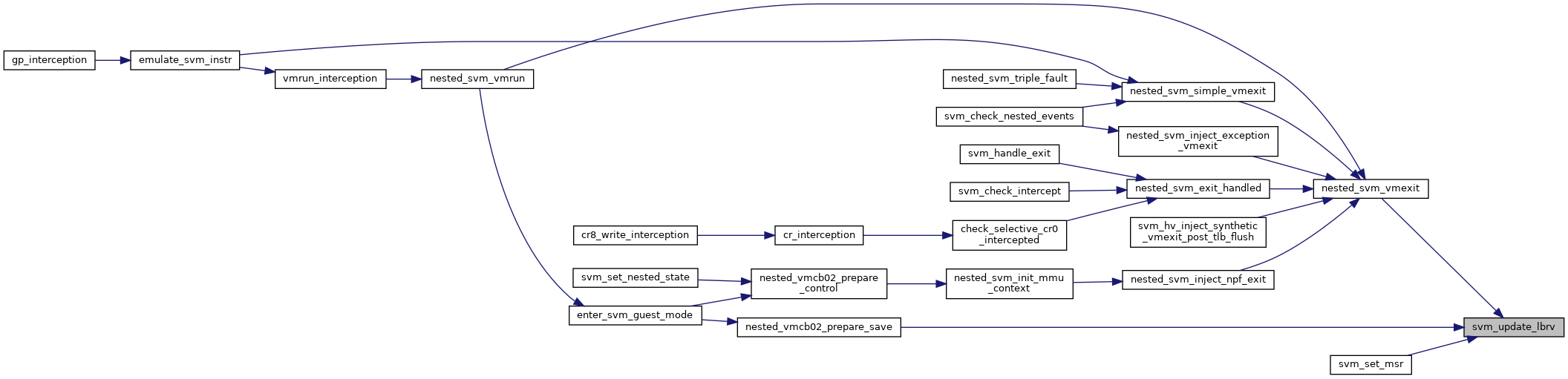

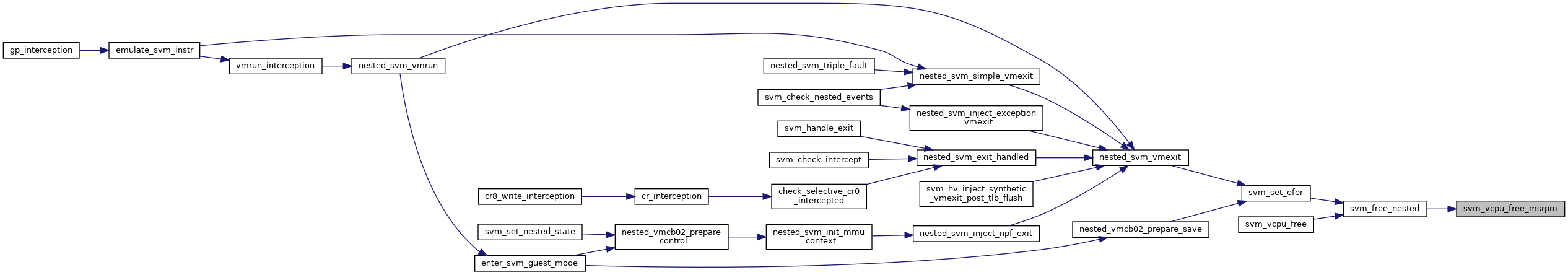

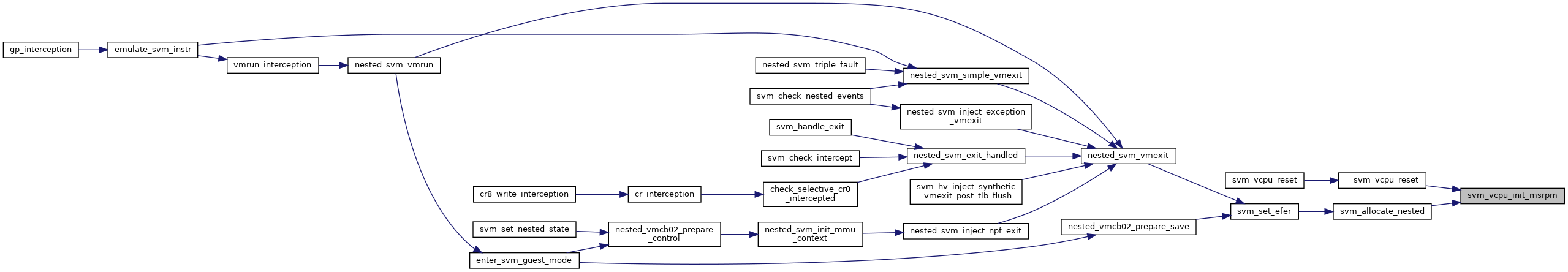

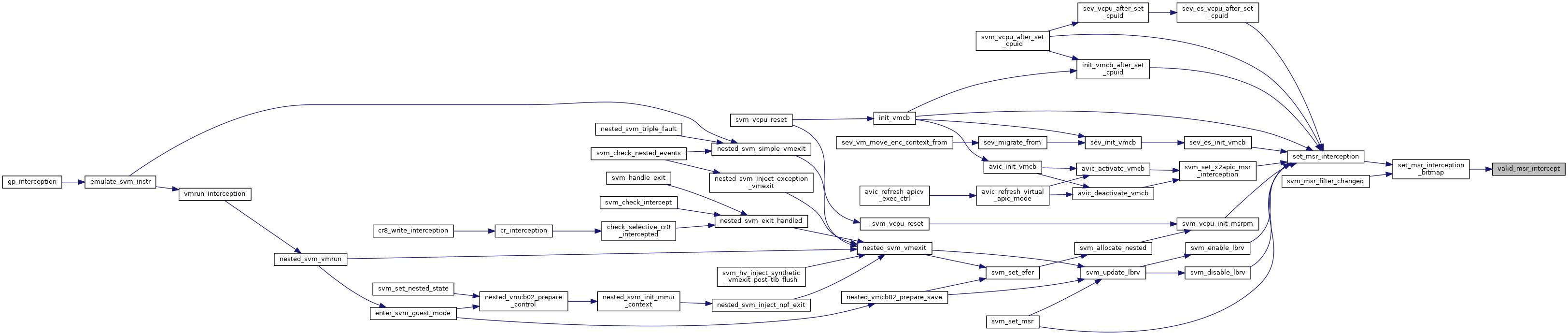

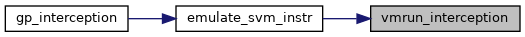

| static int | vmrun_interception (struct kvm_vcpu *vcpu) |

| static int | svm_instr_opcode (struct kvm_vcpu *vcpu) |

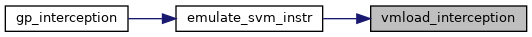

| static int | emulate_svm_instr (struct kvm_vcpu *vcpu, int opcode) |

| static int | gp_interception (struct kvm_vcpu *vcpu) |

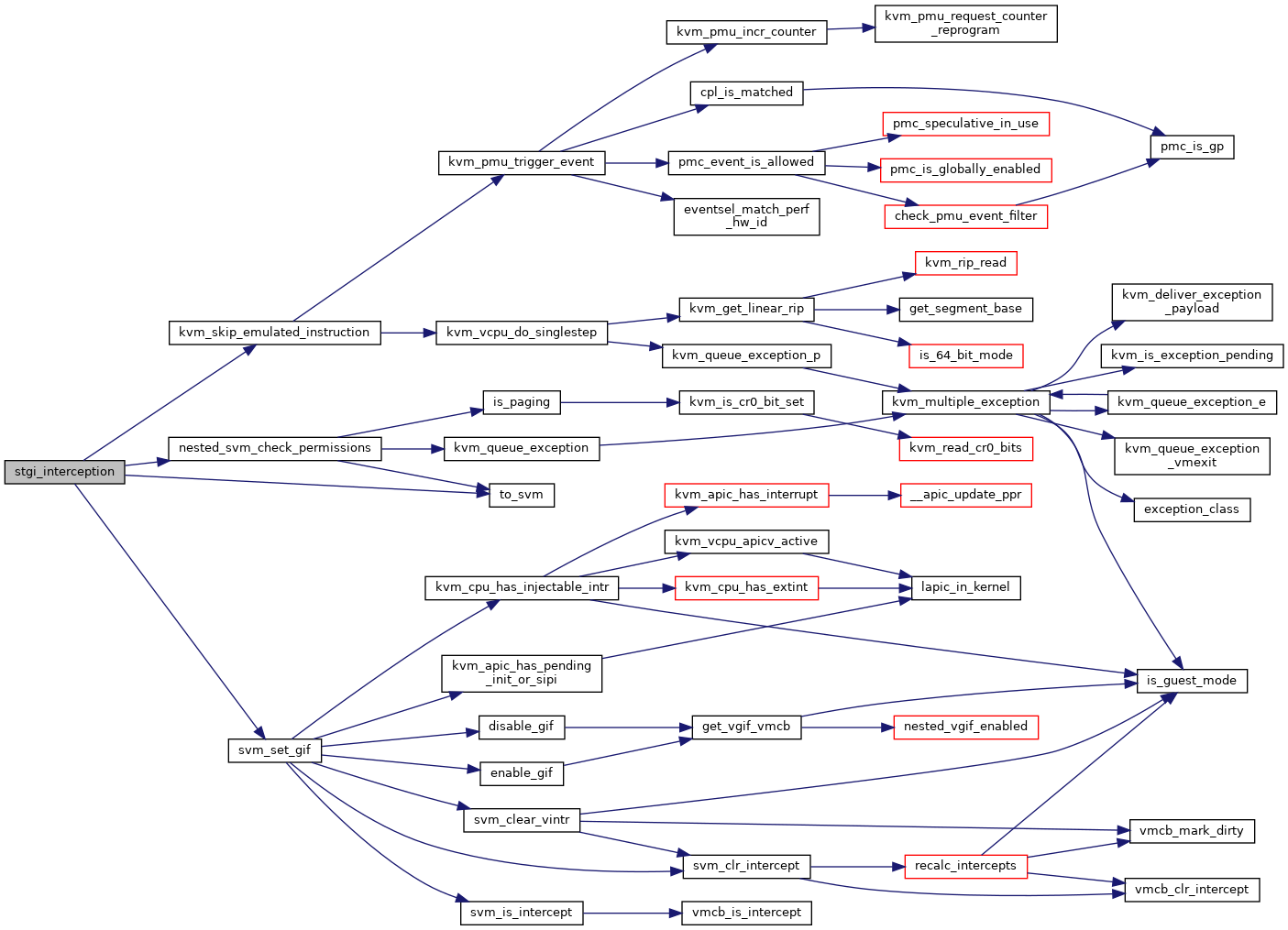

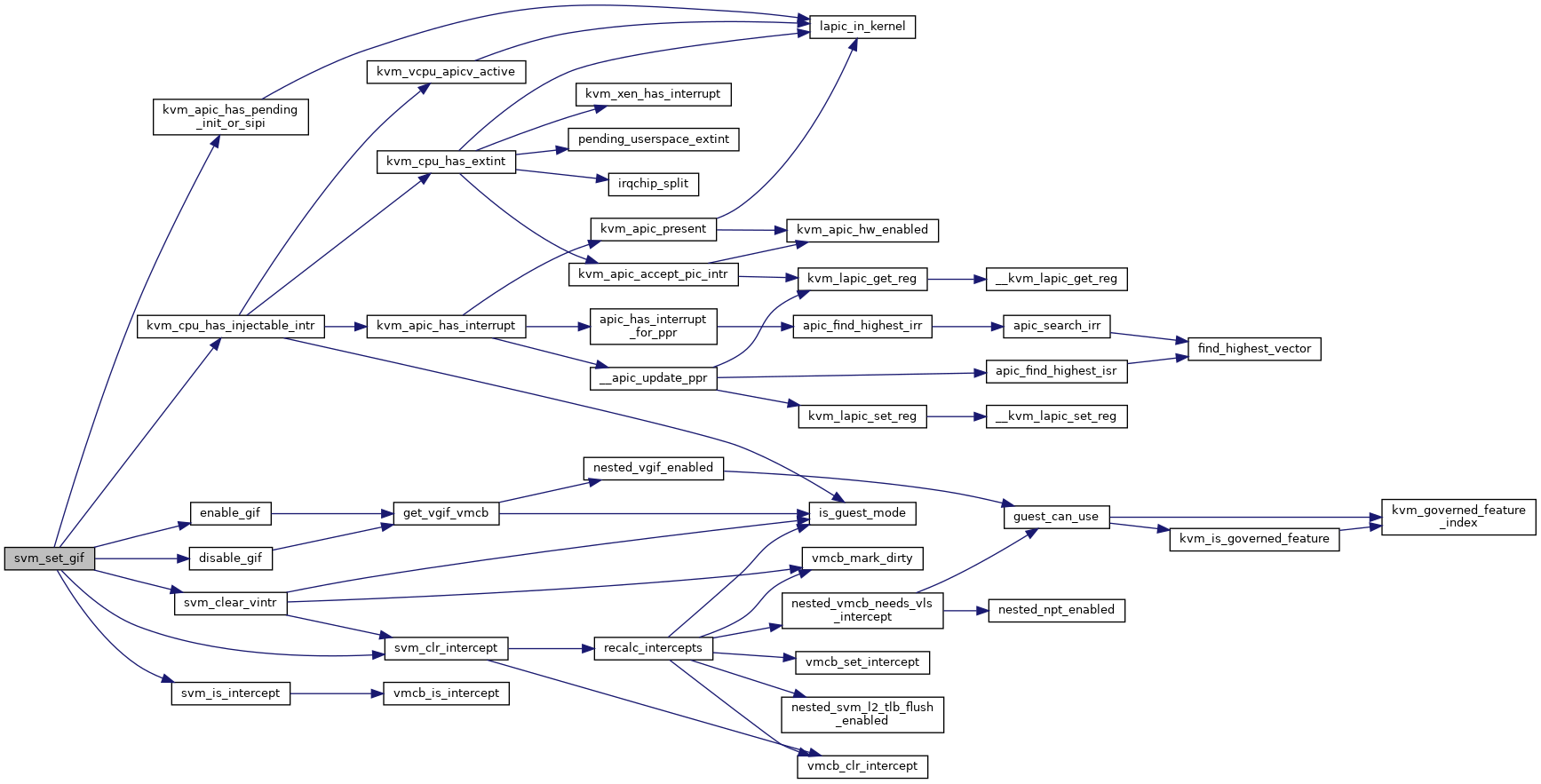

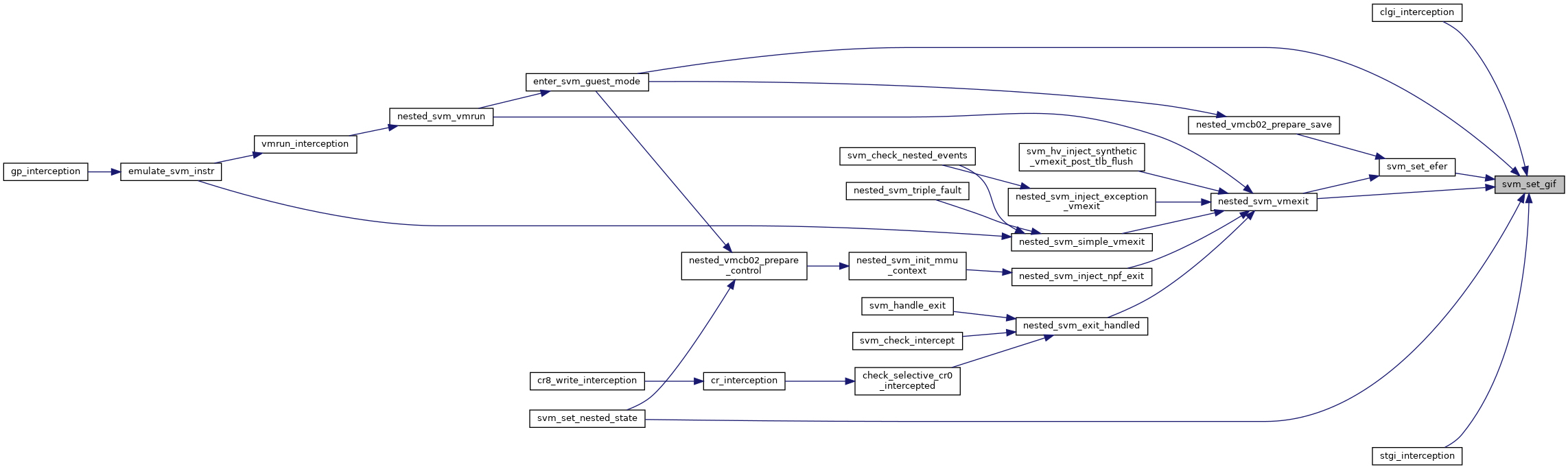

| void | svm_set_gif (struct vcpu_svm *svm, bool value) |

| static int | stgi_interception (struct kvm_vcpu *vcpu) |

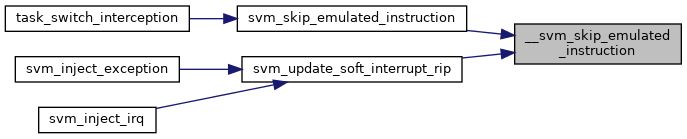

| static int | clgi_interception (struct kvm_vcpu *vcpu) |

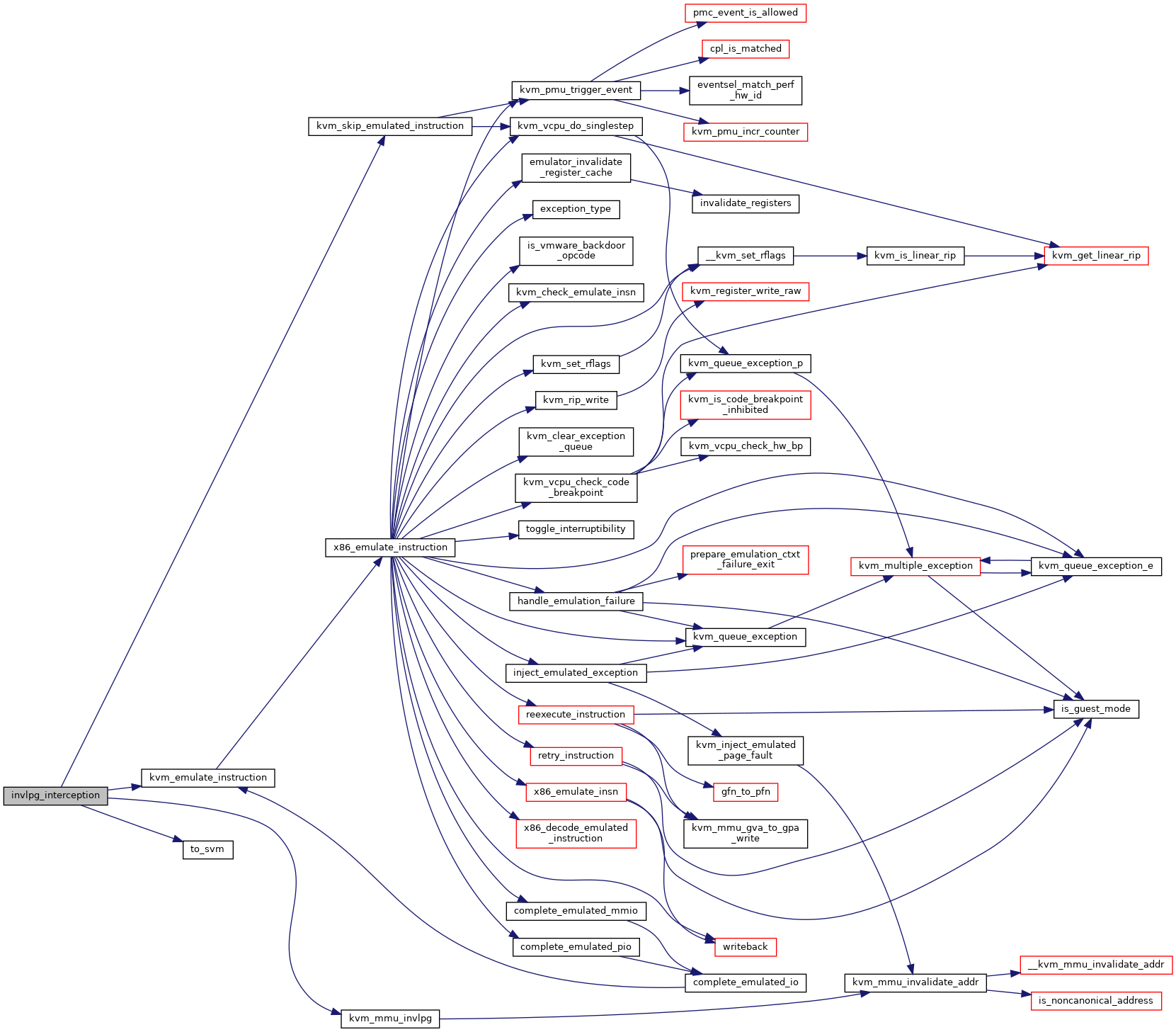

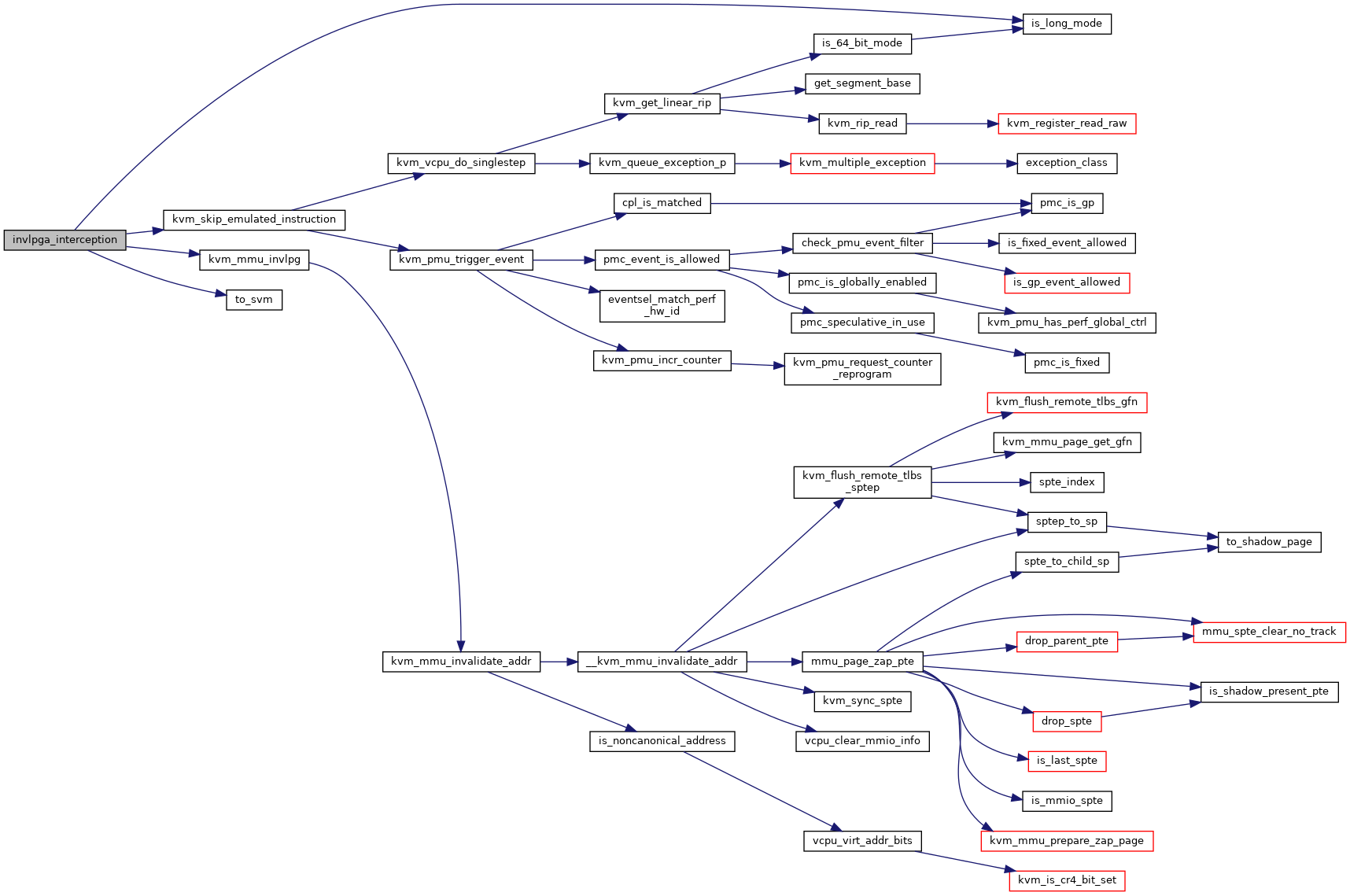

| static int | invlpga_interception (struct kvm_vcpu *vcpu) |

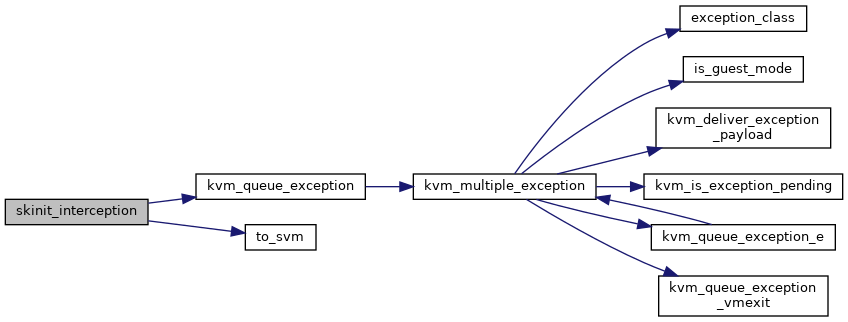

| static int | skinit_interception (struct kvm_vcpu *vcpu) |

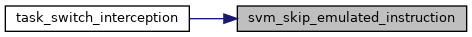

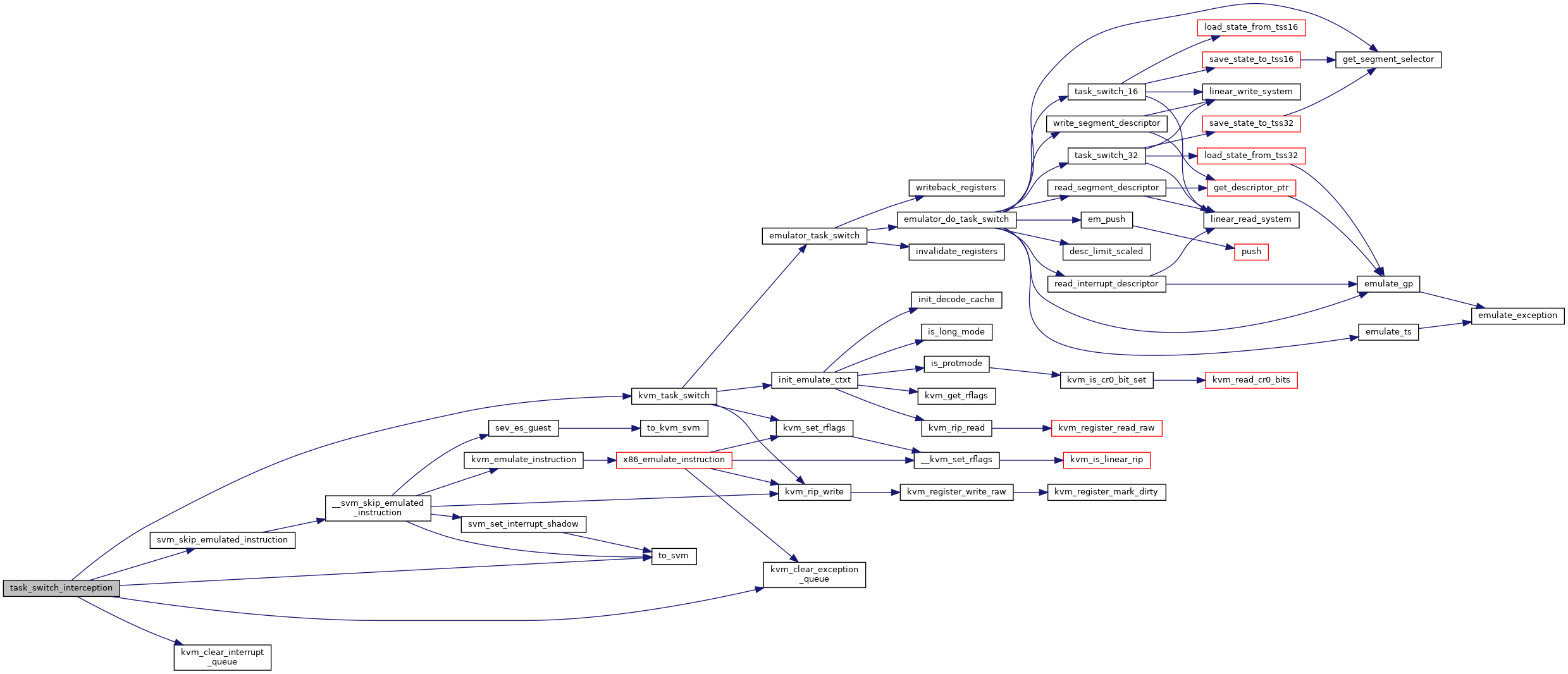

| static int | task_switch_interception (struct kvm_vcpu *vcpu) |

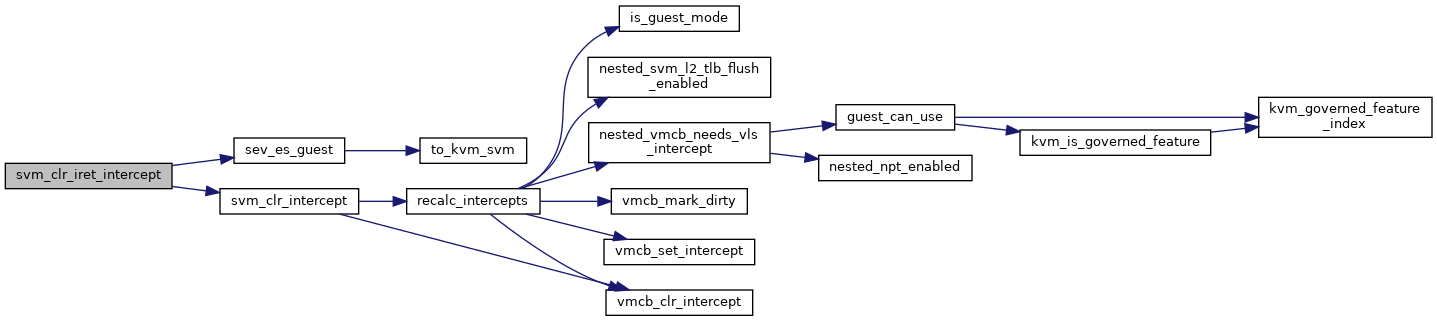

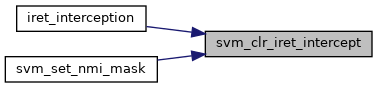

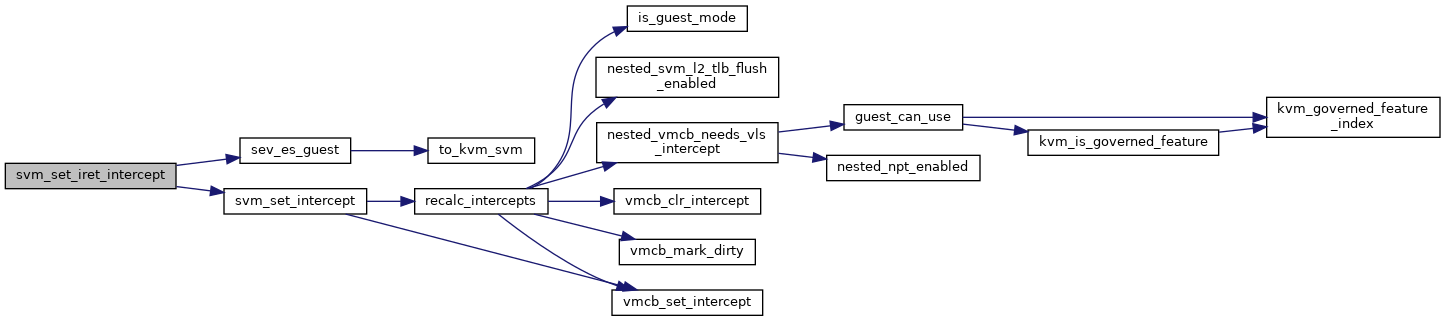

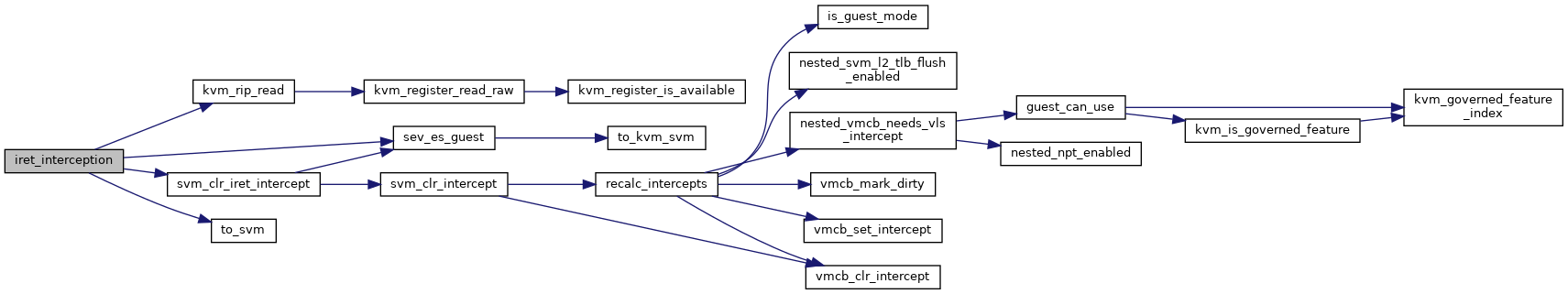

| static void | svm_clr_iret_intercept (struct vcpu_svm *svm) |

| static void | svm_set_iret_intercept (struct vcpu_svm *svm) |

| static int | iret_interception (struct kvm_vcpu *vcpu) |

| static int | invlpg_interception (struct kvm_vcpu *vcpu) |

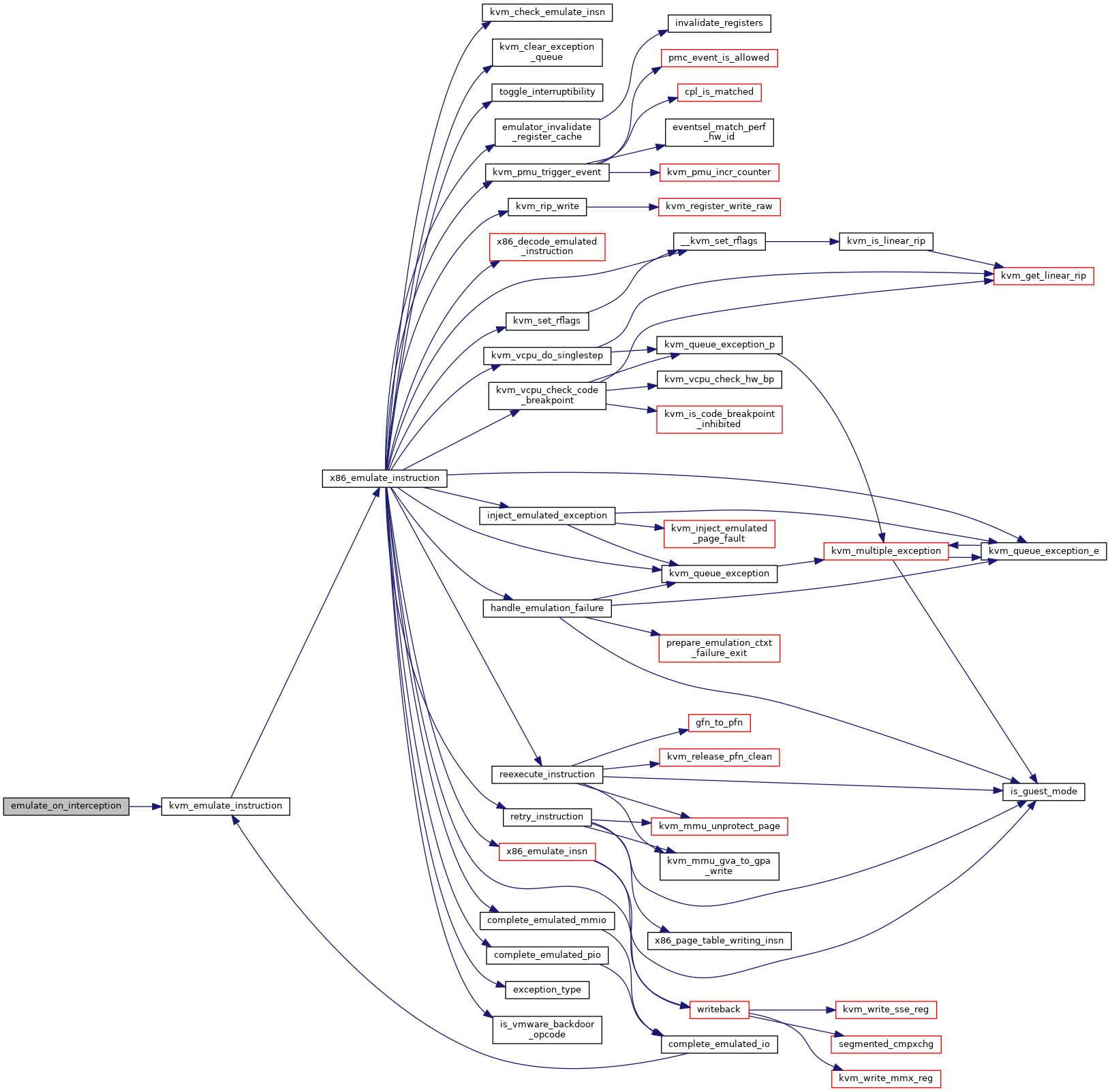

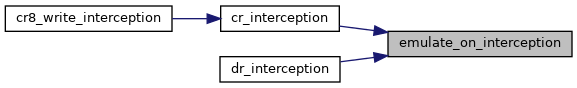

| static int | emulate_on_interception (struct kvm_vcpu *vcpu) |

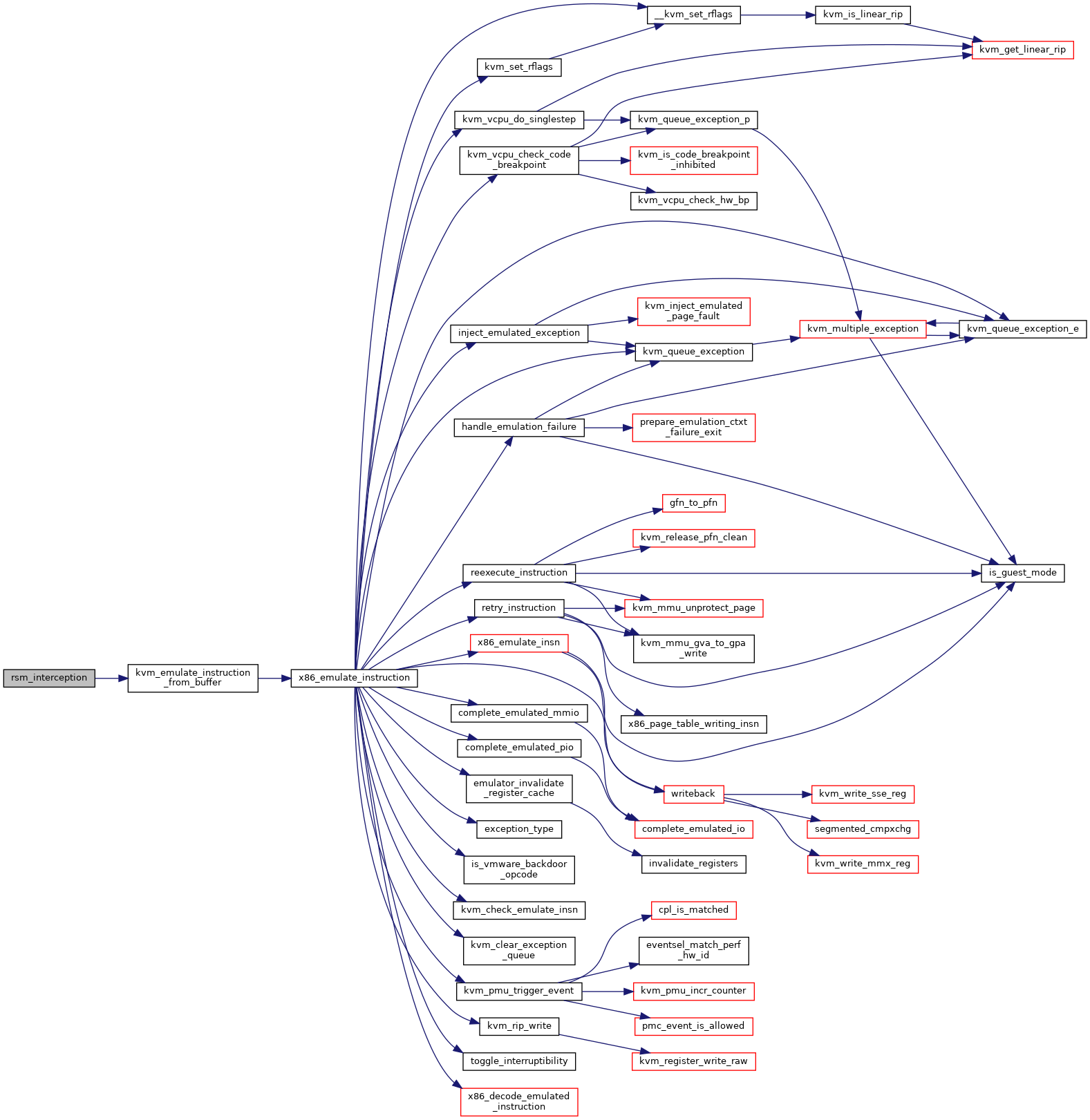

| static int | rsm_interception (struct kvm_vcpu *vcpu) |

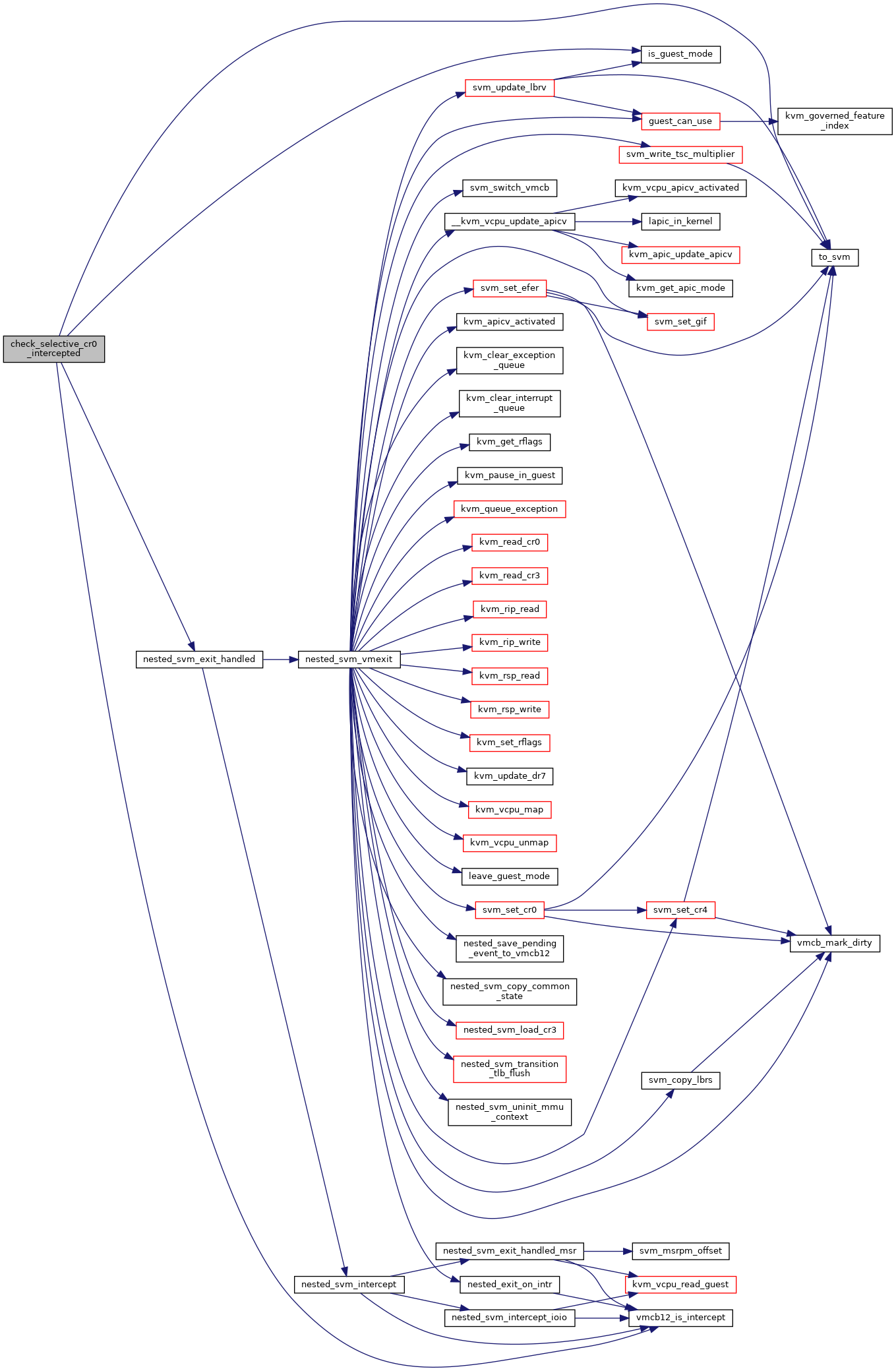

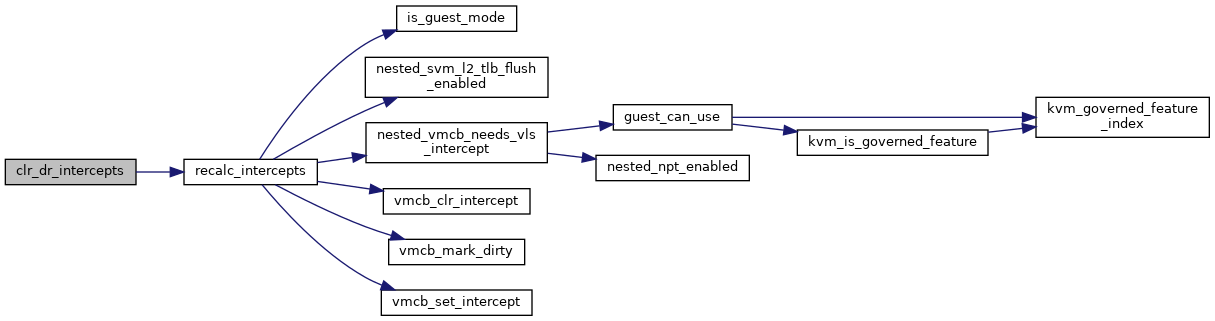

| static bool | check_selective_cr0_intercepted (struct kvm_vcpu *vcpu, unsigned long val) |

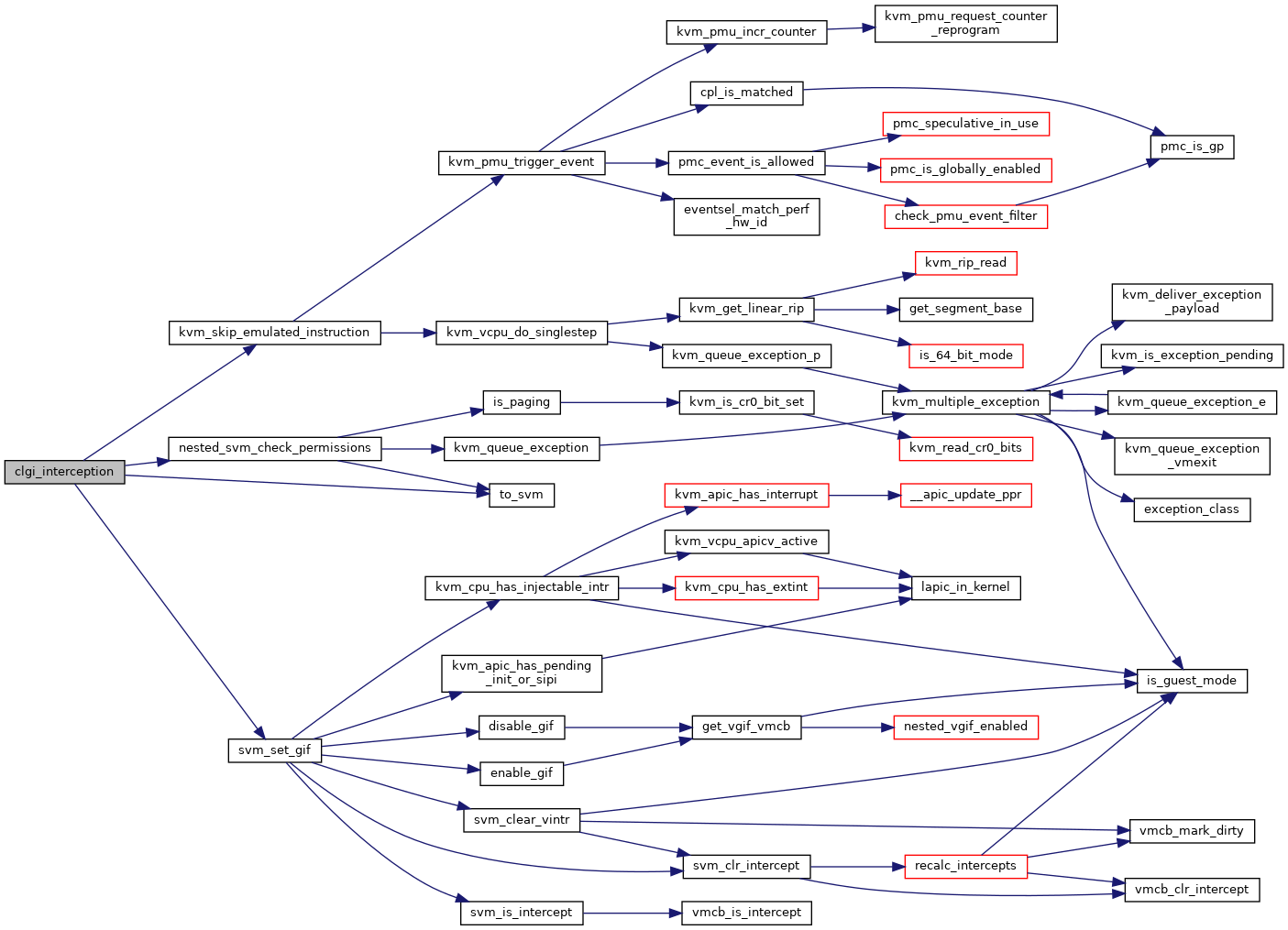

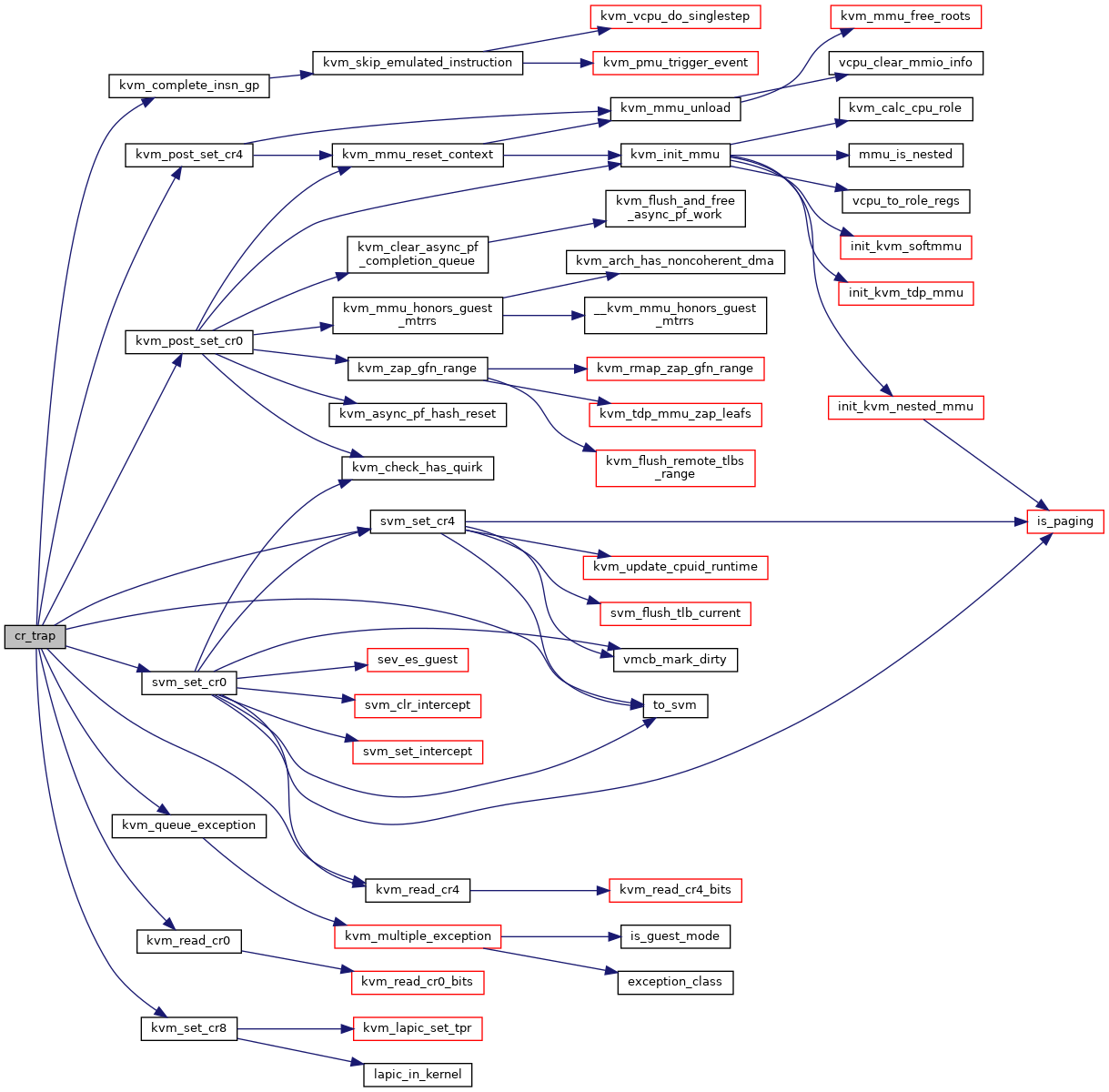

| static int | cr_interception (struct kvm_vcpu *vcpu) |

| static int | cr_trap (struct kvm_vcpu *vcpu) |

| static int | dr_interception (struct kvm_vcpu *vcpu) |

| static int | cr8_write_interception (struct kvm_vcpu *vcpu) |

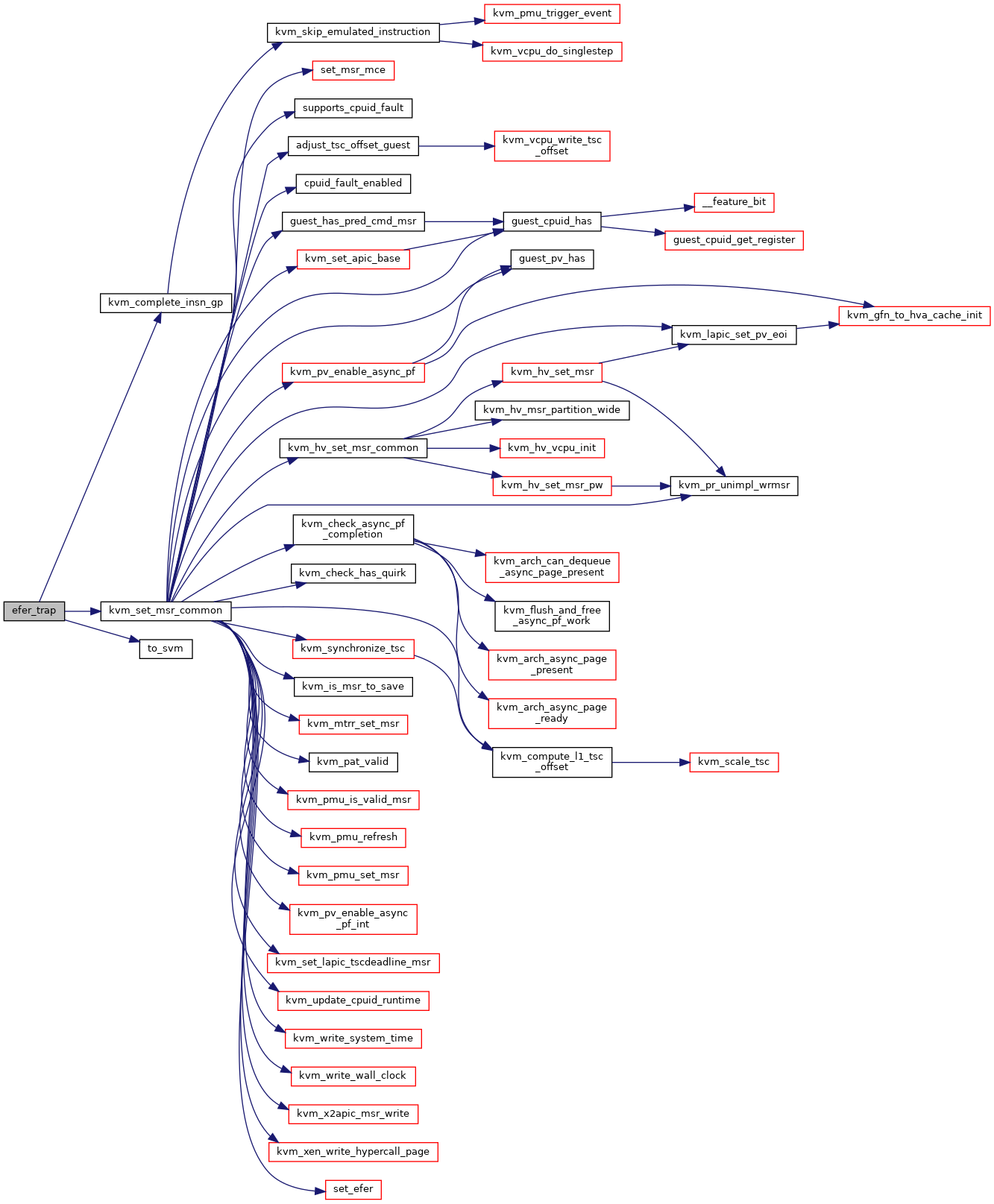

| static int | efer_trap (struct kvm_vcpu *vcpu) |

| static int | svm_get_msr_feature (struct kvm_msr_entry *msr) |

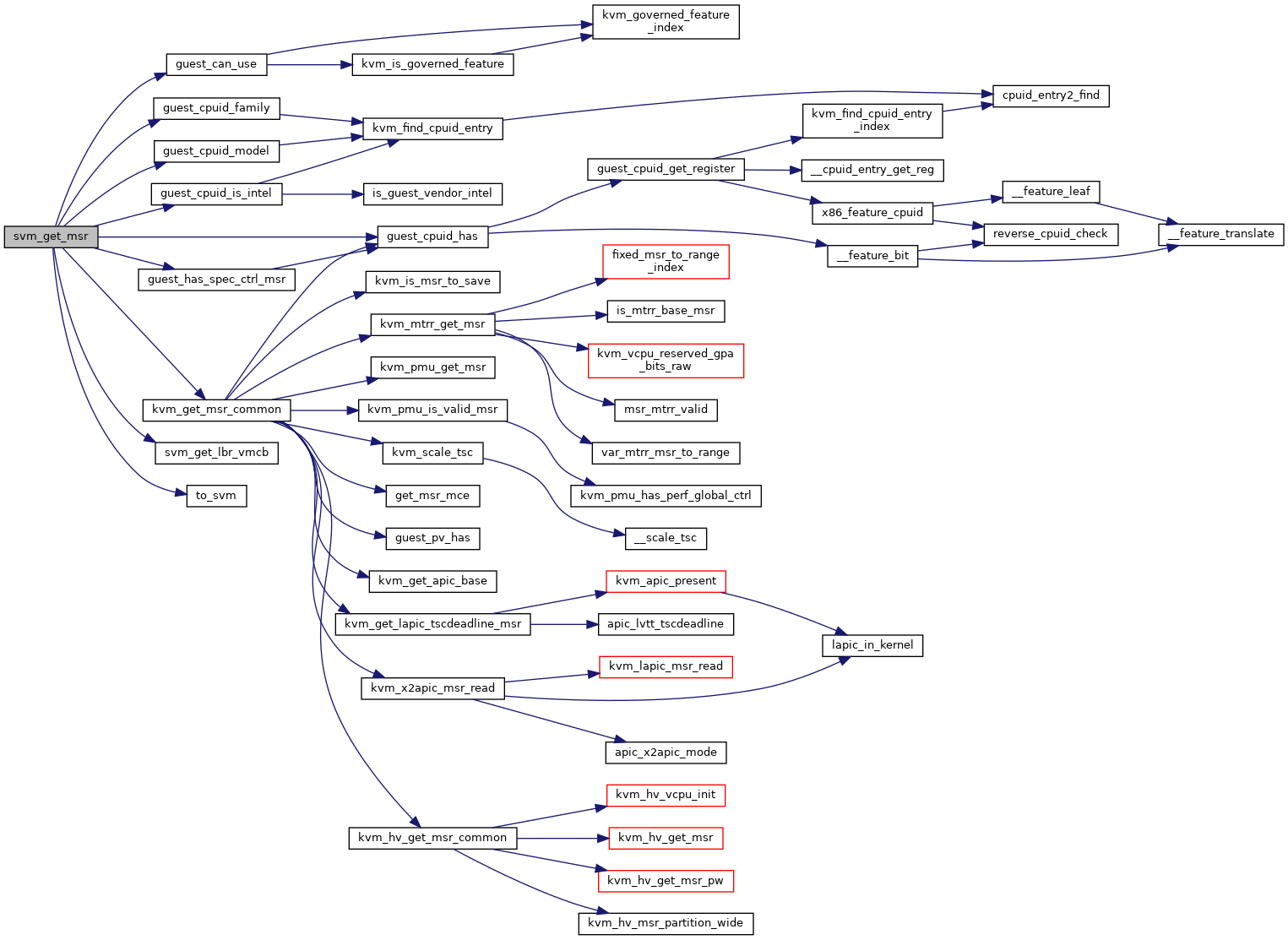

| static int | svm_get_msr (struct kvm_vcpu *vcpu, struct msr_data *msr_info) |

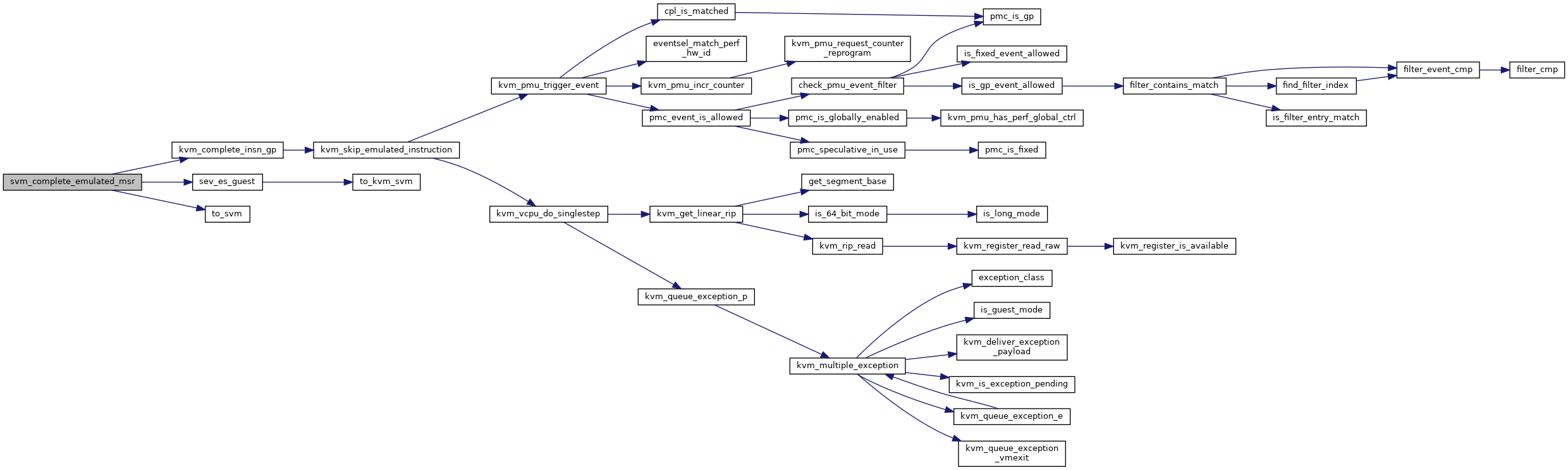

| static int | svm_complete_emulated_msr (struct kvm_vcpu *vcpu, int err) |

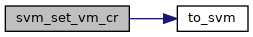

| static int | svm_set_vm_cr (struct kvm_vcpu *vcpu, u64 data) |

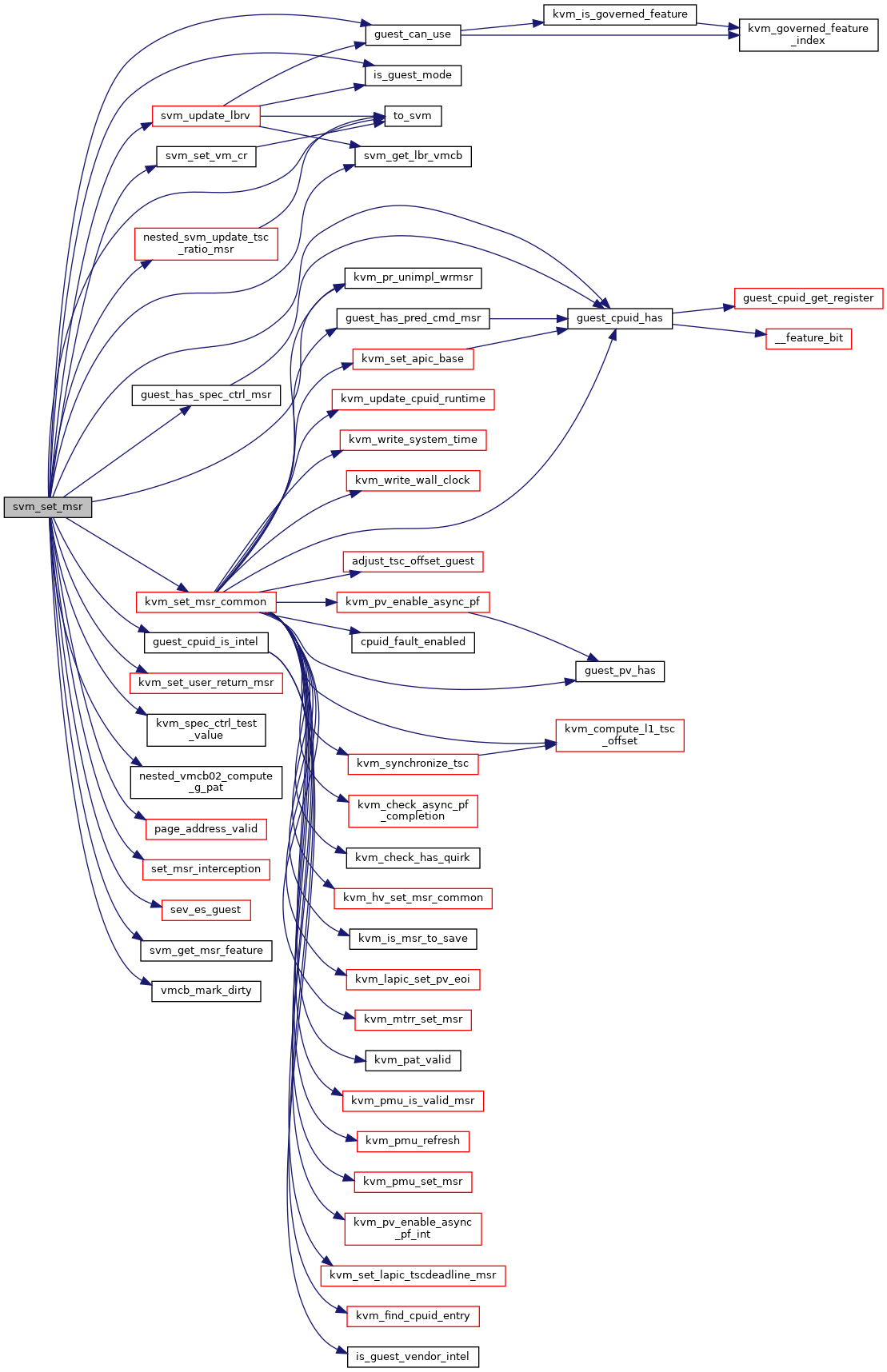

| static int | svm_set_msr (struct kvm_vcpu *vcpu, struct msr_data *msr) |

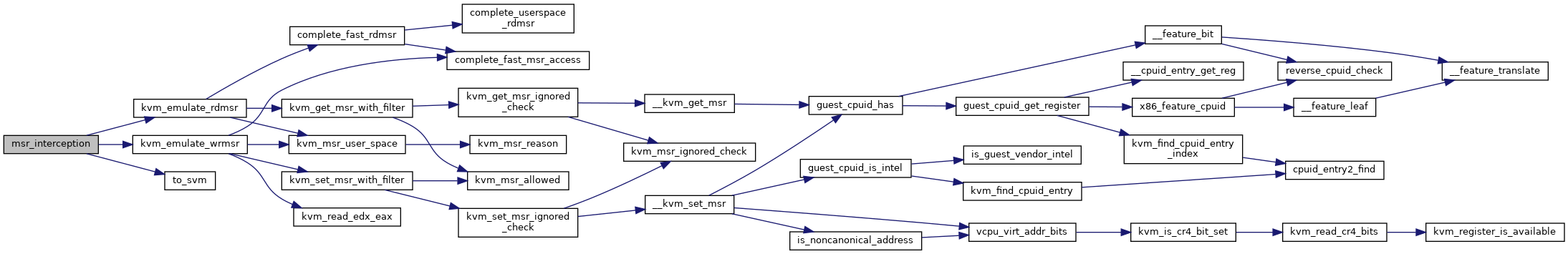

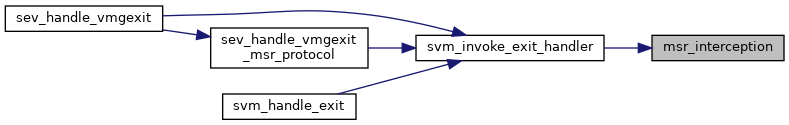

| static int | msr_interception (struct kvm_vcpu *vcpu) |

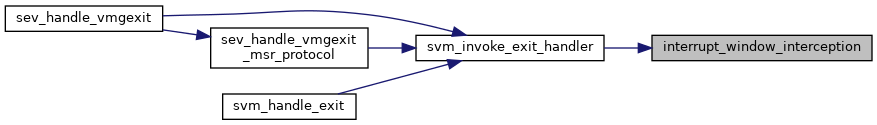

| static int | interrupt_window_interception (struct kvm_vcpu *vcpu) |

| static int | pause_interception (struct kvm_vcpu *vcpu) |

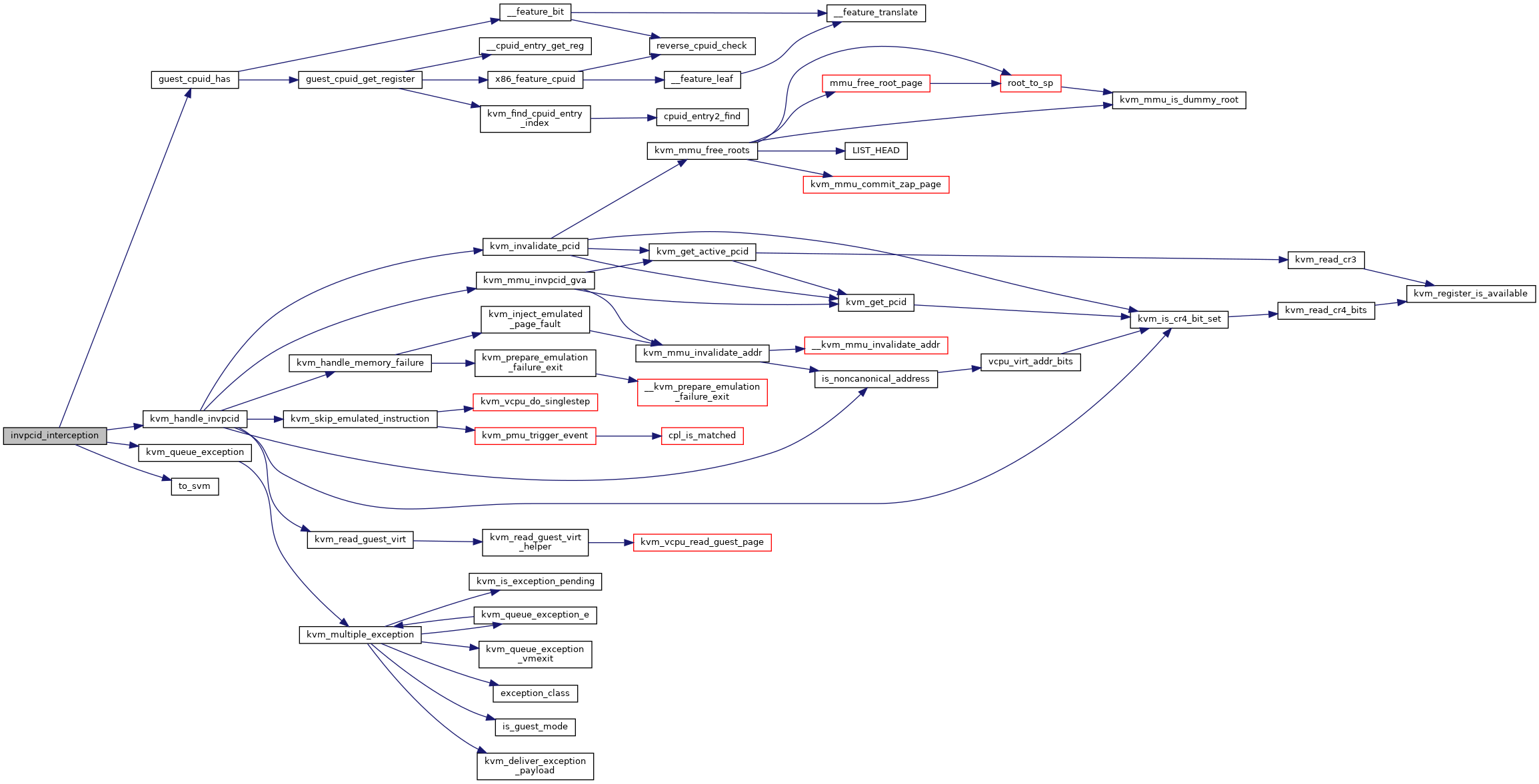

| static int | invpcid_interception (struct kvm_vcpu *vcpu) |

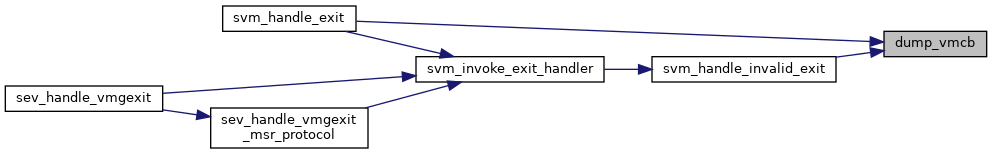

| static void | dump_vmcb (struct kvm_vcpu *vcpu) |

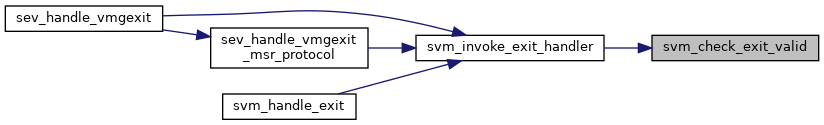

| static bool | svm_check_exit_valid (u64 exit_code) |

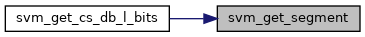

| static int | svm_handle_invalid_exit (struct kvm_vcpu *vcpu, u64 exit_code) |

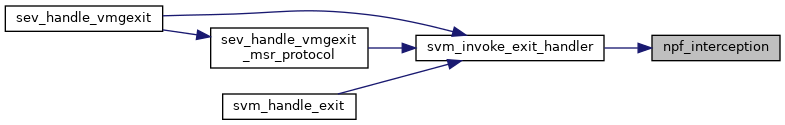

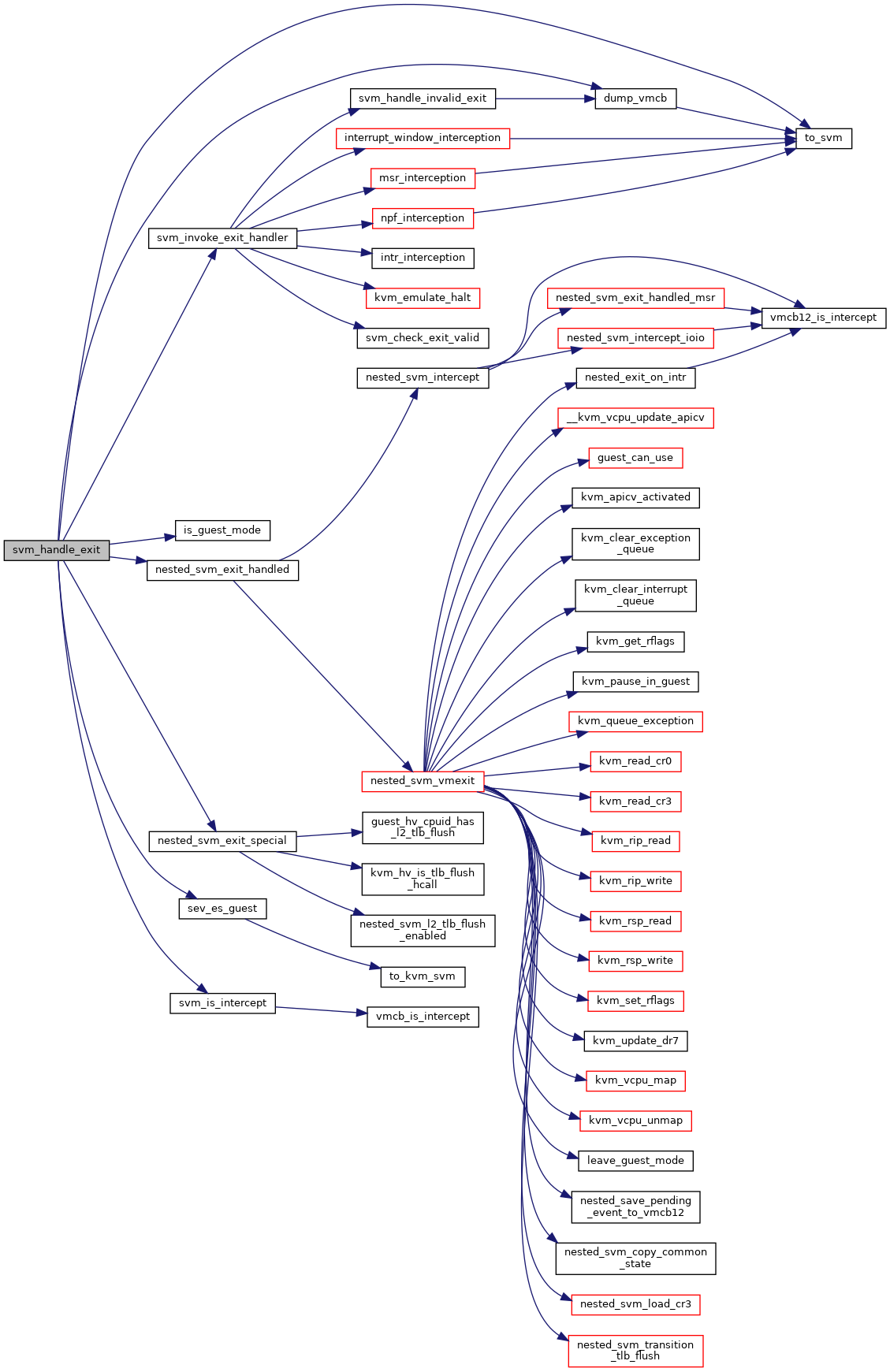

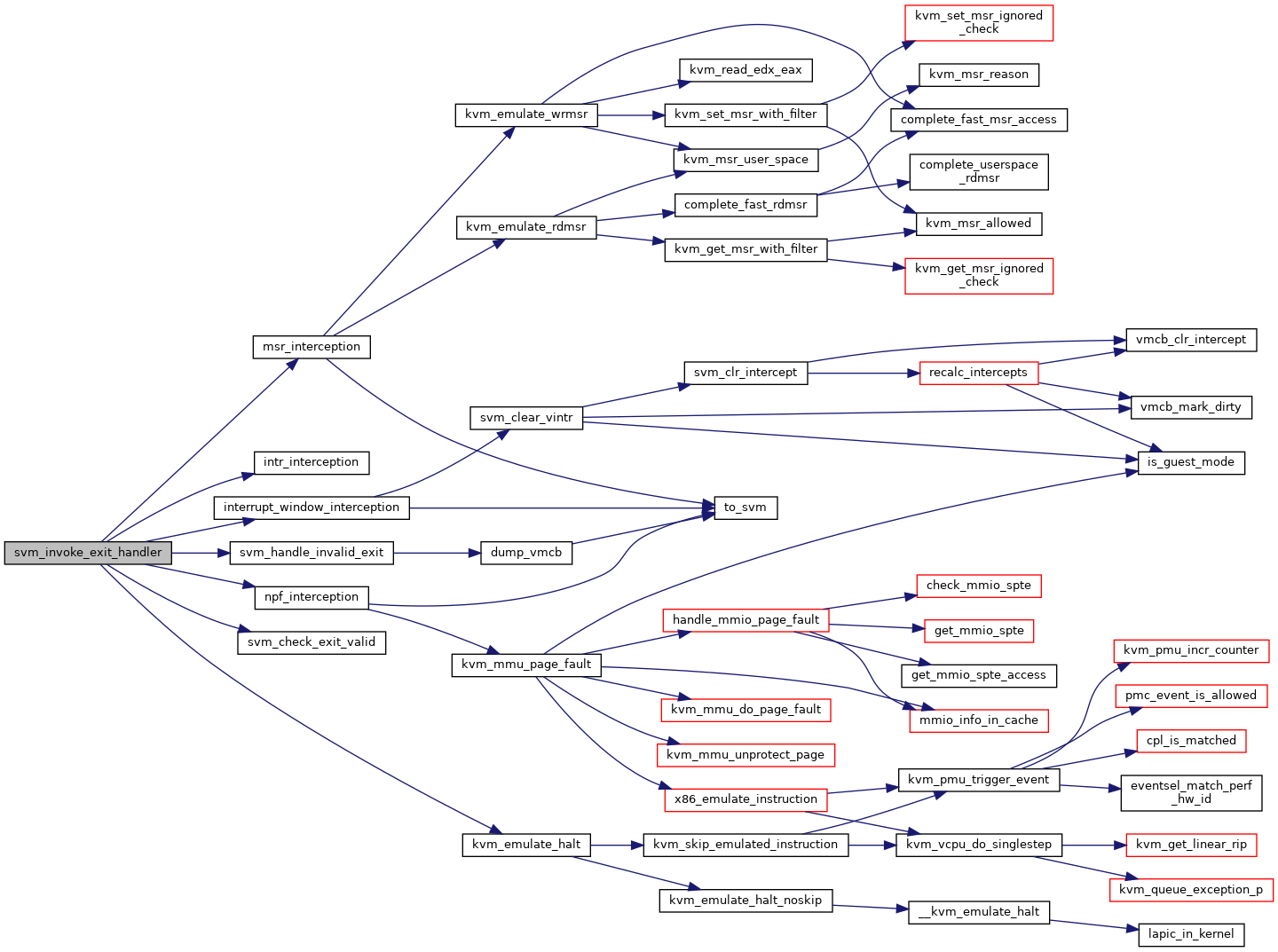

| int | svm_invoke_exit_handler (struct kvm_vcpu *vcpu, u64 exit_code) |

| static void | svm_get_exit_info (struct kvm_vcpu *vcpu, u32 *reason, u64 *info1, u64 *info2, u32 *intr_info, u32 *error_code) |

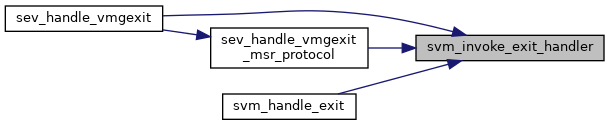

| static int | svm_handle_exit (struct kvm_vcpu *vcpu, fastpath_t exit_fastpath) |

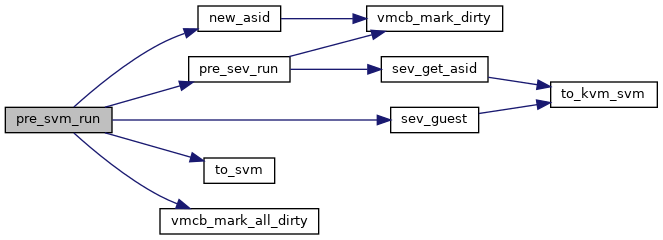

| static void | pre_svm_run (struct kvm_vcpu *vcpu) |

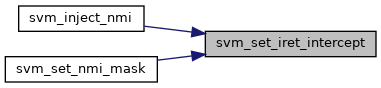

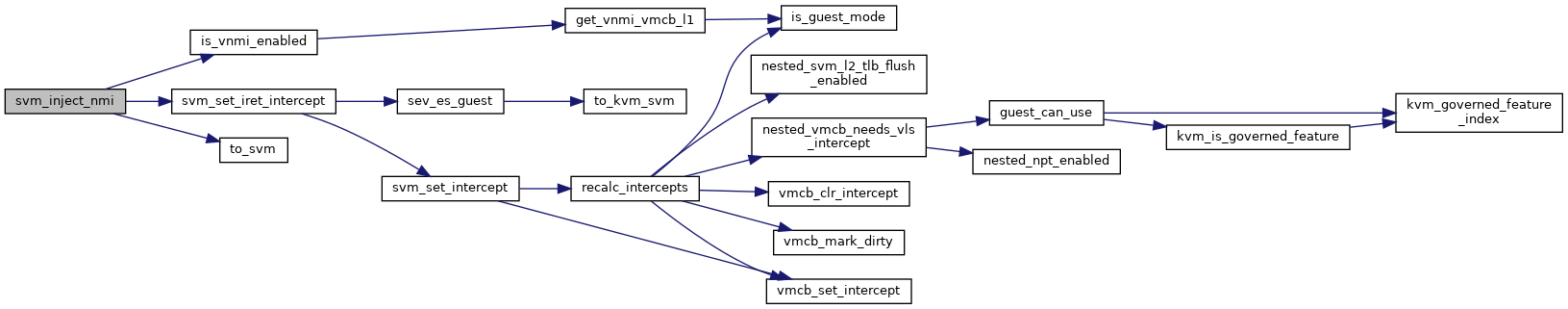

| static void | svm_inject_nmi (struct kvm_vcpu *vcpu) |

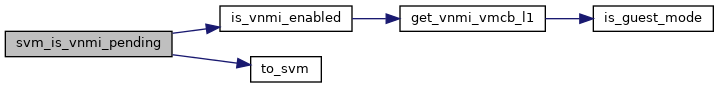

| static bool | svm_is_vnmi_pending (struct kvm_vcpu *vcpu) |

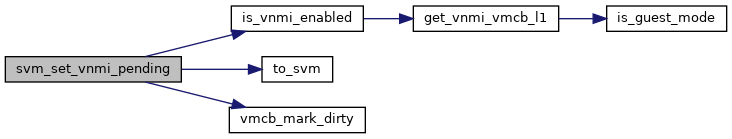

| static bool | svm_set_vnmi_pending (struct kvm_vcpu *vcpu) |

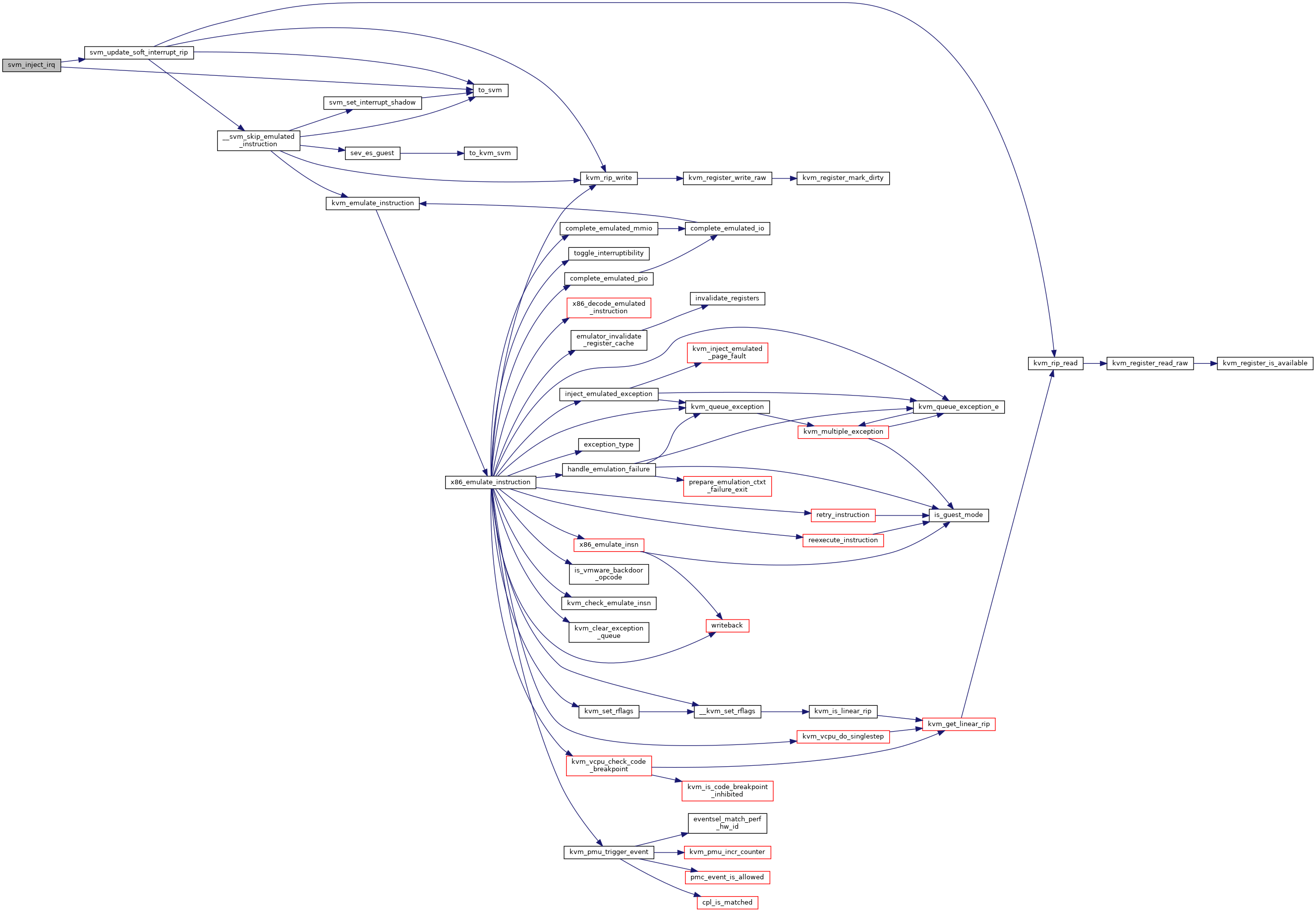

| static void | svm_inject_irq (struct kvm_vcpu *vcpu, bool reinjected) |

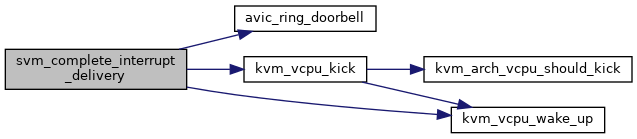

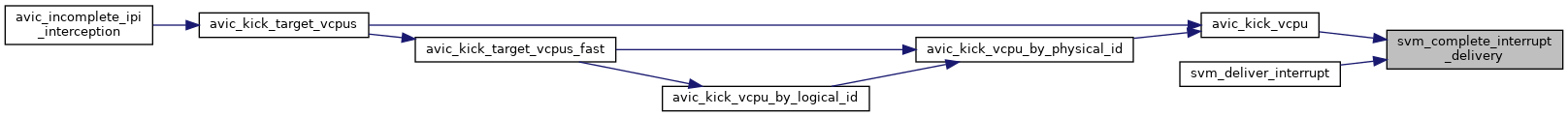

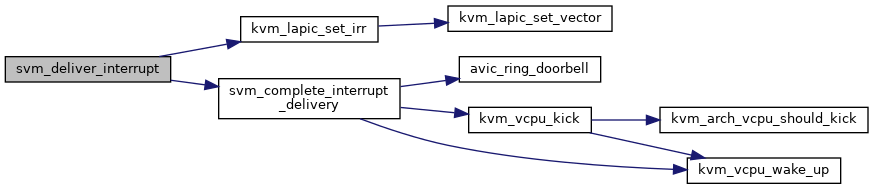

| void | svm_complete_interrupt_delivery (struct kvm_vcpu *vcpu, int delivery_mode, int trig_mode, int vector) |

| static void | svm_deliver_interrupt (struct kvm_lapic *apic, int delivery_mode, int trig_mode, int vector) |

| static void | svm_update_cr8_intercept (struct kvm_vcpu *vcpu, int tpr, int irr) |

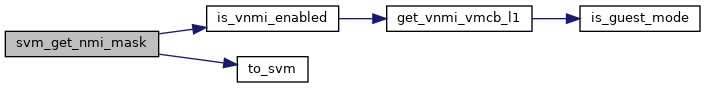

| static bool | svm_get_nmi_mask (struct kvm_vcpu *vcpu) |

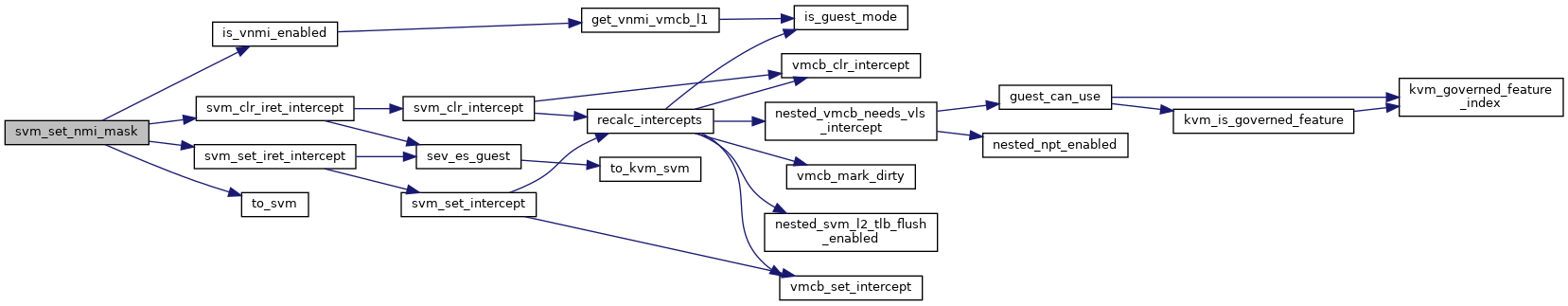

| static void | svm_set_nmi_mask (struct kvm_vcpu *vcpu, bool masked) |

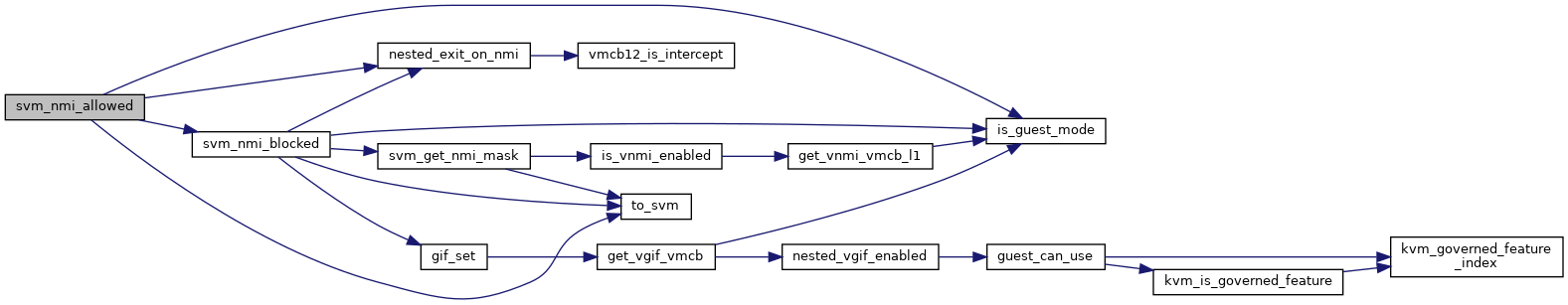

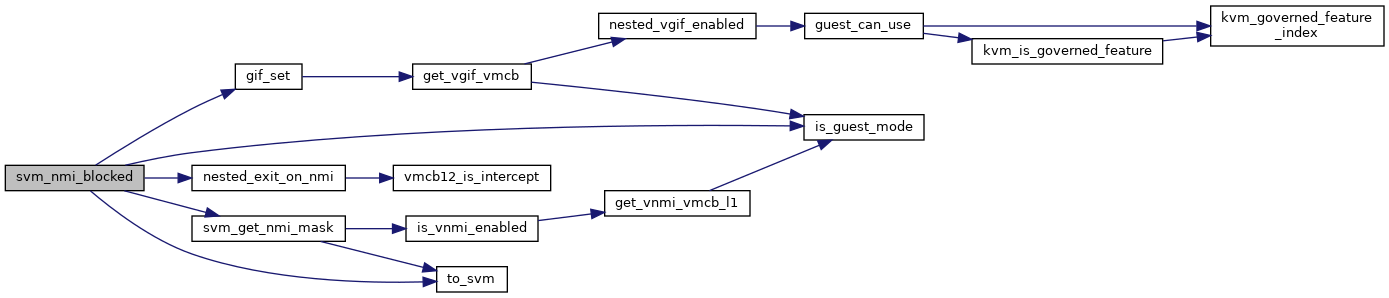

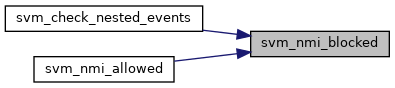

| bool | svm_nmi_blocked (struct kvm_vcpu *vcpu) |

| static int | svm_nmi_allowed (struct kvm_vcpu *vcpu, bool for_injection) |

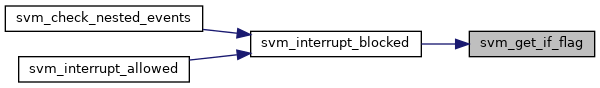

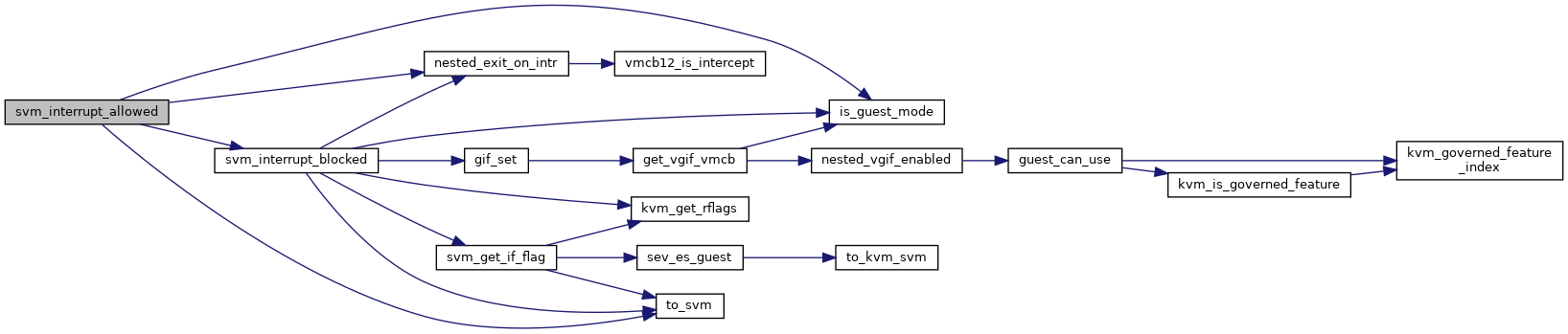

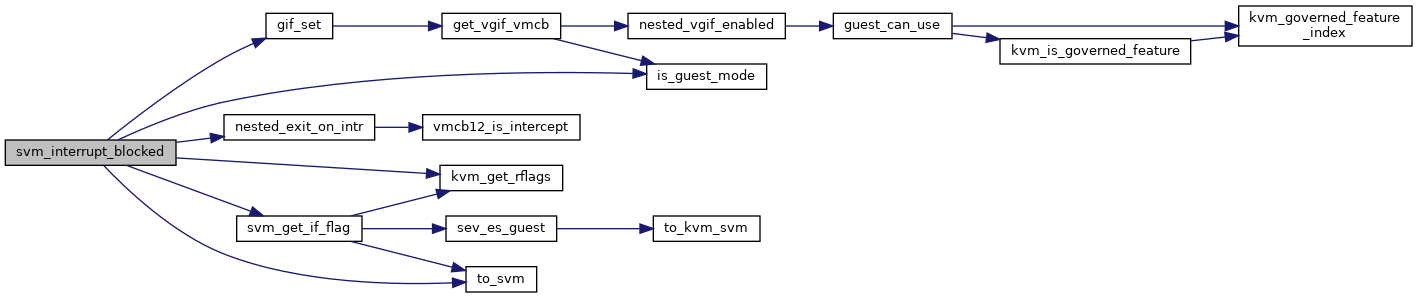

| bool | svm_interrupt_blocked (struct kvm_vcpu *vcpu) |

| static int | svm_interrupt_allowed (struct kvm_vcpu *vcpu, bool for_injection) |

| static void | svm_enable_irq_window (struct kvm_vcpu *vcpu) |

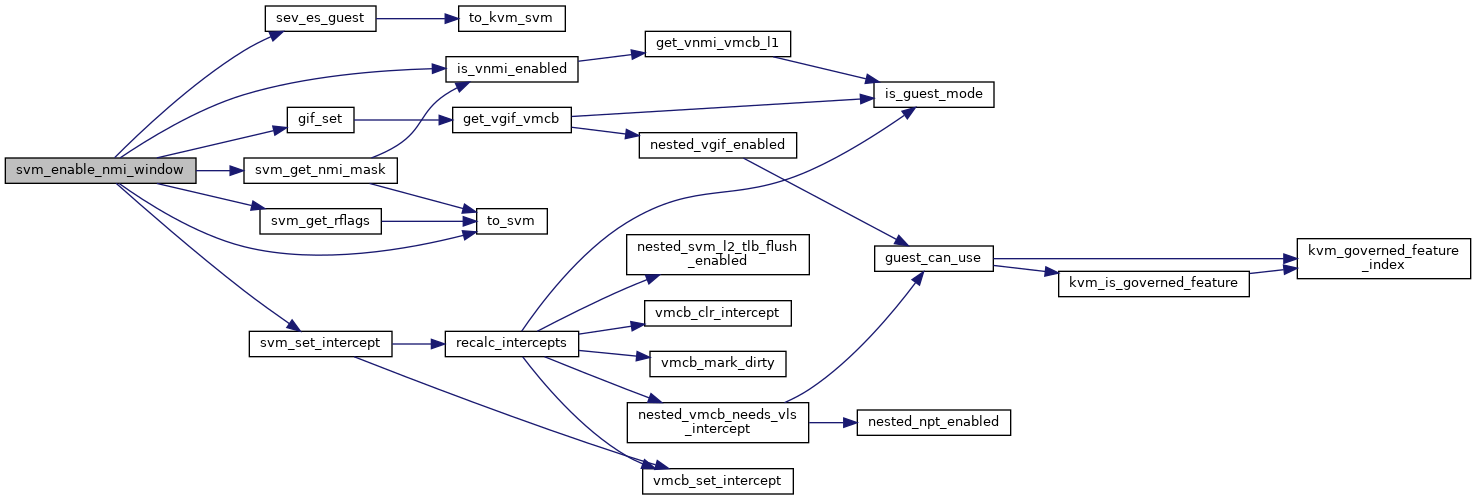

| static void | svm_enable_nmi_window (struct kvm_vcpu *vcpu) |

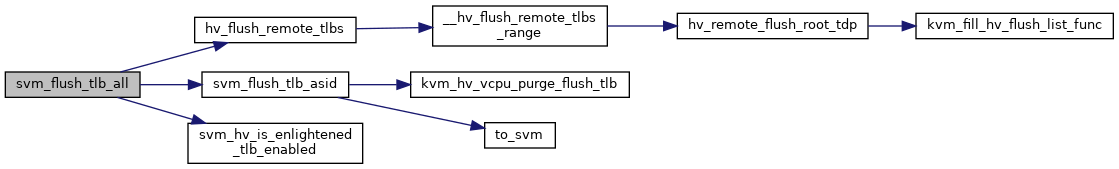

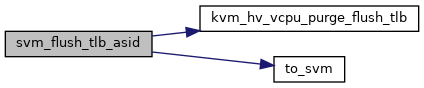

| static void | svm_flush_tlb_asid (struct kvm_vcpu *vcpu) |

| static void | svm_flush_tlb_all (struct kvm_vcpu *vcpu) |

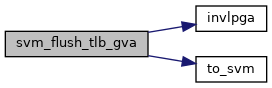

| static void | svm_flush_tlb_gva (struct kvm_vcpu *vcpu, gva_t gva) |

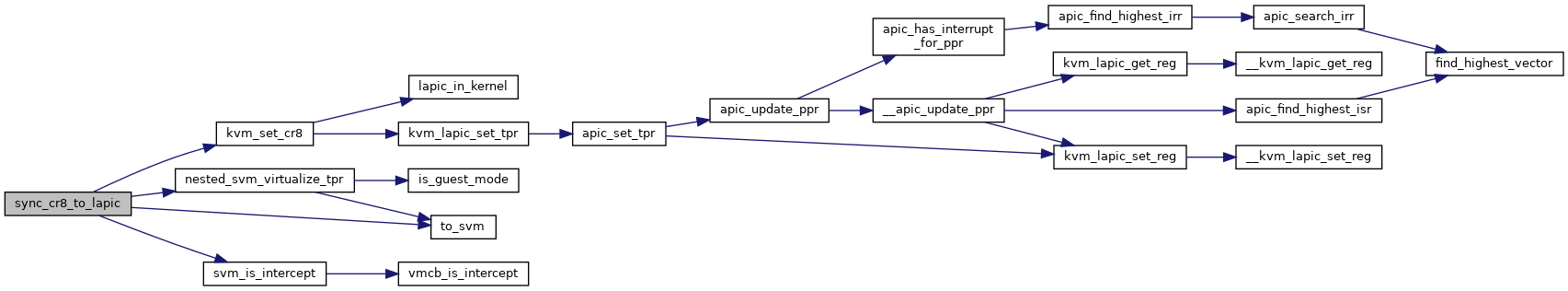

| static void | sync_cr8_to_lapic (struct kvm_vcpu *vcpu) |

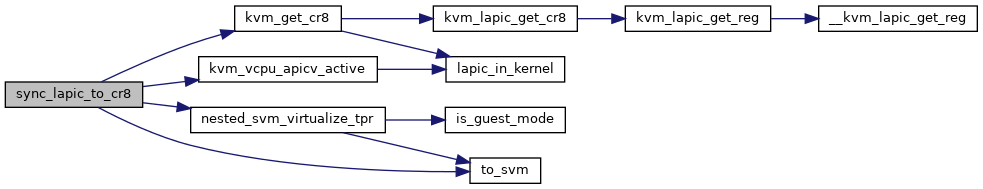

| static void | sync_lapic_to_cr8 (struct kvm_vcpu *vcpu) |

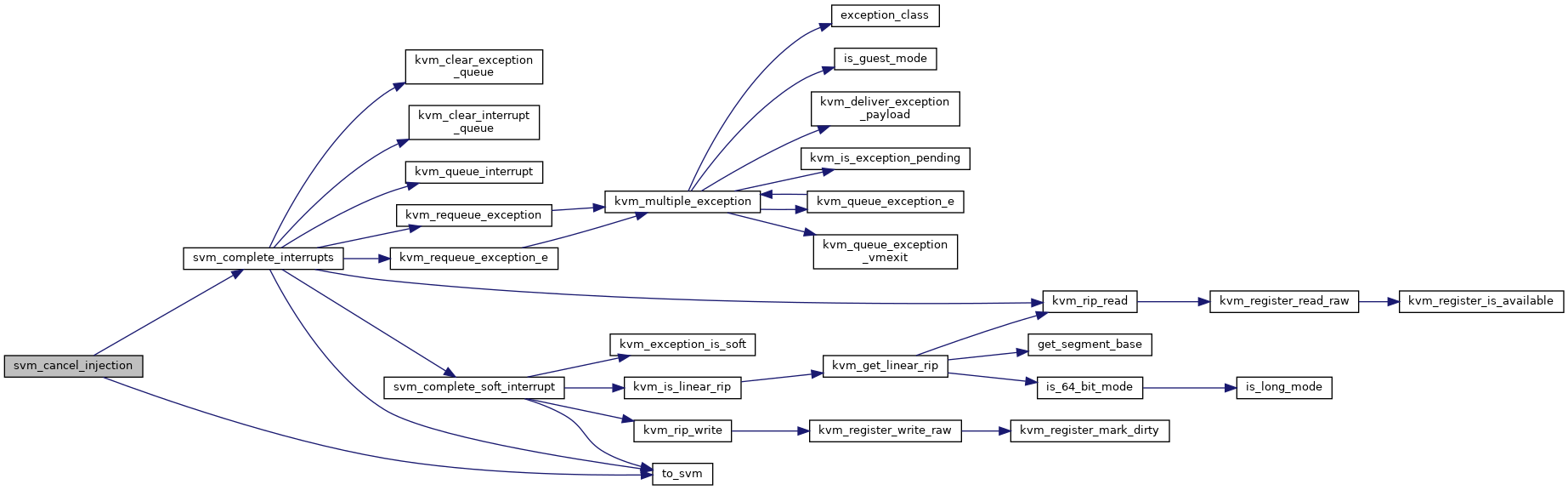

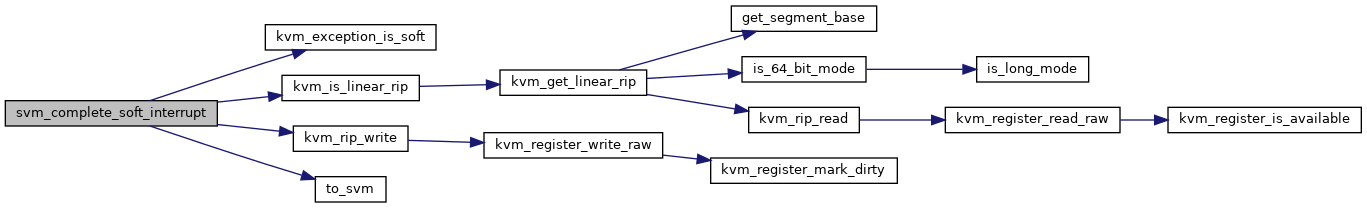

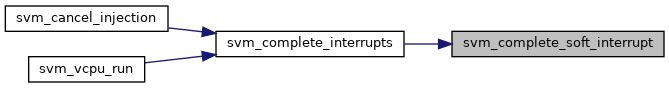

| static void | svm_complete_soft_interrupt (struct kvm_vcpu *vcpu, u8 vector, int type) |

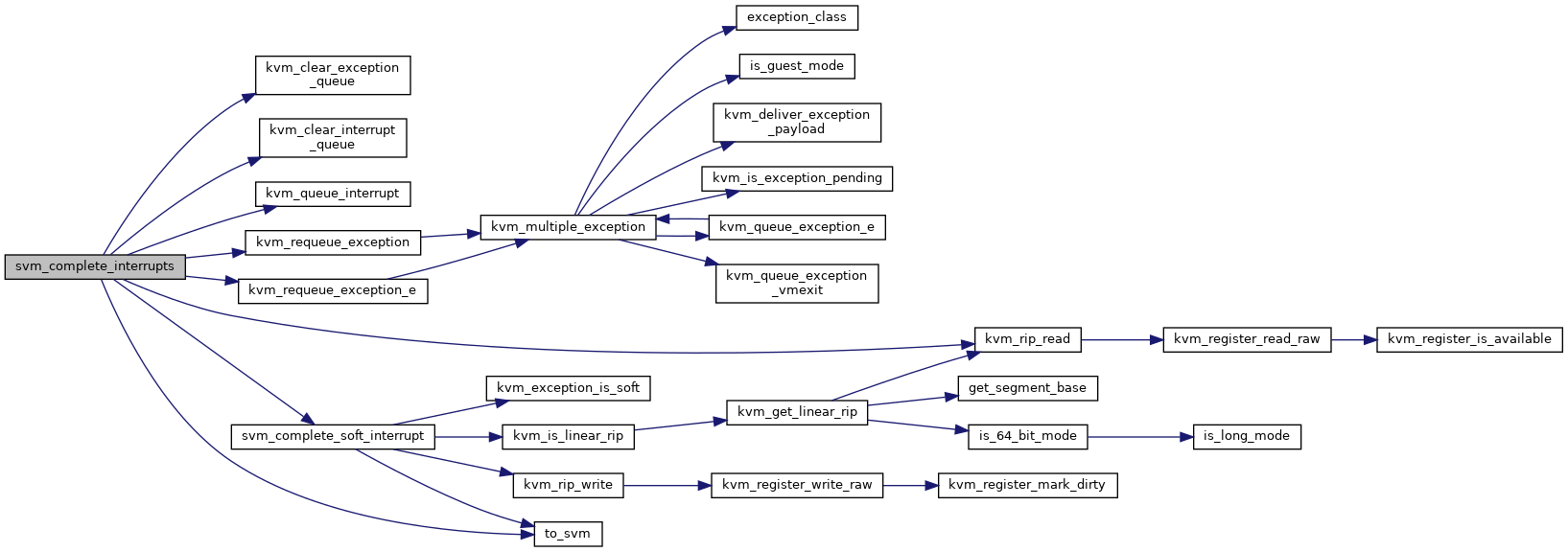

| static void | svm_complete_interrupts (struct kvm_vcpu *vcpu) |

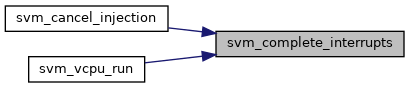

| static void | svm_cancel_injection (struct kvm_vcpu *vcpu) |

| static int | svm_vcpu_pre_run (struct kvm_vcpu *vcpu) |

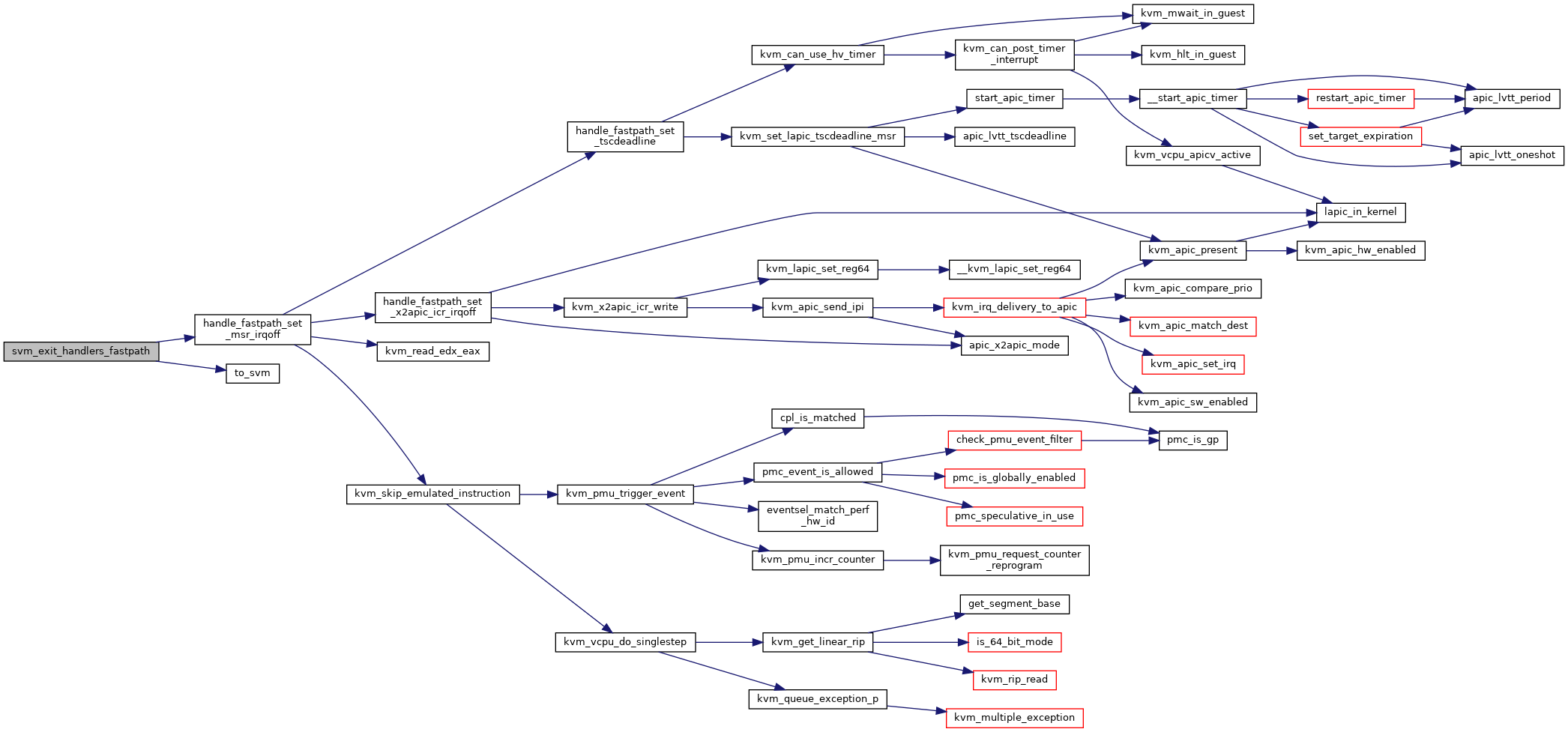

| static fastpath_t | svm_exit_handlers_fastpath (struct kvm_vcpu *vcpu) |

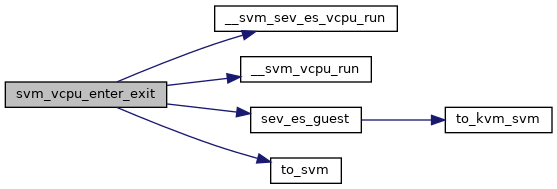

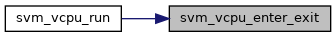

| static noinstr void | svm_vcpu_enter_exit (struct kvm_vcpu *vcpu, bool spec_ctrl_intercepted) |

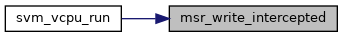

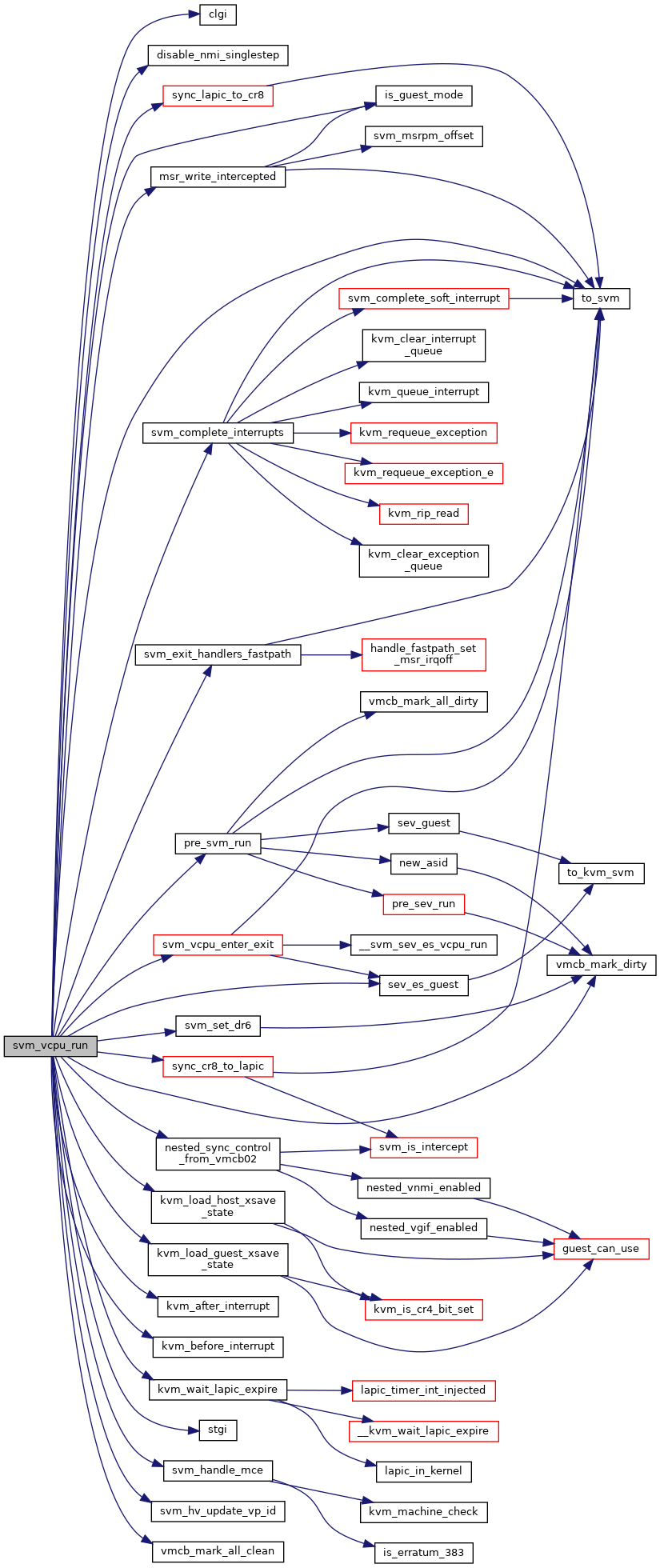

| static __no_kcsan fastpath_t | svm_vcpu_run (struct kvm_vcpu *vcpu) |

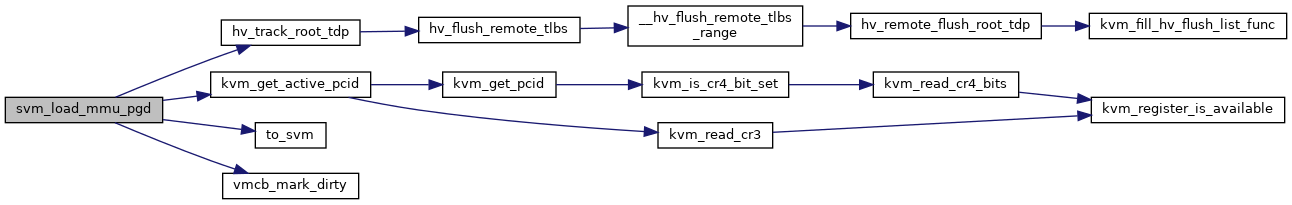

| static void | svm_load_mmu_pgd (struct kvm_vcpu *vcpu, hpa_t root_hpa, int root_level) |

| static void | svm_patch_hypercall (struct kvm_vcpu *vcpu, unsigned char *hypercall) |

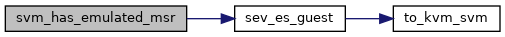

| static bool | svm_has_emulated_msr (struct kvm *kvm, u32 index) |

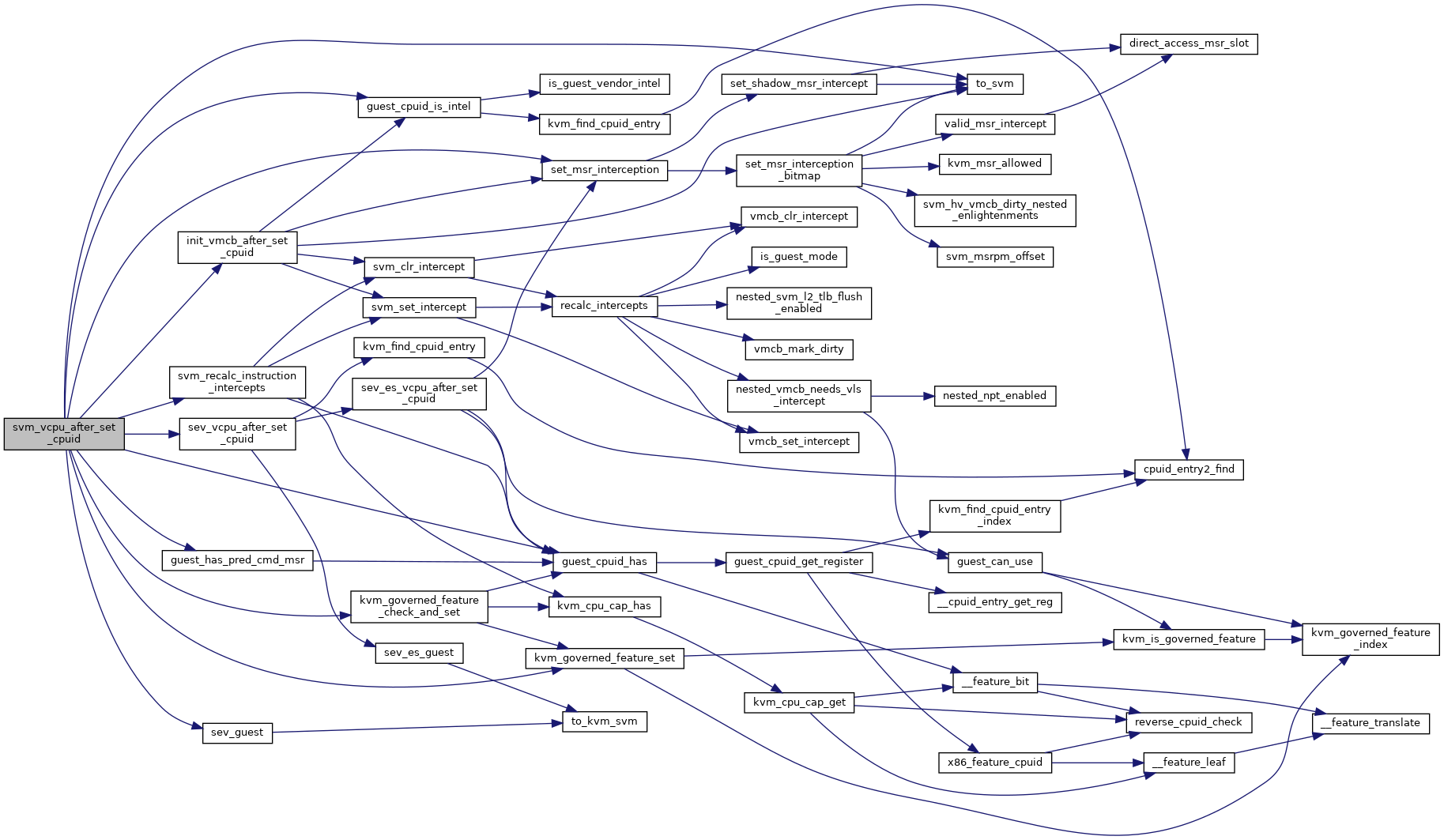

| static void | svm_vcpu_after_set_cpuid (struct kvm_vcpu *vcpu) |

| static bool | svm_has_wbinvd_exit (void) |

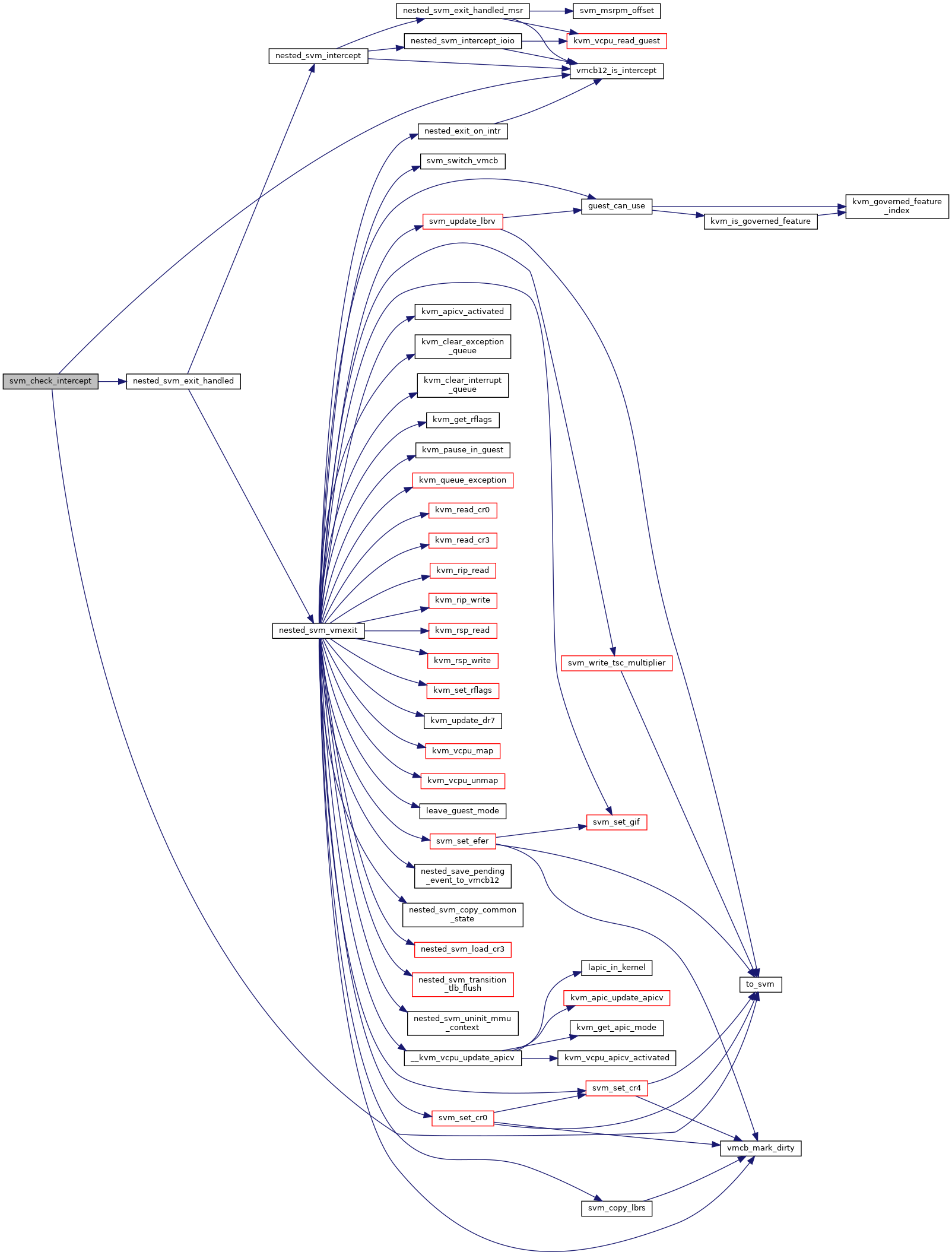

| static int | svm_check_intercept (struct kvm_vcpu *vcpu, struct x86_instruction_info *info, enum x86_intercept_stage stage, struct x86_exception *exception) |

| static void | svm_handle_exit_irqoff (struct kvm_vcpu *vcpu) |

| static void | svm_sched_in (struct kvm_vcpu *vcpu, int cpu) |

| static void | svm_setup_mce (struct kvm_vcpu *vcpu) |

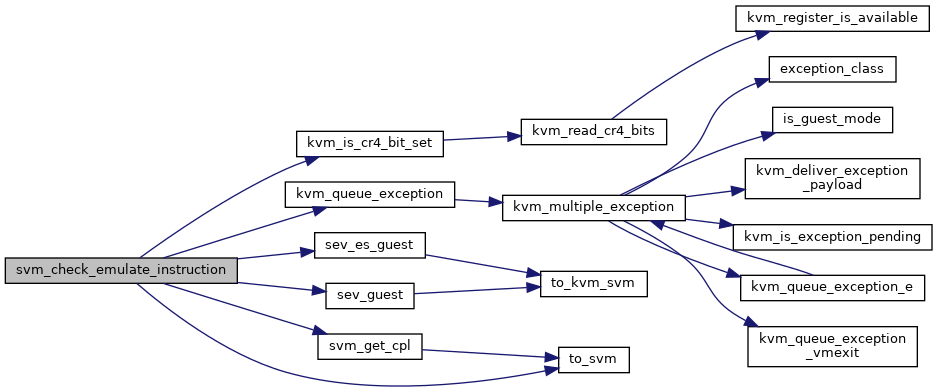

| static int | svm_check_emulate_instruction (struct kvm_vcpu *vcpu, int emul_type, void *insn, int insn_len) |

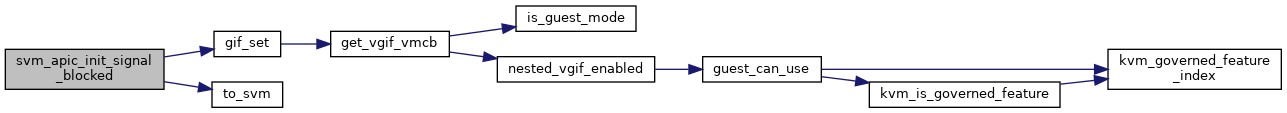

| static bool | svm_apic_init_signal_blocked (struct kvm_vcpu *vcpu) |

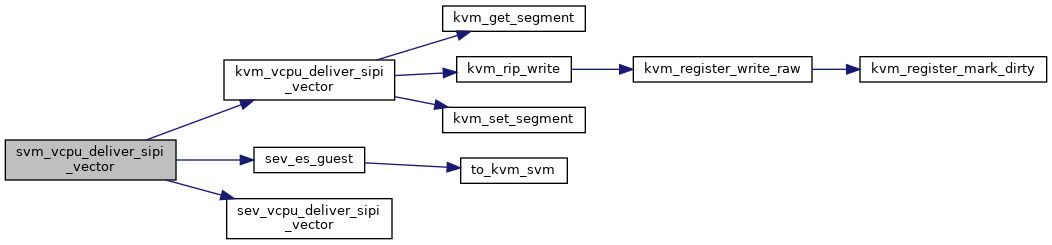

| static void | svm_vcpu_deliver_sipi_vector (struct kvm_vcpu *vcpu, u8 vector) |

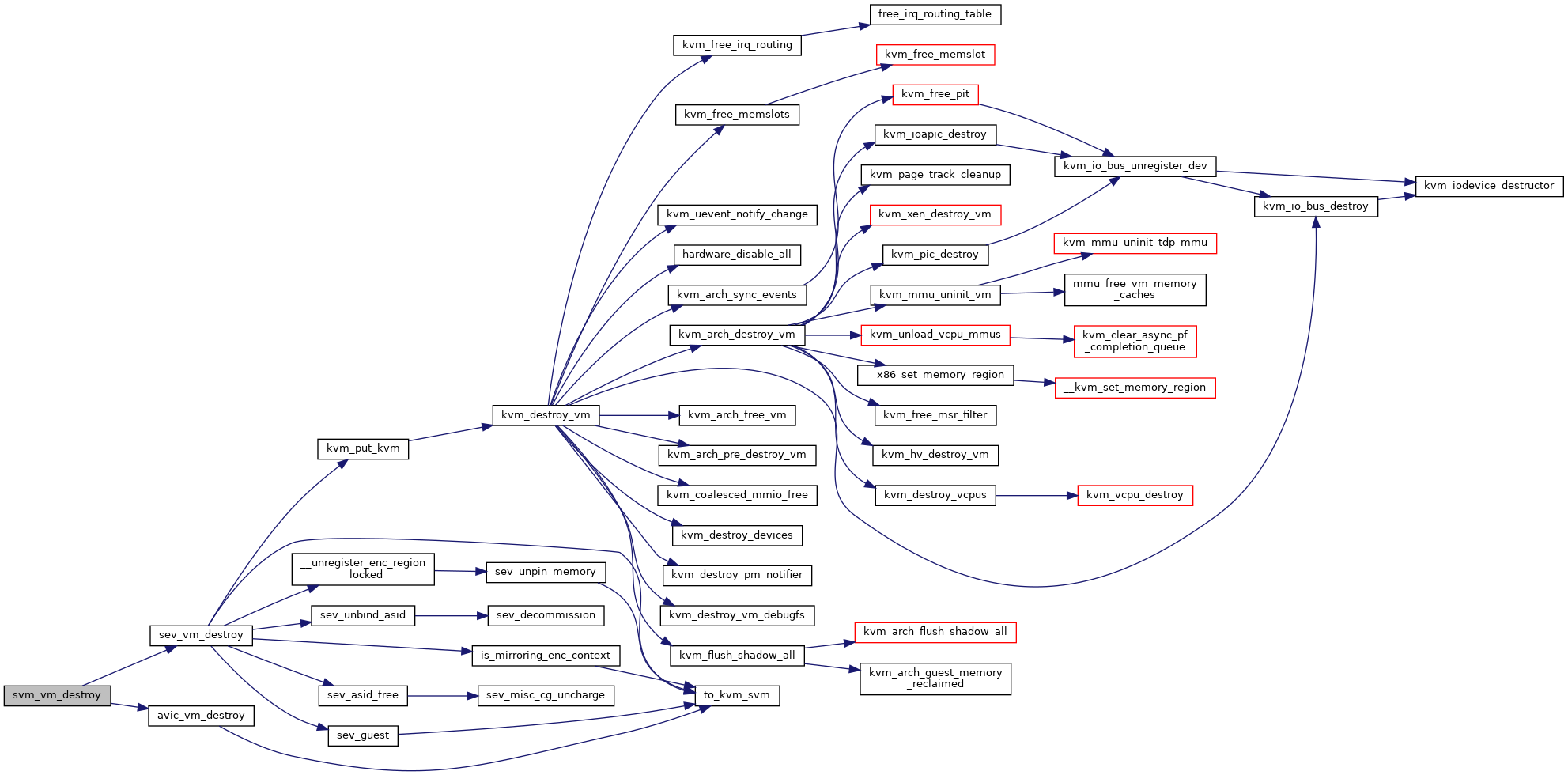

| static void | svm_vm_destroy (struct kvm *kvm) |

| static int | svm_vm_init (struct kvm *kvm) |

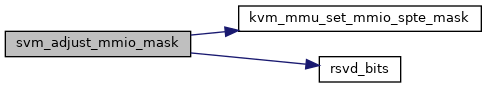

| static __init void | svm_adjust_mmio_mask (void) |

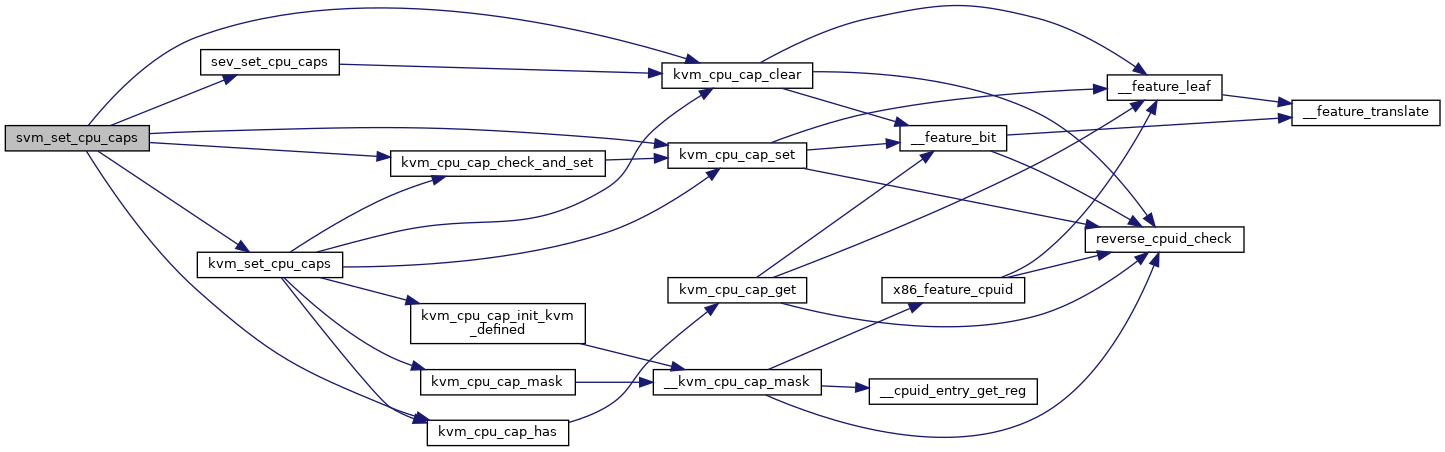

| static __init void | svm_set_cpu_caps (void) |

| static __init int | svm_hardware_setup (void) |

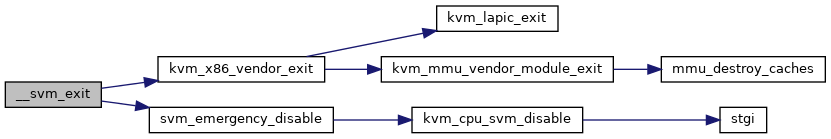

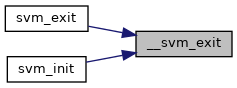

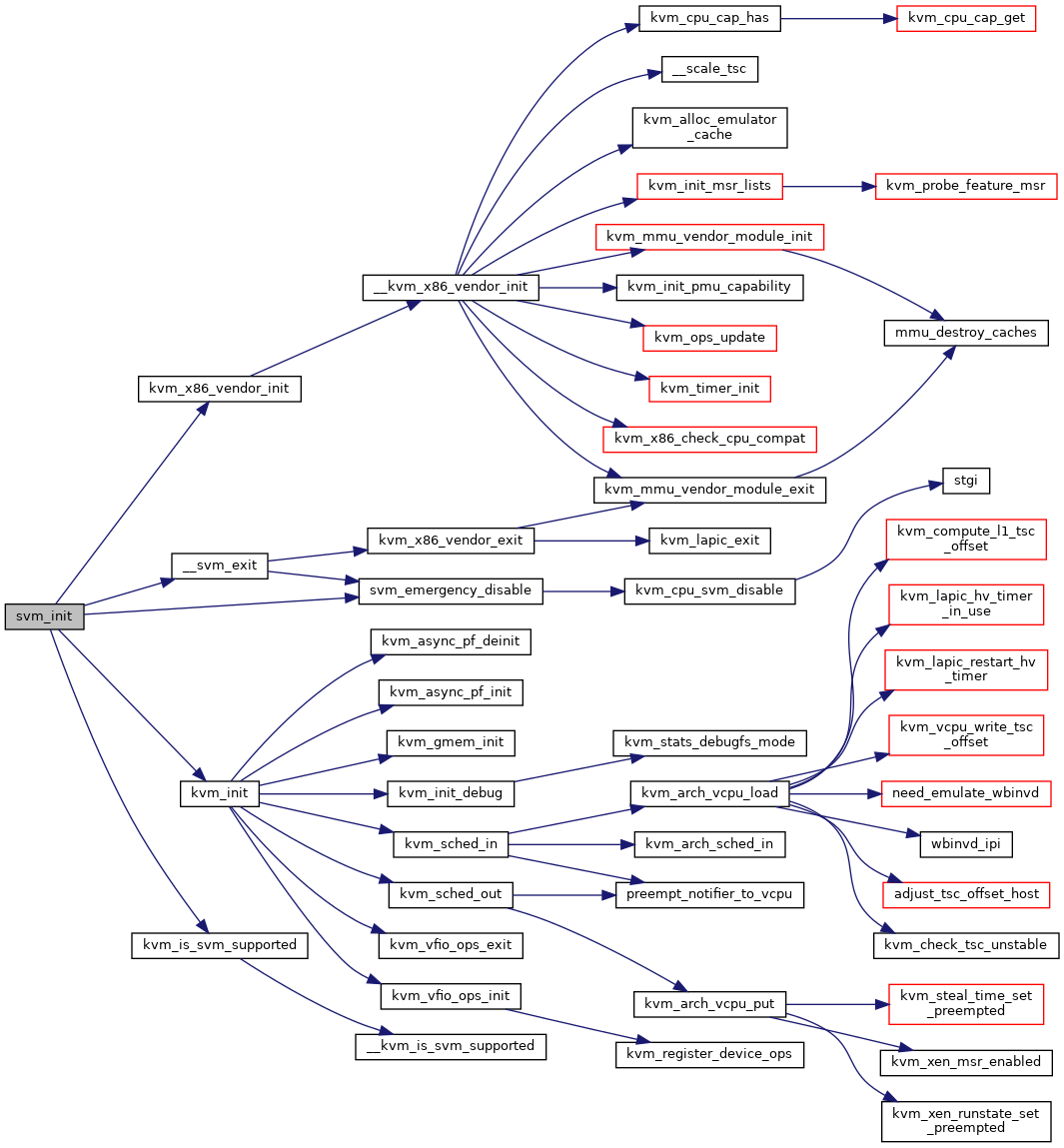

| static void | __svm_exit (void) |

| static int __init | svm_init (void) |

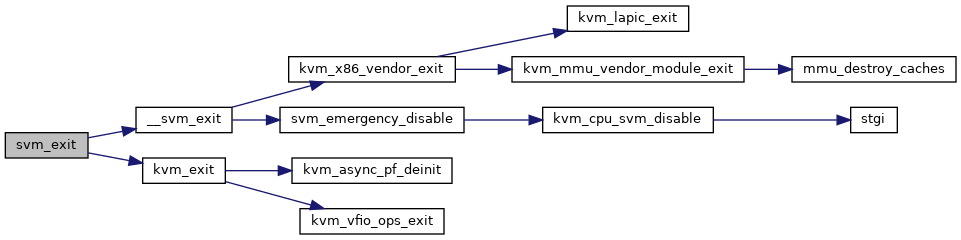

| static void __exit | svm_exit (void) |

Variables | |

| static bool erratum_383_found | __read_mostly = -1 |

| static uint64_t | osvw_len = 4 |

| static uint64_t | osvw_status |

| static const struct svm_direct_access_msrs | direct_access_msrs [MAX_DIRECT_ACCESS_MSRS] |

| static unsigned short | pause_filter_thresh = KVM_DEFAULT_PLE_GAP |

| static unsigned short | pause_filter_count = KVM_SVM_DEFAULT_PLE_WINDOW |

| static unsigned short | pause_filter_count_grow = KVM_DEFAULT_PLE_WINDOW_GROW |

| static unsigned short | pause_filter_count_shrink = KVM_DEFAULT_PLE_WINDOW_SHRINK |

| static unsigned short | pause_filter_count_max = KVM_SVM_DEFAULT_PLE_WINDOW_MAX |

| bool | npt_enabled = true |

| static int | nested = true |

| int | nrips = true |

| static int | vls = true |

| int | vgif = true |

| static int | lbrv = true |

| static int | tsc_scaling = true |

| static bool | avic |

| bool __read_mostly | dump_invalid_vmcb |

| bool | intercept_smi = true |

| bool | vnmi = true |

| static bool | svm_gp_erratum_intercept = true |

| static u8 | rsm_ins_bytes [] = "\x0f\xaa" |

| static unsigned long | iopm_base |

| static const u32 | msrpm_ranges [] = {0, 0xc0000000, 0xc0010000} |

| static int(*const | svm_exit_handlers [])(struct kvm_vcpu *vcpu) |

| static const struct __x86_intercept | x86_intercept_map [] |

| static struct kvm_x86_ops svm_x86_ops | __initdata |

Macro Definition Documentation

◆ CR_VALID

◆ MSRS_IN_RANGE

| #define MSRS_IN_RANGE (MSRS_RANGE_SIZE * 8 / 2) |

◆ MSRS_RANGE_SIZE

◆ NUM_MSR_MAPS

| #define NUM_MSR_MAPS ARRAY_SIZE(msrpm_ranges) |

◆ POST_EX

| #define POST_EX | ( | exit | ) |

◆ POST_MEM

| #define POST_MEM | ( | exit | ) |

◆ pr_fmt

◆ PRE_EX

| #define PRE_EX | ( | exit | ) |

◆ SEG_TYPE_BUSY_TSS16

◆ SEG_TYPE_LDT

◆ X2APIC_MSR

Enumeration Type Documentation

◆ anonymous enum

| anonymous enum |

Function Documentation

◆ __kvm_is_svm_supported()

|

static |

◆ __svm_exit()

|

static |

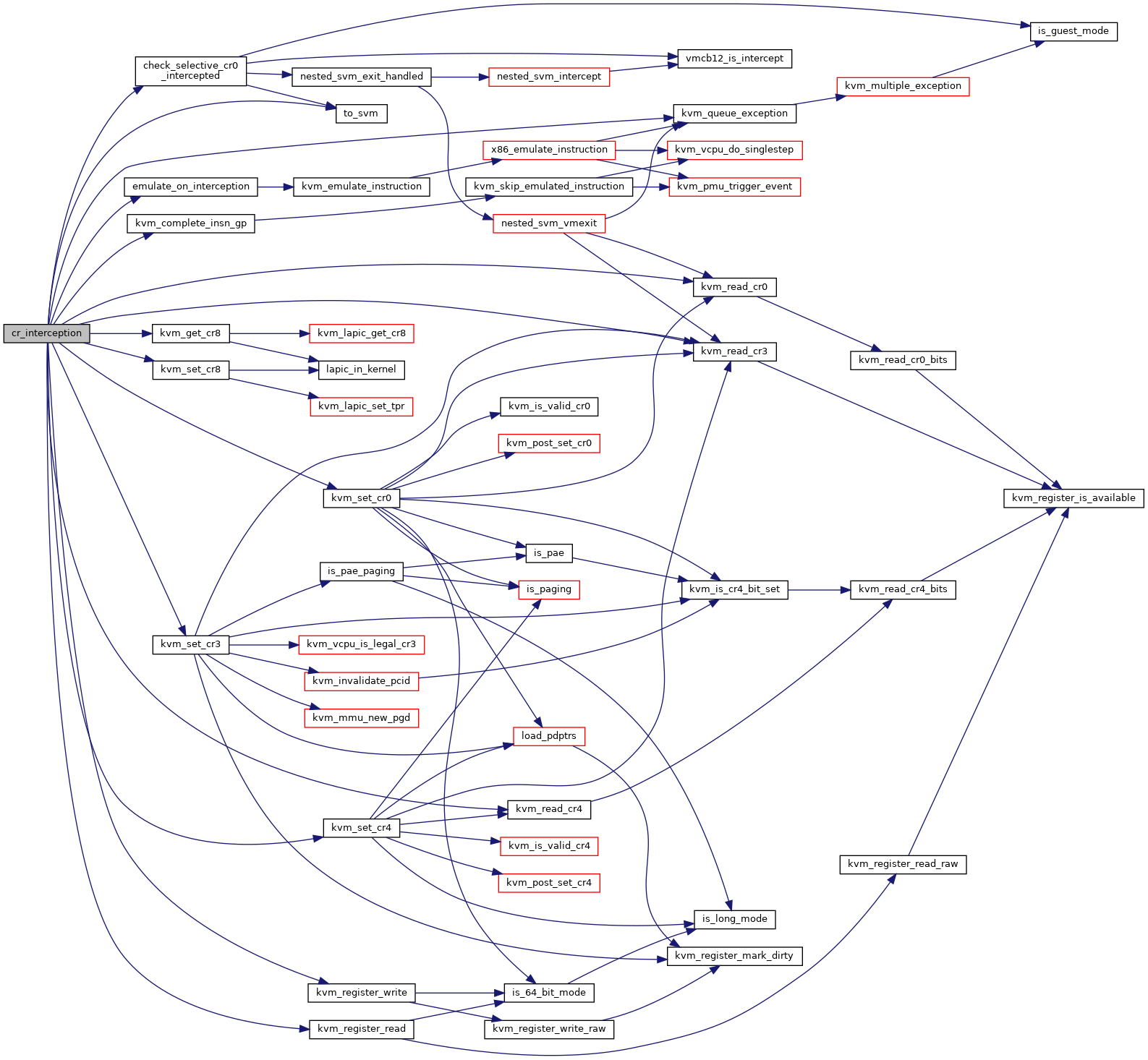

◆ __svm_skip_emulated_instruction()

|

static |

Definition at line 369 of file svm.c.

◆ __svm_vcpu_reset()

|

static |

◆ __svm_write_tsc_multiplier()

|

static |

◆ ac_interception()

|

static |

◆ add_msr_offset()

|

static |

◆ bp_interception()

|

static |

◆ check_selective_cr0_intercepted()

|

static |

◆ clgi_interception()

|

static |

Definition at line 2451 of file svm.c.

◆ clr_dr_intercepts()

|

static |

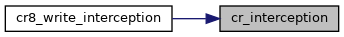

◆ cr8_write_interception()

|

static |

◆ cr_interception()

|

static |

Definition at line 2625 of file svm.c.

◆ cr_trap()

|

static |

Definition at line 2699 of file svm.c.

◆ db_interception()

|

static |

◆ DEFINE_PER_CPU() [1/2]

| DEFINE_PER_CPU | ( | struct svm_cpu_data | , |

| svm_data | |||

| ) |

◆ DEFINE_PER_CPU() [2/2]

|

static |

◆ direct_access_msr_slot()

|

static |

◆ disable_nmi_singlestep()

| void disable_nmi_singlestep | ( | struct vcpu_svm * | svm | ) |

◆ dr_interception()

|

static |

◆ dump_vmcb()

|

static |

◆ efer_trap()

|

static |

Definition at line 2791 of file svm.c.

◆ emulate_on_interception()

|

static |

◆ emulate_svm_instr()

|

static |

Definition at line 2333 of file svm.c.

◆ get_npt_level()

|

static |

◆ gp_interception()

|

static |

Definition at line 2366 of file svm.c.

◆ grow_ple_window()

|

static |

◆ init_msrpm_offsets()

|

static |

◆ init_seg()

|

static |

◆ init_sys_seg()

|

static |

◆ init_vmcb()

|

static |

Definition at line 1227 of file svm.c.

◆ init_vmcb_after_set_cpuid()

|

inlinestatic |

◆ interrupt_window_interception()

|

static |

◆ intr_interception()

|

static |

◆ invlpg_interception()

|

static |

◆ invlpga_interception()

|

static |

◆ invpcid_interception()

|

static |

Definition at line 3216 of file svm.c.

◆ io_interception()

|

static |

Definition at line 2211 of file svm.c.

◆ iret_interception()

|

static |

Definition at line 2566 of file svm.c.

◆ is_erratum_383()

|

static |

◆ kvm_cpu_svm_disable()

|

inlinestatic |

◆ kvm_is_svm_supported()

|

static |

◆ mc_interception()

|

static |

◆ MODULE_AUTHOR()

| MODULE_AUTHOR | ( | "Qumranet" | ) |

◆ MODULE_LICENSE()

| MODULE_LICENSE | ( | "GPL" | ) |

◆ module_param() [1/15]

| module_param | ( | avic | , |

| bool | , | ||

| 0444 | |||

| ) |

◆ module_param() [2/15]

| module_param | ( | dump_invalid_vmcb | , |

| bool | , | ||

| 0644 | |||

| ) |

◆ module_param() [3/15]

| module_param | ( | intercept_smi | , |

| bool | , | ||

| 0444 | |||

| ) |

◆ module_param() [4/15]

| module_param | ( | lbrv | , |

| int | , | ||

| 0444 | |||

| ) |

◆ module_param() [5/15]

| module_param | ( | nested | , |

| int | , | ||

| 0444 | |||

| ) |

◆ module_param() [6/15]

| module_param | ( | nrips | , |

| int | , | ||

| 0444 | |||

| ) |

◆ module_param() [7/15]

| module_param | ( | pause_filter_count | , |

| ushort | , | ||

| 0444 | |||

| ) |

◆ module_param() [8/15]

| module_param | ( | pause_filter_count_grow | , |

| ushort | , | ||

| 0444 | |||

| ) |

◆ module_param() [9/15]

| module_param | ( | pause_filter_count_max | , |

| ushort | , | ||

| 0444 | |||

| ) |

◆ module_param() [10/15]

| module_param | ( | pause_filter_count_shrink | , |

| ushort | , | ||

| 0444 | |||

| ) |

◆ module_param() [11/15]

| module_param | ( | pause_filter_thresh | , |

| ushort | , | ||

| 0444 | |||

| ) |

◆ module_param() [12/15]

| module_param | ( | tsc_scaling | , |

| int | , | ||

| 0444 | |||

| ) |

◆ module_param() [13/15]

| module_param | ( | vgif | , |

| int | , | ||

| 0444 | |||

| ) |

◆ module_param() [14/15]

| module_param | ( | vls | , |

| int | , | ||

| 0444 | |||

| ) |

◆ module_param() [15/15]

| module_param | ( | vnmi | , |

| bool | , | ||

| 0444 | |||

| ) |

◆ module_param_named()

| module_param_named | ( | npt | , |

| npt_enabled | , | ||

| bool | , | ||

| 0444 | |||

| ) |

◆ msr_interception()

|

static |

◆ msr_write_intercepted()

|

static |

◆ new_asid()

|

static |

◆ nmi_interception()

|

static |

◆ npf_interception()

|

static |

Definition at line 2051 of file svm.c.

◆ pause_interception()

|

static |

Definition at line 3200 of file svm.c.

◆ pf_interception()

|

static |

Definition at line 2038 of file svm.c.

◆ pre_svm_run()

|

static |

◆ rsm_interception()

|

static |

Definition at line 2596 of file svm.c.

◆ set_dr_intercepts()

|

static |

◆ set_msr_interception()

| void set_msr_interception | ( | struct kvm_vcpu * | vcpu, |

| u32 * | msrpm, | ||

| u32 | msr, | ||

| int | read, | ||

| int | write | ||

| ) |

Definition at line 859 of file svm.c.

◆ set_msr_interception_bitmap()

|

static |

Definition at line 822 of file svm.c.

◆ set_shadow_msr_intercept()

|

static |

◆ sev_post_set_cr3()

|

static |

◆ shrink_ple_window()

|

static |

◆ shutdown_interception()

|

static |

◆ skinit_interception()

|

static |

◆ smi_interception()

|

static |

◆ stgi_interception()

|

static |

◆ svm_adjust_mmio_mask()

|

static |

Definition at line 5042 of file svm.c.

◆ svm_apic_init_signal_blocked()

|

static |

◆ svm_cache_reg()

|

static |

Definition at line 1612 of file svm.c.

◆ svm_cancel_injection()

|

static |

Definition at line 4077 of file svm.c.

◆ svm_check_emulate_instruction()

|

static |

Definition at line 4721 of file svm.c.

◆ svm_check_exit_valid()

|

static |

Definition at line 3435 of file svm.c.

◆ svm_check_intercept()

|

static |

Definition at line 4427 of file svm.c.

◆ svm_check_processor_compat()

|

static |

◆ svm_clear_current_vmcb()

|

static |

◆ svm_clear_vintr()

|

static |

◆ svm_clr_iret_intercept()

|

static |

◆ svm_complete_emulated_msr()

|

static |

◆ svm_complete_interrupt_delivery()

| void svm_complete_interrupt_delivery | ( | struct kvm_vcpu * | vcpu, |

| int | delivery_mode, | ||

| int | trig_mode, | ||

| int | vector | ||

| ) |

◆ svm_complete_interrupts()

|

static |

Definition at line 4008 of file svm.c.

◆ svm_complete_soft_interrupt()

|

static |

Definition at line 3976 of file svm.c.

◆ svm_copy_lbrs()

| void svm_copy_lbrs | ( | struct vmcb * | to_vmcb, |

| struct vmcb * | from_vmcb | ||

| ) |

◆ svm_cpu_init()

|

static |

◆ svm_cpu_uninit()

|

static |

◆ svm_deliver_interrupt()

|

static |

Definition at line 3667 of file svm.c.

◆ svm_disable_lbrv()

|

static |

◆ svm_emergency_disable()

|

static |

◆ svm_enable_irq_window()

|

static |

◆ svm_enable_lbrv()

|

static |

◆ svm_enable_nmi_window()

|

static |

◆ svm_exit()

|

static |

◆ svm_exit_handlers_fastpath()

|

static |

Definition at line 4093 of file svm.c.

◆ svm_flush_tlb_all()

|

static |

Definition at line 3927 of file svm.c.

◆ svm_flush_tlb_asid()

|

static |

Definition at line 3887 of file svm.c.

◆ svm_flush_tlb_current()

|

static |

◆ svm_flush_tlb_gva()

|

static |

◆ svm_get_cpl()

|

static |

◆ svm_get_cs_db_l_bits()

|

static |

Definition at line 1786 of file svm.c.

◆ svm_get_exit_info()

|

static |

◆ svm_get_gdt()

|

static |

◆ svm_get_idt()

|

static |

◆ svm_get_if_flag()

|

static |

◆ svm_get_interrupt_shadow()

|

static |

◆ svm_get_l2_tsc_multiplier()

|

static |

◆ svm_get_l2_tsc_offset()

|

static |

◆ svm_get_lbr_vmcb()

|

static |

◆ svm_get_msr()

|

static |

Definition at line 2826 of file svm.c.

◆ svm_get_msr_feature()

|

static |

◆ svm_get_nmi_mask()

|

static |

◆ svm_get_rflags()

|

static |

◆ svm_get_segment()

|

static |

◆ svm_get_segment_base()

|

static |

◆ svm_handle_exit()

|

static |

Definition at line 3490 of file svm.c.

◆ svm_handle_exit_irqoff()

|

static |

◆ svm_handle_invalid_exit()

|

static |

◆ svm_handle_mce()

|

static |

◆ svm_hardware_disable()

|

static |

◆ svm_hardware_enable()

|

static |

◆ svm_hardware_setup()

|

static |

Definition at line 5152 of file svm.c.

◆ svm_hardware_unsetup()

|

static |

◆ svm_has_emulated_msr()

|

static |

◆ svm_has_wbinvd_exit()

|

static |

◆ svm_init()

|

static |

Definition at line 5342 of file svm.c.

◆ svm_init_erratum_383()

|

static |

◆ svm_init_osvw()

|

static |

◆ svm_inject_exception()

|

static |

◆ svm_inject_irq()

|

static |

◆ svm_inject_nmi()

|

static |

Definition at line 3557 of file svm.c.

◆ svm_instr_opcode()

|

static |

Definition at line 2312 of file svm.c.

◆ svm_interrupt_allowed()

|

static |

◆ svm_interrupt_blocked()

| bool svm_interrupt_blocked | ( | struct kvm_vcpu * | vcpu | ) |

◆ svm_invoke_exit_handler()

| int svm_invoke_exit_handler | ( | struct kvm_vcpu * | vcpu, |

| u64 | exit_code | ||

| ) |

Definition at line 3453 of file svm.c.

◆ svm_is_valid_cr0()

|

static |

◆ svm_is_valid_cr4()

|

static |

◆ svm_is_vnmi_pending()

|

static |

◆ svm_load_mmu_pgd()

|

static |

Definition at line 4246 of file svm.c.

◆ svm_msr_filter_changed()

|

static |

◆ svm_msrpm_offset()

| u32 svm_msrpm_offset | ( | u32 | msr | ) |

◆ svm_nmi_allowed()

|

static |

◆ svm_nmi_blocked()

| bool svm_nmi_blocked | ( | struct kvm_vcpu * | vcpu | ) |

◆ svm_patch_hypercall()

|

static |

◆ svm_prepare_host_switch()

|

static |

◆ svm_prepare_switch_to_guest()

|

static |

Definition at line 1506 of file svm.c.

◆ svm_recalc_instruction_intercepts()

|

static |

Definition at line 1172 of file svm.c.

◆ svm_sched_in()

|

static |

◆ svm_seg()

|

static |

◆ svm_set_cpu_caps()

|

static |

Definition at line 5077 of file svm.c.

◆ svm_set_cr0()

| void svm_set_cr0 | ( | struct kvm_vcpu * | vcpu, |

| unsigned long | cr0 | ||

| ) |

◆ svm_set_cr4()

| void svm_set_cr4 | ( | struct kvm_vcpu * | vcpu, |

| unsigned long | cr4 | ||

| ) |

◆ svm_set_dr6()

|

static |

◆ svm_set_dr7()

|

static |

◆ svm_set_efer()

| int svm_set_efer | ( | struct kvm_vcpu * | vcpu, |

| u64 | efer | ||

| ) |

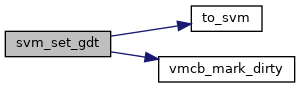

◆ svm_set_gdt()

|

static |

◆ svm_set_gif()

| void svm_set_gif | ( | struct vcpu_svm * | svm, |

| bool | value | ||

| ) |

Definition at line 2406 of file svm.c.

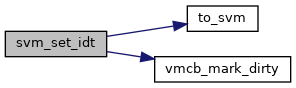

◆ svm_set_idt()

|

static |

◆ svm_set_interrupt_shadow()

|

static |

◆ svm_set_iret_intercept()

|

static |

◆ svm_set_msr()

|

static |

Definition at line 2973 of file svm.c.

◆ svm_set_nmi_mask()

|

static |

◆ svm_set_rflags()

|

static |

◆ svm_set_segment()

|

static |

◆ svm_set_vintr()

|

static |

◆ svm_set_vm_cr()

|

static |

◆ svm_set_vnmi_pending()

|

static |

◆ svm_set_x2apic_msr_interception()

| void svm_set_x2apic_msr_interception | ( | struct vcpu_svm * | svm, |

| bool | intercept | ||

| ) |

◆ svm_setup_mce()

|

static |

◆ svm_skip_emulated_instruction()

|

static |

◆ svm_switch_vmcb()

| void svm_switch_vmcb | ( | struct vcpu_svm * | svm, |

| struct kvm_vmcb_info * | target_vmcb | ||

| ) |

◆ svm_sync_dirty_debug_regs()

|

static |

◆ svm_update_cr8_intercept()

|

static |

◆ svm_update_exception_bitmap()

|

static |

◆ svm_update_lbrv()

| void svm_update_lbrv | ( | struct kvm_vcpu * | vcpu | ) |

◆ svm_update_soft_interrupt_rip()

|

static |

◆ svm_vcpu_after_set_cpuid()

|

static |

Definition at line 4306 of file svm.c.

◆ svm_vcpu_alloc_msrpm()

| u32* svm_vcpu_alloc_msrpm | ( | void | ) |

◆ svm_vcpu_create()

|

static |

Definition at line 1413 of file svm.c.

◆ svm_vcpu_deliver_sipi_vector()

|

static |

Definition at line 4875 of file svm.c.

◆ svm_vcpu_enter_exit()

|

static |

◆ svm_vcpu_free()

|

static |

◆ svm_vcpu_free_msrpm()

| void svm_vcpu_free_msrpm | ( | u32 * | msrpm | ) |

◆ svm_vcpu_init_msrpm()

| void svm_vcpu_init_msrpm | ( | struct kvm_vcpu * | vcpu, |

| u32 * | msrpm | ||

| ) |

◆ svm_vcpu_load()

|

static |

◆ svm_vcpu_pre_run()

|

static |

◆ svm_vcpu_put()

|

static |

Definition at line 1565 of file svm.c.

◆ svm_vcpu_reset()

|

static |

◆ svm_vcpu_run()

|

static |

Definition at line 4118 of file svm.c.

◆ svm_vm_destroy()

|

static |

◆ svm_vm_init()

◆ svm_write_tsc_multiplier()

| void svm_write_tsc_multiplier | ( | struct kvm_vcpu * | vcpu | ) |

◆ svm_write_tsc_offset()

|

static |

◆ sync_cr8_to_lapic()

|

inlinestatic |

◆ sync_lapic_to_cr8()

|

inlinestatic |

◆ task_switch_interception()

|

static |

Definition at line 2488 of file svm.c.

◆ ud_interception()

|

static |

◆ valid_msr_intercept()

|

static |

◆ vmload_interception()

|

static |

Definition at line 2286 of file svm.c.

◆ vmload_vmsave_interception()

|

static |

Definition at line 2252 of file svm.c.

◆ vmrun_interception()

|

static |

◆ vmsave_interception()

|

static |

Variable Documentation

◆ __initdata

◆ __read_mostly

◆ avic

◆ direct_access_msrs

|

static |

◆ dump_invalid_vmcb

| bool __read_mostly dump_invalid_vmcb |

◆ intercept_smi

◆ iopm_base

◆ lbrv

◆ msrpm_ranges

◆ nested

◆ npt_enabled

◆ nrips

◆ osvw_len

◆ osvw_status

◆ pause_filter_count

|

static |

◆ pause_filter_count_grow

|

static |

◆ pause_filter_count_max

|

static |

◆ pause_filter_count_shrink

|

static |

◆ pause_filter_thresh

|

static |

◆ rsm_ins_bytes

◆ svm_exit_handlers

|

static |

◆ svm_gp_erratum_intercept

◆ tsc_scaling

◆ vgif

◆ vls

◆ vnmi

◆ x86_intercept_map

|

static |